介绍Chiplet前,先说下SOC。Chiplet和SOC是两个相互对立的概念,刚好可以用来互为参照。

SOC (System On Chip,系统级芯片)——

是指将多个负责不同类型计算任务的单元,通过光刻的形式制作到同一片晶圆上。

目前主流智能手机的SOC芯片上,基本都集成了CPU、GPU、DSP、ISP、NPU、Modem等众多不同功能的计算单元,以及诸多的接口IP与SRAM。

SOC追求的是“高度的集成化”,利用先进制程对于所有的单元进行全面的提升。

Chiplet (也称作“芯粒”或者“小芯片”)——

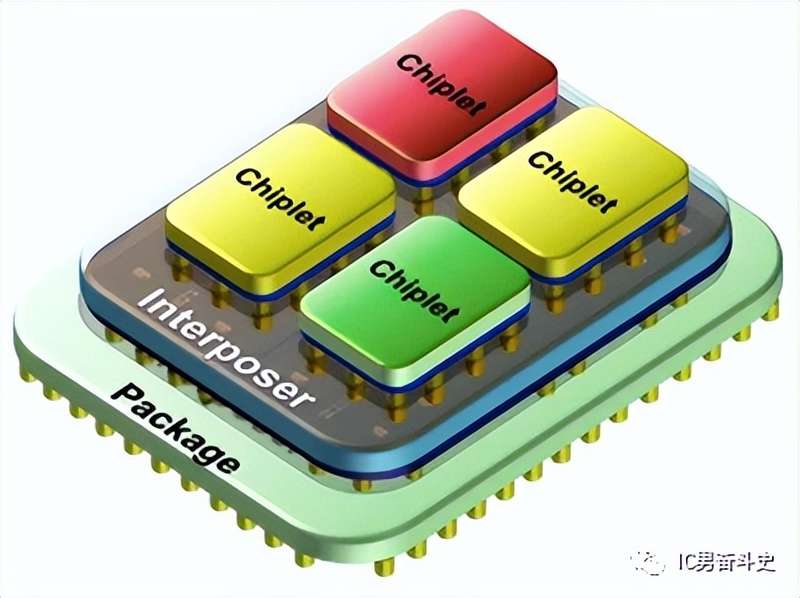

是指将一颗原本较为复杂的SOC芯片,从设计时就按照不同的功能单元进行分解,然后每个单元选择最适合的半导体制程工艺分别进行制造,再通过先进封装技术将各个单元彼此互联,就像搭“乐高积木”一样封装为一个系统级芯片组。

目前Chiplet封装技术已经在CPU、GPU、ASIC等高端芯片领域有所应用。随着摩尔定律接近极限,为了提高集成度,越来越多的复杂逻辑芯片会采用chiplet封装。

Chiplet封装支持每个功能单元使用不同的制程工艺,从而达到性能与成本的相对最优解。

晶圆制程工艺往3nm/2nm以下推进的难度突然飙升,几乎已经触碰到硅材料本身的物理极限;靠升级制程工艺来提升芯片性能的方法按照目前的科技能力已经无法再继续下去;通过先进封装技术(例如2.5D/3D/chiplet等)提升芯片性能并延续摩尔定律,已经逐步获得整个半导体产业界的认可。

台积电CoWoS 2.5D封装技术已经日趋成熟,成为高性能计算芯片的主要选择;全球前两大封装厂日月光和安靠科技在2.5D/3D封装领域也都建立了自己的技术路线,目前也有帮客户推出不同类型的产品;国内三大封测厂长电、通富和华天也都在先进封装领域积极布局,包括2.5D/3D等技术都取得了一定的发展。

3 AI应用对算力的巨大需求加速Chiplet技术发展

ChatGPT训练需要消耗3640PFLOPS-days AI算力,AIGC领域将引领新一轮的算力需求风暴;不论是从政府层面还是企业层面,数据中心和超算中心的持续建立都需要巨大的算力支持;随着自动驾驶技术的逐步落地,AI算力的需求还会进一步加剧。

4 美国芯片制裁政策推动Chiplet在国内的发展

2022年8月,美国政府针对3nm以下先进制程工艺使用的EDA软件实施出口限制;2022年9月,美国政府限制英伟达和AMD向中国出售高性能GPU芯片;2022年10月,美国政府出台政策限制台积电等全球芯片制造企业为中国加工制造高性能计算芯片。受限于美国制裁,国内AI芯片企业无法使用先进制程工艺迭代来提升算力,转而使用Chiplet等先进封装技术来实现算力的提升与新产品的研发。

当需要制造的芯片被拆成小模块分别制造,就可以各自使用最适合的制程工艺;这样单个模块的die size比较小,良率相对也会比较高;组合在一起后整体的产片良率也会比较高,比目前先进制程良率不足30%的大芯片节省了很多成本。

在芯片内部所包含的模块中,除了计算单元需要应用最先进的制程来达到良好的性能之外,其他模块例如存储、模拟、射频等则没有必要使用最先进的制程;比如存储模块在14nm、模拟在65/90nm节点会达到比先进工艺更好的性能;过往SOC芯片的设计中,所有模块都用同一个工艺节点制造,不仅会造成大量的浪费,而且也不是最优解。

如果按原来的设计模式,虽然自研或者外购的IP看似可以复用,但与其他模块的连接都需要重新设计,也需要重新再做测试,设计流程并没有简化;应用了Chiplet技术之后,芯粒在不同芯片之间可以重复使用,芯片设计流程变得简单灵活,芯片研发的成本将大幅降低。

研发一款复杂芯片时只需要把资源投入到核心模块上,其他功能模块可以使用成熟的“小芯片”,这样可以大幅缩短产品的研发周期。

由于Chiplet技术将复杂的电路拆解成一系列模块,然后再将不同的模块组装在一起,因此封装布线会变得非常复杂,这也成为使用Chiplet技术构建芯片的一个重要环节。

使用Chiplet将不同的“芯粒”拼接在一起后,最终组合成的芯片尺寸会比原本的SOC芯片封装尺寸大,相应的封装基板的尺寸也会更大;这样会增加基板的制造难度,降低基板的生产良率,从而增加封装成本。

Chiplet技术可以拆解数据处理器的复杂性,但是这需要在每个子模块之间添加一系列互联接口,以便所有模块之间进行数据交换,这些互联接口的设计比较复杂。

由于Chiplet技术使用不同制程工艺的模块组合在一起,相对于传统的单一制程工艺的SOC芯片,芯片可靠性方面的难度加大;芯片封装尺寸变大,对于封装可靠性的难度也会加大;这些将对系统的整体可靠性产生负面影响。

由于Chiplet技术的高度模块化,如果发生故障,就需要将故障点定位到某个具体的子模块。然后再去找子模块的供应商去分析具体的问题,反馈周期会比较长,相应的维护成本也会较高。