FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是器件的标配了。从PCI发展到PCI-E,从ATA发展到SATA,从并行ADC接口到JESD204,从RIO到Serial RIO……等等,都是在借助SerDes来提高数据传输的性能。SerDes是非常复杂的数模混合设计,用户手册的内容只是描述了相对粗略的概念以及使用方法,并不能完全解释SerDes是怎么工作的。在使用SerDes的过程中,设计者有太多的疑惑:为什么在传输的过程中没有时钟信号?什么是加重和均衡?抖动和误码是什么关系?各种抖动之间有什么关系?时钟怎么恢复?等等这些问题,如果设计者能够完全理解这些问题,那么对于SerDes的开发也不再是难事。本文试着从一个SerDes用户的角度来理解SerDes是怎么设计的。

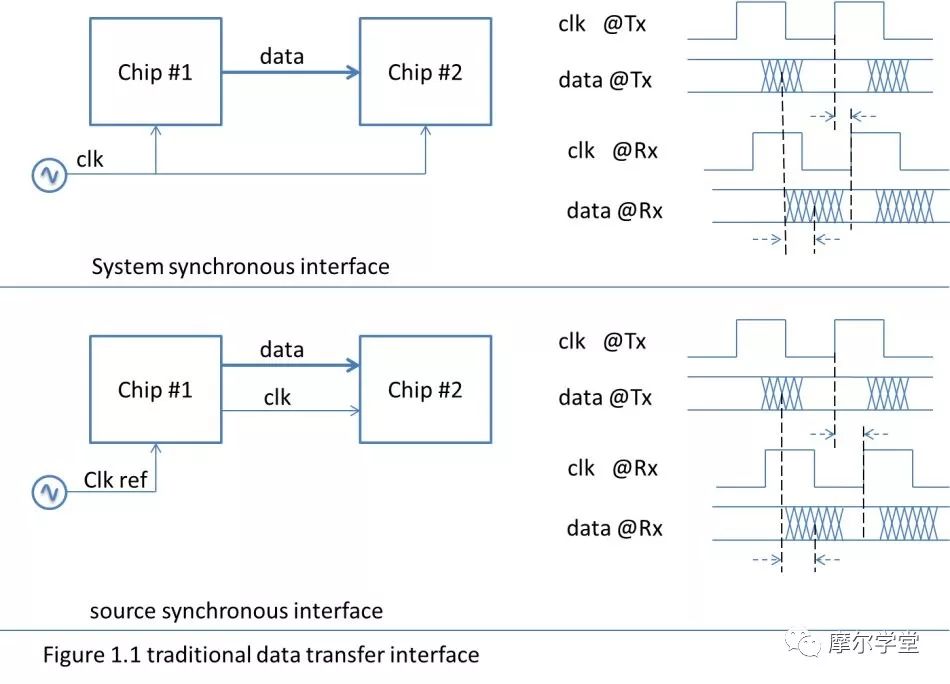

在芯片之间的数据传输,最早的时候是以串行传输的方式完成的,但随着数据量的越来越大,串行数据传输的缺点变得特别明显:速率太低。所以芯片设计者就想着增加数据传输的位宽,用并行的方式传输数据,这样相对于串行传输就有更高的传输速率。芯片之间的互联通古系统同步或者源同步的并行接口传输数据。图1.1演示了系统同步和源同步并行接口。

随着接口频率的提高,在系统同步接口方式中,有几个因素限制了有效数据串口宽度的继续增加。

时钟到达两个芯片的传播延时不相等(clock skew)

并行数据各个bit的传播延时博相等 (data skew)

时钟的传播延时和数据的传播延时不一致(skew between data and clock)

虽然可以通过在目的芯片(chip #2)内使用PLL补偿时钟延时差(clock skew),但是PVT(Process Verification Test)变化时,时钟沿是的变化量和数据延时的变化量是不一样的。这又进一步恶化了数据窗口,即无法通过简单的、不断增加的数据总线数达到增加数据传输速率的目的。

源同步接口方式中,发送端Tx把时钟伴随数据一起发送出去,限制了clock skew对有效数据窗口的危害。通常在发送测芯片内部,源同步接口把时钟信号和数据信号当作一样来处理,也就是让它和数据信号经过相同的路径,以保证相同的延时。这样PVT变化时,时钟和数据会朝着同一个方向增大或者减小相同的量,对skew最有利。

我们来做一些合理的典型假设,假设一个32bit数据的并行总线:

发送端的数据skew = 50 ps (很高的要求)

PCB总线引入的skew = 50 ps (很高的要求)

时钟的周期抖动jitter = +/- 50 ps (很高的要求)

接收端触发器采样窗口 = 250 ps (Xilinx V7 高端器件的IO触发器)

可以大致估算出并行接口的最高时钟 = 1/(50+50+100+250) = 2.2GHz (DDR)或者1.1GHz(SDR).

利用源同步接口,数据的有效窗口可以提高很多,通常频率都是在1GHz以下。在实际使用中可以见到如SPI4.2接口的时钟可以高达DDR 700HNz * 16 bits位宽。DDR Memory接口也是一种源同步接口,如DDR3在FPGA中可以做到大约800MHz的时钟(DDR)。

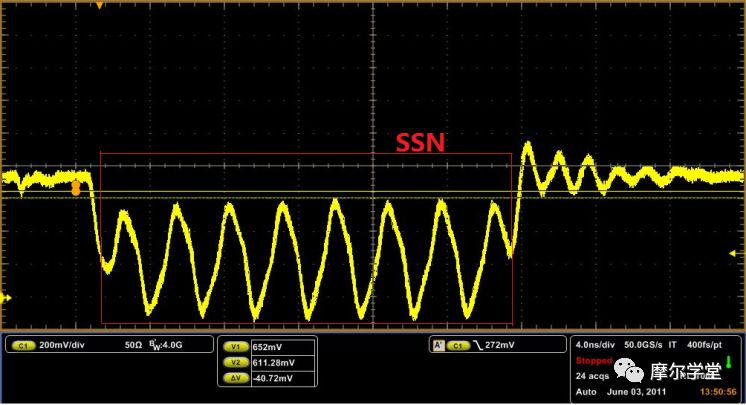

要提高接口的传输带宽有两种方法:一种是提高时钟频率;一种是加大数据位宽。那么数据位宽是不是可以无限制地加大呢?这就要牵扯到另外一个非常重要的问题----同步切换噪声(SSN)。

SSN的计算公式:SSN = L * N * di/dt

L是芯片封装电感,N是数据位宽,di/dt是电流变化的斜率。随着频率的提高,数据位宽的增加,SSN成为提高传输带宽的主要瓶颈。图1.2是一个DDR3串扰的例子。途中低电平的理论值在0V,由于SSN的影响,低电平表现为震荡,震荡噪声的最大值达610mv,因此噪声余量只有1.5V/2 - 610mV = 140mV。

因此也不可能靠无限地提高数据位宽来继续增加带宽。一种解决SSN的办法是使用差分信号替代单端信号,使用差分信号可以很好地解决SSN的问题,代价是使用更多的芯片引脚。使用差分信号仍然解决不了数据skew的问题,很大位宽的差分信号再加上严格的时序限制,给并行接口带来了很大的挑战。

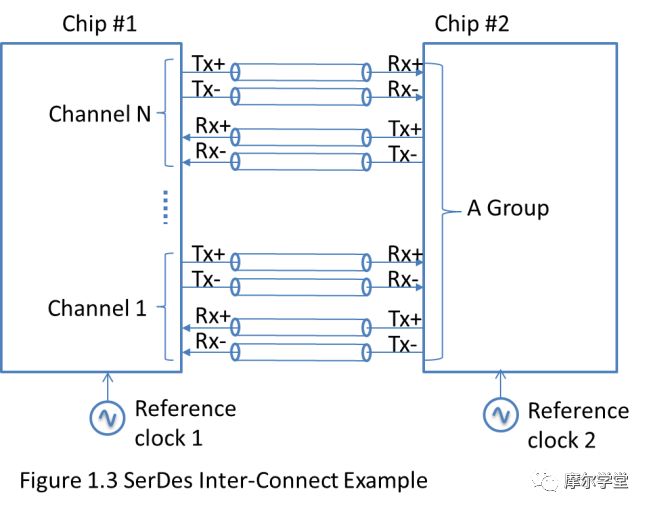

源同步接口的时钟频率已经遇到瓶颈,由于信道(channel)的非理想特性,在继续提高频率,信号会被严重损伤,这就需要采用均衡和数据时钟相位检测等技术。这也就是SerDes所采用的技术。SerDes是串行器和解串器的简称。串行器也成为SerDes发送端(Tx),解串器也成为接收端(Rx)。图1.3是一个N对SerDes收发通道的互连演示,一般N小于4.

可以看到,SerDes不传送时钟信号,这也是SerDes最特别的地方,SerDes在接收端集成了CDR(Clock Data Recovery)电路,利用CDR从数据的边沿信息中抽取时钟,并找到最优的采样位置。

SerDes采用差分方式传送数据。一般会有多个通道的数据放在一个group中以共享PLL资源,每个通道仍然是相互独立工作的。

SerDes需要参考时钟(Reference Clock),一般也是差分的形式以降低噪声。接口端Rx和发送端Tx的参考时钟可以允许几百个ppm的频差(plesio-synchronous system),也可以是同频的时钟,但是对相位差没有要求。

做个简单的比较,一个SerDes通道(Channel)使用4个引脚(Tx+/-, Rx+/-),目前的FPGA可以做到高达28Gbps。而一个16bit的DDR3-1600的线速率为1.6Gbps*16 = 25Gbps,却需要50多个引脚。这样对比之下可以看出SerDes在传输带宽上的优势。

相比于源同步接口,SerDes的主要特点包括:

SerDes在数据线中时钟内嵌,不需要传送时钟信号。

SerDes通过加重/均衡技术可以实现高速长距离传输,如背板。

SerDes使用了较少的芯片引脚。

也存在一些介于SerDes和并行接口之间的接口类型,相对源同步接口而言,这些中间类型的接口也使用串行器和解串器,同时也传送用于同步的时钟信号。这类接口如视频显示接口7:1 LVDS等。

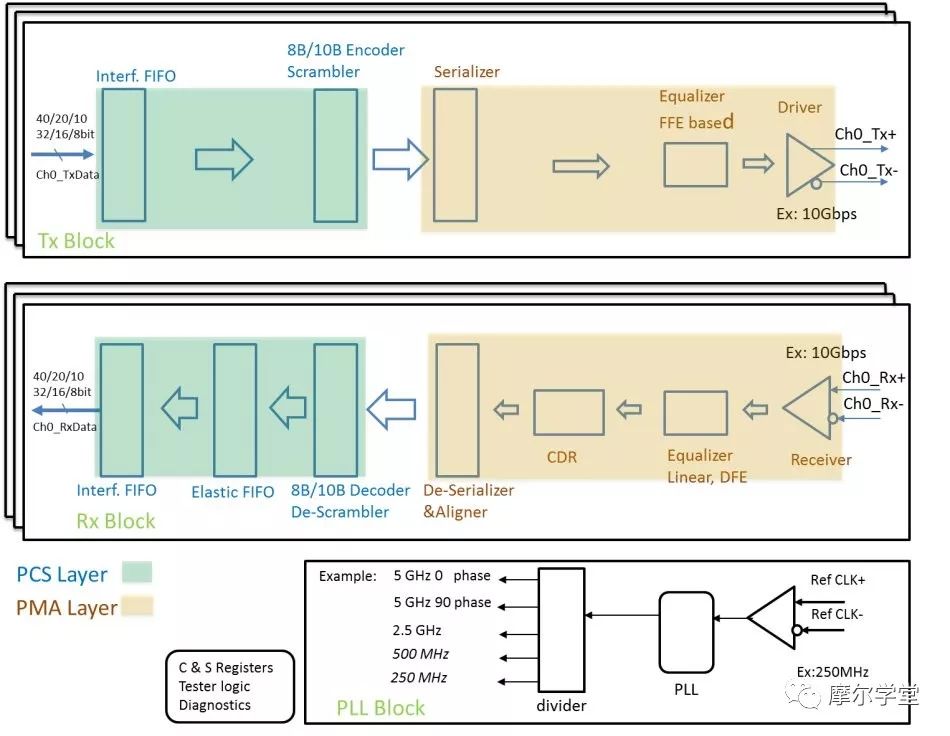

SerDes的主要构成可以分为三部分:PLL模块,发送模块Tx,接收模块Rx。为了方便维护和测试,还会包括控制和状态寄存器,换回测试,PRBS测试等功能。如图2.1

图中蓝色背景子模块为PCS层,是标准的可综合CMOS数字逻辑,可以使用硬件逻辑实现,也可以使用FPGA软逻辑实现,相对容易理解。褐色背景的子模块是PMA层,是数模混合CML/CMOS电路,是理解SerDes区别于并行接口的关键,也是本文讨论的重点内容。

发送方显(Tx)信号的流向:FPGA逻辑(Fabric)发送过来的并行信号,通过接口FIFO(Interface FIFO),发送到 8B/10B编码器(8B/10B encoder)或扰码器(scambler),以避免数据含有较多的0或者较多的1。之后送给串行器(Serializer)进行并串转换。串行数据警告过均衡器(equalizer)调理,由驱动器(driver)发送出去。

接收方向(Rx)信号的流向,外部串行信号由线性均衡器(Linear Equalizer)或者DFE(Decision Feedback Equalizer)结构均衡器条例,去除一部分确定性抖动(Deterministic jitter).CDR从数据中恢复出来采样时钟,经解串器变为对齐的并行信号。8B/10B解码器(8B/10B decoder)或解扰其(de-scambler)完成解码或者解扰。如果是异步时钟系统(Plesio-synchronous system),在用户FIFO之前还应该有弹性FIFO来补偿频差。

PLL负责产生SerDes各个模块所需要的时钟信号,并管理这些时钟之间的相位关系。以图中线速率10Gbps为例,参考时钟频率250MHz。Serializer/Deserializer至少需要5GHz 0相位时钟和5GHz 0相位时钟和5GHz 90度相位时钟,1GHz(10bit并行)/1.25GHz(8bit并行)时钟等。

一个SerDes通常还需要调试能力,例如伪随机码刘产生和比对,各种环回测试,控制状态寄存器以及访问接口,LOS检测,沿途测试等。

串行器(Serializer)把并行信号转化为串行信号,解串器(Deserializer)把串行信号转化为并行信号,一般地,并行信号为8/10bit或者16/20bit宽度,串行信号为1bit宽度(也可以分阶段串行化,如8bit->4bit->2bit->1bit以降低equalizer的工作频率)。采用扰码(scrambled)的协议和SDH/SONET,SMPTE SDI使用8/16bit的并行宽度,如PCI-Express采用8B/10B编码的协议,GbE使用10bits/20bits宽度。

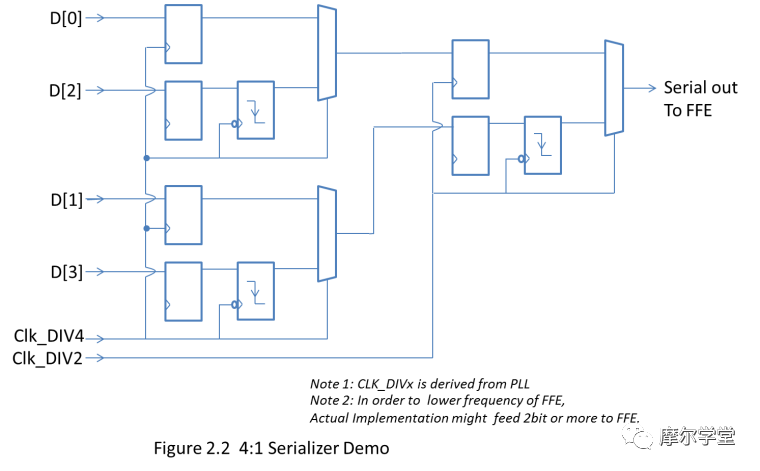

一个4:1的串行器图下图2.2所示.8:1或16:1的串行器采用类似的方法实现。在实现时,为了降低均衡器的工作频率,串行器会先把并行数据变为2bit,送给均衡器滤波,最后一步再做2:1串行化。

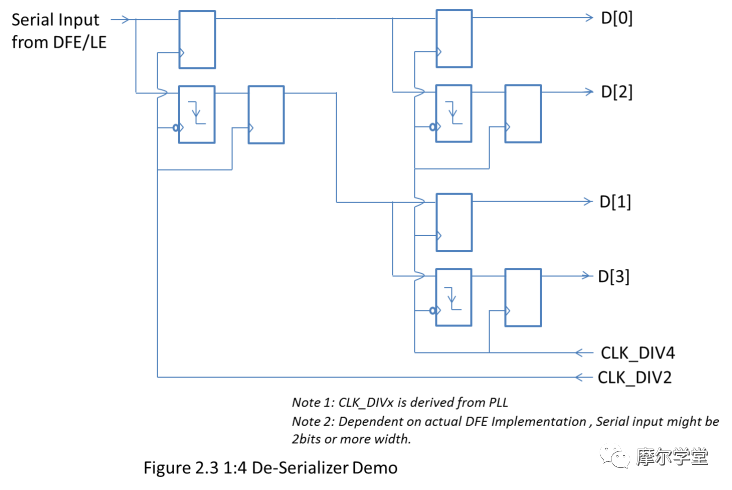

一个1:4的解串器如图2.3所示,8:1或16:1的解串器采用类似的实现。实现时,为了降低均衡器的工作频率,均衡器工作在DDR模式下,解串器的输入是2bit或者更宽。

串行器解串器的实现采用双沿DDR的工作方式,利用面积换速度的策略,降低了电路中高频率电路的比例,从而降低了电路的噪声。

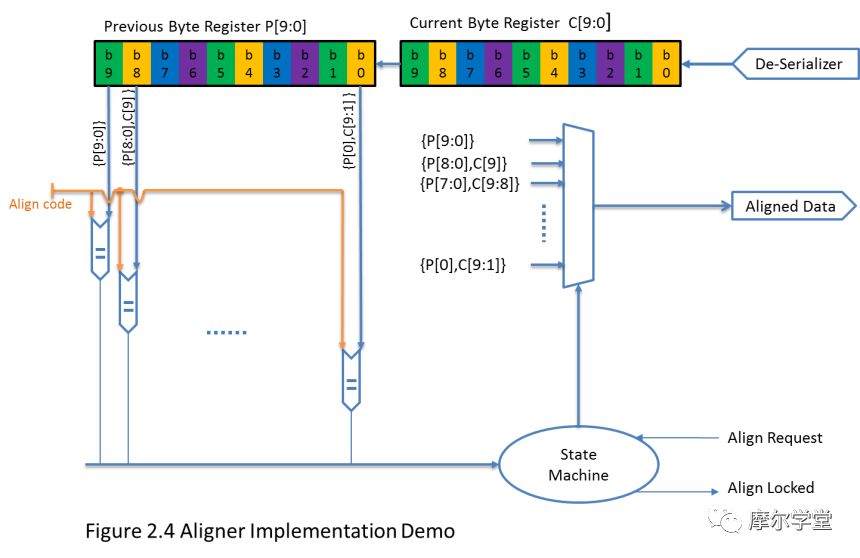

接收方向除了解串器以外,一般还有对齐功能逻辑(Aligner)。相对SerDes发送端,SerDes接收端起始工作的时刻是任意的,接收器正确收到的第一个bit可能是发送并行数据的任意bit位置。因此需要对齐逻辑来判断从什么bit位置开始,以组成正确的并行逻辑。对齐逻辑通过在串行数据流中搜索特征码字(Alignment Code)来决定串并转换的起始位置。比如8B/10B编码的协议通常用K28.5(正码10‘b1110000011,负码:10’b0001111100)来作为对齐字。图2.4为一个对齐逻辑的演示。通过滑窗,逐bit比对,比找到对起码(Align-Code)的位置,经过多次在相同的位置找到对起码之后,状态机锁定位置并选择相应的位置输出对齐数据。

SerDes信号从发送芯片到达接收芯片所经过的路径成为信道(Channel),包括芯片封装,PCB总线,过孔,电缆,连接器等元件。从频域上看,信道可以简化为一个低通滤波器(LPF)模型,如果SerDes的速率大于信道(channel)的截止频率,就会一定程度上损伤信号。均衡器的作用就是不让信道对信号的损伤。

发送端的均衡器采用FFE(Feed Forward Equalizers)结构,发送端的equalizer也称作加重器(emphasis).加重分为去加重(de-emphasis)和预加重(pre-emphasis)。de-emphasis降低差分信号的摆幅(swing).Pre-emphasis增加差分信号的摆幅。FPGA大部分使用de-emphasis的方式,加重越强,信号的平均幅度就越小。

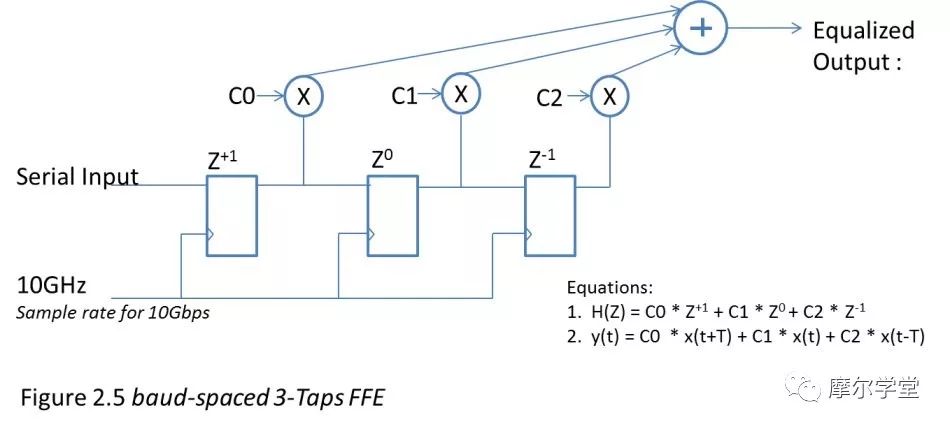

发送测均衡器设计为一个高通滤波器(HPF),大致为信道频响H(f)的反函数,FFE(Feed Forward Equalization 前行反馈均衡)的目标是让到达接收端的信号为一个干净的信号,FFE的实现方式有很多,典型的例子如下图2.5所示:

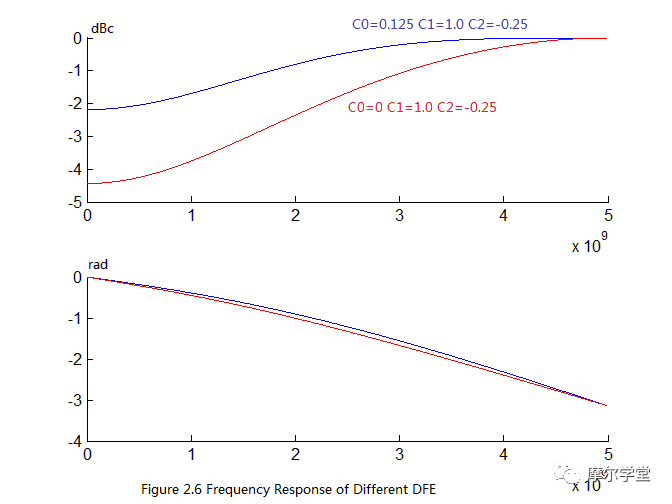

调节滤波器的系数可以改变滤波器的频响,以补偿不同的信道特性,一般可以动态配置。以10Gbps线速率为例,图2.6为DFE频率响应演示,可以看到对于C0 = 0, C1 = 1, C2 = -0.25的配置,5GHz处高频增益比低频区域高出4dB,从而补偿信道对高频频谱的衰减。

采样时钟的频率限制了这种FFE,最高只能补偿到Fs/2(上例中Fs/2 = 5GHz)。根据采样定理,串行数据里的信息都包含在5GHz以内,从这个角度看也就足够了。如果要补偿Fs/2以上的频率,就要求DDE高于Fs的工作频率,或者连续时间域滤波器(Continuous Time FFE).

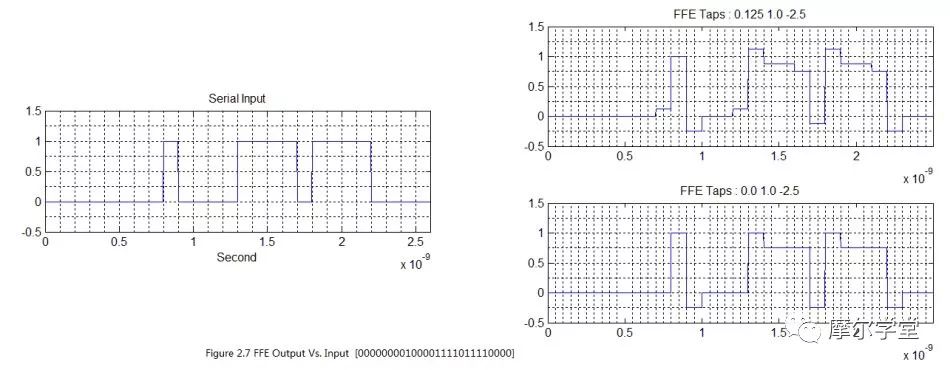

图2.7为DFE时序滤波效果的演示,以10Gbps线速率为例,一个UI = 0.1 ns = 100 ps.演示的串行数据码流为二进制[00000000100001111011110000].

11月09日-10日将在上海举办一期SerDes课程,本期短期课程旨在通过提供 SerDes 空间所需的系统级和电路级概念来弥补这些差距。课程将从传统的模拟架构开始,逐步发展到今天基于 DSP 的均衡和定时恢复。本课程从传统的模拟混合信号 SerDes 架构开始,该架构如今仍适用于 UCI、HBM 和 XSR 解决方案。之后,我们将转向 ADC-DSP 解决方案。

--点击图片即转至课程页面

今天小编带来了:ISSCC2023套餐,里面有文章、Short Course、PPT、Tutorial等,同学可以拿回去自己学习研究。

1、深入理解SerDes(Serializer-Deserializer)之一

2、深入理解SerDes(Serializer-Deserializer)之二

3、科普:深入理解SerDes(Serializer-Deserializer)之三

4、资深工程师的ESD设计经验分享

5、干货分享,ESD防护方法及设计要点!

6、科普来了,一篇看懂ESD(静电保护)原理和设计!

7、锁相环(PLL)基本原理 及常见构建模块

8、当锁相环无法锁定时,该怎么处理的呢?

9、高性能FPGA中的高速SERDES接口

10、什么是毫米波技术?它与其他低频技术相比有何特点?

11、如何根据数据表规格算出锁相环(PLL)中的相位噪声

12、了解模数转换器(ADC):解密分辨率和采样率

13、究竟什么是锁相环(PLL)

14、如何模拟一个锁相环

15、了解锁相环(PLL)瞬态响应

16、如何优化锁相环(PLL)的瞬态响应

17、如何设计和仿真一个优化的锁相环

18、锁相环(PLL) 倍频:瞬态响应和频率合成

19、了解SAR ADC

20、了解 Delta-Sigma ADC

21、什么是数字 IC 设计?

22、什么是模拟 IC 设计?

23、什么是射频集成电路设计?

24、学习射频设计:选择合适的射频收发器 IC

25、连续时间 Sigma-Delta ADC:“无混叠”ADC

26、了解电压基准 IC 的噪声性能

27、数字还是模拟?I和Q的合并和分离应该怎么做?

28、良好通信链路性能的要求:IQ 调制和解调

29、如何为系统仿真建模数据转换器?

30、干货!CMOS射频集成电路设计经典讲义(Prof. Thomas Lee)

31、使用有效位数 (ENOB) 对 ADC 进行建模

32、以太网供电 (PoE) 的保护建议

33、保护高速接口的设计技巧

34、保护低速接口和电源电路设计技巧

35、使用互调多项式和有效位数对 ADC 进行建模

36、向 ADC 模型和 DAC 建模添加低通滤波器

37、揭秘芯片的内部设计原理和结构

38、Delta-Sigma ADCs中的噪声简介(一)

39、Delta-Sigma ADCs中的噪声简介(二)

40、Delta-Sigma ADCs 中的噪声简介(三)

41、了解Delta-Sigma ADCs 中的有效噪声带宽(一)

42、了解Delta-Sigma ADCs 中的有效噪声带宽(二)

43、放大器噪声对 Delta-Sigma ADCs 的影响(一)

44、放大器噪声对 Delta-Sigma ADCs 的影响(二)

45、参考电压噪声如何影响 Delta Sigma ADCs

46、如何在高分辨率Delta-Sigma ADCs电路中降低参考噪声

47、时钟信号如何影响精密ADC

48、了解电源噪声如何影响 Delta-Sigma ADCs

49、运算放大器简介和特性

50、使用 Delta-Sigma ADCs 降低电源噪声的影响

51、如何设计带有运算放大器的精密电流泵

52、锁定放大器的基本原理

53、了解锁定放大器的类型和相关的噪声源

54、用于降低差分 ADC 驱动器谐波失真的 PCB 布局技术

55、干货!《实用的RFIC技术》课程讲义

56、如何在您的下一个 PCB 设计中消除反射噪声

57、硅谷“八叛徒”与仙童半导体(Fairchild)的故事!

58、帮助你了解 SerDes!

1、免费公开课:ISCAS 2015 :The Future of Radios_ Behzad Razavi

2、免费公开课:从 5 微米到 5 纳米的模拟 CMOS(Willy Sansen)

3、免费公开课:变革性射频毫米波电路(Harish Krishnaswamy)

4、免费公开课:ESSCIRC2019-讲座-Low-Power SAR ADCs

5、免费公开课:ESSCIRC2019-讲座-超低功耗接收器(Ultra-Low-Power Receivers)

6、免费公开课:CICC2019-基于 ADC 的有线收发器(Yohan Frans Xilinx)

7、免费公开课:ESSCIRC 2019-有线与数据转换器应用中的抖动

8、免费公开课:ISSCC2021 -锁相环简介-Behzad Razavi

9、免费公开课:ISSCC2020-DC-DC 转换器的模拟构建块

10、免费公开课:ISSCC2020-小数N分频数字锁相环设计

11、免费公开课:ISSCC2020-无线收发器电路和架构的基础知识(从 2G 到 5G)

12、免费公开课:ISSCC2020-从原理到应用的集成变压器基础

13、免费公开课:ISSCC2021-射频和毫米波功率放大器设计的基础

14、免费公开课:ISSCC 2022-高速/高性能数据转换器系列1(Prof. Boris Murmann)

15、免费公开课:ISSCC 2022-高速/高性能数据转换器系列2(Dr. Gabriele Manganaro)

16、免费公开课:ISSCC 2022-高速/高性能数据转换器系列3(Prof. Pieter Harpe)

17、免费公开课:ISSCC 2022-高速/高性能数据转换器系列4(Prof. Nan Sun)

点击下方“公众号”,关注更多精彩

半导体人才招聘服务平台