使用碳化硅 (SiC),肖特基二极管可以在功率转换应用中比硅 (Si) P/N 二极管提高效率和性能。在本文中,我们将重点介绍Nexperia新推出的 PSC1065K SiC 650V 肖特基二极管的一些特性和性能。SiC肖特基二极管的优点

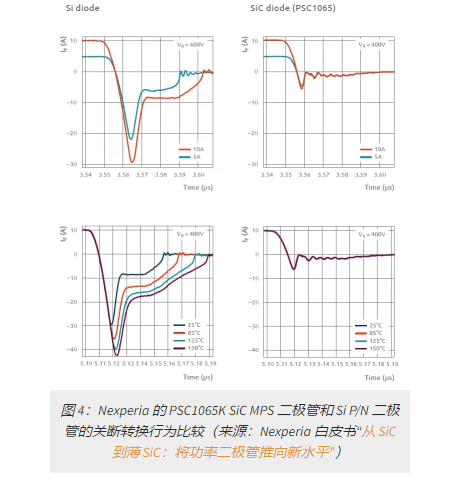

- 由于是单极,肖特基二极管在反向偏置转换时不会遭受存储电荷 (Q rr ) 耗散的影响。P/N 二极管将这种反向恢复效应表现为反向电流 (I rr )中的尖峰,这会导致更高的功率损耗,不仅会导致二极管关断,还会导致在导通时必须承载此 I rr电流的互补器件产生更高的功率损耗导通,导致导通损耗增加 E ON。相反,肖特基二极管只需要放电其自电容。

相关电荷可能比 P/N 二极管中的 Qrr 小一个数量级。例如,在升压转换器中,这种反向恢复损耗可能是主要损耗。P/N 二极管的反向恢复损耗通常随着开关频率的增加而增加,从而增加了肖特基二极管在压摆率超过 100 kV/us 和几 kA/us 的高要求应用中的优势。P/N 二极管反向恢复行为的另一个缺点是其温度依赖性,这使得电路优化变得困难。SiC 肖特基二极管不会表现出这种反向恢复随温度变化的情况。 - SiC 肖特基二极管在正常应用电流驱动范围内对正向压降表现出正温度系数 (PTC)。这使得它们更容易并联,因为PTC可以实现电流的自然平衡并防止热失控。另一方面,Si P/N 二极管具有负温度系数,需要在并联操作下降额或使用额外电路来强制均流。

肖特基二极管中的 PTC 确实会增加高温下的传导损耗。然而,动态损耗的优势通常会过度补偿这一点。 - 由于 SiC 肖特基二极管具有软关断和电容关断行为,因此可以大大减少开关干扰。EMI滤波器通常在处理 P/N 二极管产生的高频传导和辐射发射时效果较差。

SiC 二极管的软恢复行为的另一个好处是,它在关断转换期间引起的电压过冲较小。这种反向恢复电压尖峰有时会超过额定电压并导致可靠性问题。虽然快速恢复硅二极管可以在其两端添加缓冲器来限制边沿速率和阻尼振荡,但这些添加的器件会消耗能量,影响整体系统效率。 - 肖特基二极管的较低损耗意味着在需要较少冷却的更小、更轻的模块中具有更高的功率密度。

合并式 PiN (MPS) 肖特基二极管

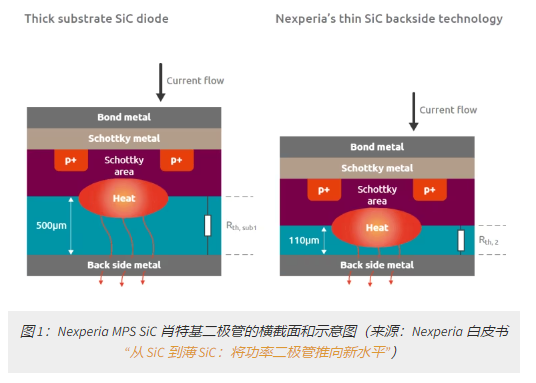

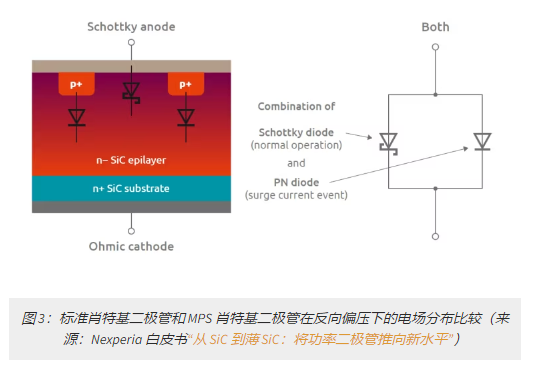

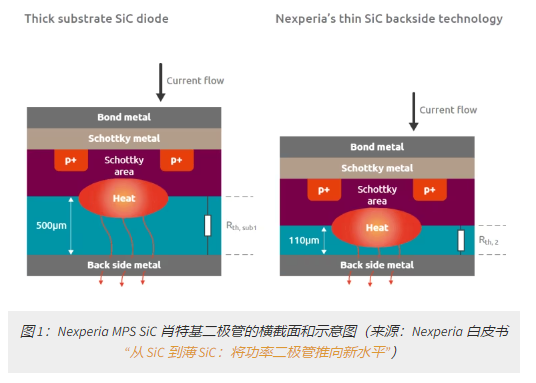

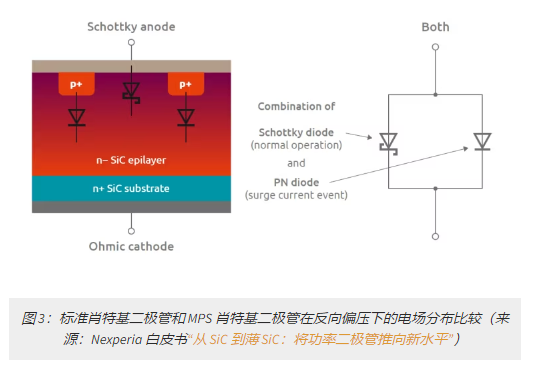

肖特基二极管单极传导的缺点之一是与 Si P/N 二极管相比,其浪涌电流额定值较低。较低电阻的漂移区有助于降低正向压降,但代价是关断状态下的漏电流较高。Nexperia 采用的 MPS 结构如图 1 所示,提高了浪涌性能,同时降低了漏电流。MPS 结构有效地将 PN 二极管与肖特基二极管并联。一旦其导通电压达到浪涌电流水平,P/N 二极管就开始以较低的差分电阻导通。正常情况下,P/N二极管不被触发,肖特基二极管占主导地位。在这些条件下,二极管的行为几乎完全类似于肖特基,这具有所描述的反向恢复优势。

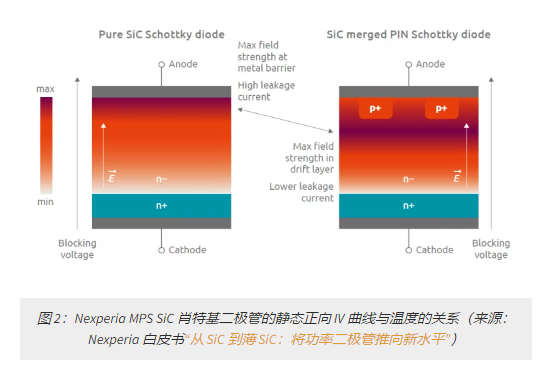

Nexperia 的 MPS 肖特基二极管的静态 IV 正向 IV 曲线如图 2 所示。PSC1065K 二极管在 150 ℃、10 ms 半正弦波脉冲条件下具有额定正向电流 I F = 10A 和浪涌电流额定值 I FSM共 42 个。

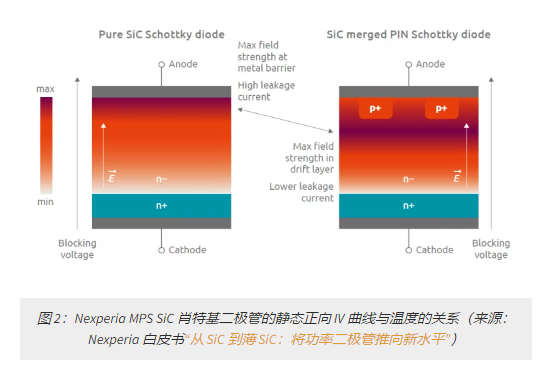

如图 3 所示,使用 p 区还可以有效地将反向偏压下的最大电场区域推离阳极接触,其中金属-半导体界面处的缺陷会产生高漏电流。因此,对于给定的击穿电压,MPS 器件可以在具有相同漏电流和漂移层厚度的情况下以更高的击穿电压工作,或者以更低的漂移电阻(因此,在工作和浪涌电流水平下,正向电压随温度的增加更低)。

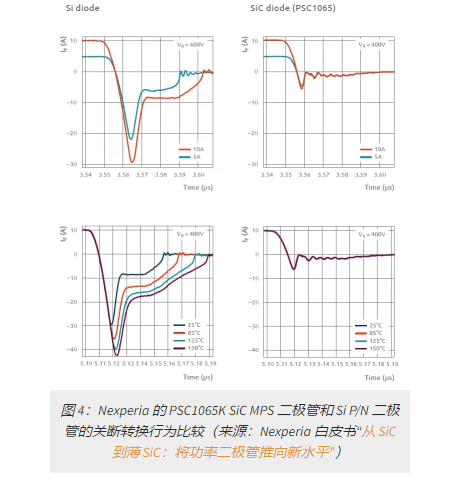

图 4 描述了 SiC MPS 二极管在关断转换下的优点。与此处所示的 Si P/N 二极管响应相比,PSC1065K 具有快速、对温度和电流不敏感的恢复能力。

PSC 结构中 p 阱区域的尺寸和掺杂在正向压降和浪涌能力之间进行权衡;该选择可以是特定于应用程序的。

薄碳化硅二极管

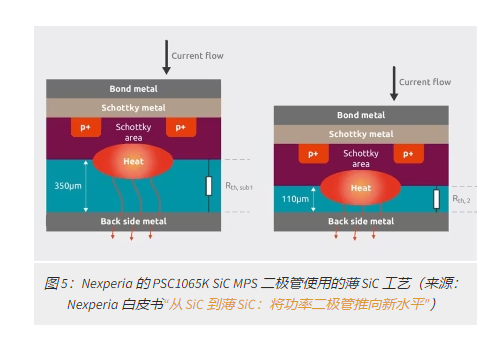

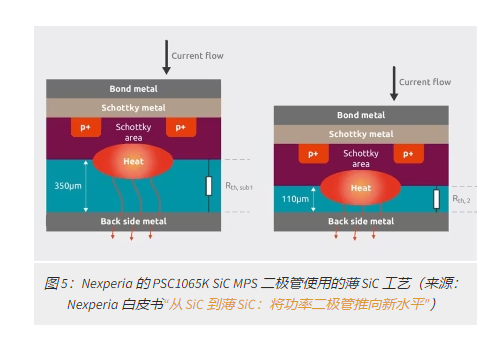

SiC 的标准衬底厚度范围为 350 µm 至 500 µm。该区域增加了器件的电阻和热阻。基材减薄可以帮助减少这种影响。由于 SiC 的硬度以及确保均匀、精密研磨的需要,这需要先进的制造能力。

如图 5 所示,Nexperia 的“薄 SiC”工艺流程将原始基板厚度减少了约三分之一。这极大地降低了热阻,从而实现更低的工作温度、更高的可靠性、使用寿命、浪涌电流能力和更低的正向压降。热阻的降低相当于给定外壳温度下功耗能力的增加。然而,应用中需要考虑由于减薄而导致热容的降低。

结论

当与 IGBT 或 SiC MOSFET 结合使用时,SiC 肖特基二极管可在独立和续流应用中实现快速、低损耗的开关。更高的功率密度和/或更简单的冷却、更少的 EMI 以及更低的系统复杂性和成本节省是它们可以带来的一些系统级优势。Nexperia 的 PSC1065 系列 650V、10A MPS 薄型 SiC 肖特基二极管有多种封装选项,包括 TO-220-2、TO-247-2、通孔以及 DPAK 和 D2PAK 表面贴装选项。未来的路线图还包括 1200V 和 20A 设备额定值。

本文作者:Sonu Daryanani 博士。1993 年在英国布拉德福德大学获得电子工程博士学位,同时在新泽西州 AT&T 贝尔实验室进行砷化镓光电子学研究。在过去 25 年里,他是亚利桑那州 Microchip Technology 的设备/工艺集成工程师,从事微控制器和分立器件方面的工作。

*免责声明:本文由作者原创。文章内容系作者个人观点,InSemi转载仅为了传达观点,仅代表InSemi对该观点赞同或支持,如果有任何异议,欢迎InSemi。