----与智者为伍 为创新赋能----

扇出型晶圆级封装技术采取在芯片尺寸以外的区域做I/O接点的布线设计,提高I/O接点数量。采用RDL工艺让芯片可以使用的布线区域增加,充分利用到芯片的有效面积,达到降低成本的目的。扇出型封装技术完成芯片锡球连接后,不需要使用封装载板便可直接焊接在印刷线路板上,这样可以缩短信号传输距离,提高电学性能。

扇出型晶圆级封装技术的优势在于能够利用高密度布线制造工艺,形成功率损耗更低、功能性更强的芯片封装结构,让系统级封装(System in a Package, SiP)和3D芯片封装更愿意采用扇出型晶圆级封装工艺。

第一代FOWLP技术是由德国英飞凌(Infineon)开发的嵌入式晶圆级球栅阵列(Embedded Wafer Level Ball Grid Array, eWLB)技术(见图1),随后出现了台积电(TSMC)的整合式扇出型晶圆级封装(Integrated Fan-Out Package, InFO)技术和飞思卡尔(Freescale)的重分布芯片封装(Redistributed Chip Package, RCP)技术等。由于其成本相对较低,功能性强大,所以逐步被市场接受,例如苹果公司(Apple)已经在A12处理器采用扇出型封装进行量产。同时其不仅在无线领域发展迅速,现在也正渗透进汽车和医疗应用,相信未来我们生活中的大部分设备都会采用扇出型晶圆级封装工艺。

图1 英飞凌eWLB工艺技术示例图

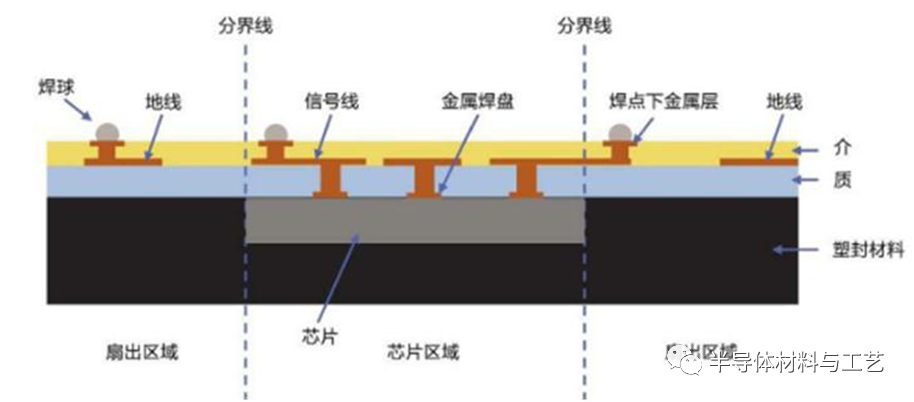

传统的封装技术如倒装封装、引线键合等,其信号互连线的形式包括引线、通孔、锡球等复杂的互连结构。这些复杂的互连结构会影响芯片信号传输的性能。在扇出型封装中(见图2),根据重布线的工序顺序,主要分为先芯片(Chip first)和后芯片(Chip last)两种工艺,根据芯片的放置方式,主要分为面朝上(Face up)和面朝下(Face down)两种工艺,综合上述四种工艺,封装厂根据操作的便利性,综合出以下三种组合工艺,分别是面朝上的先芯片处理(Chip first-face up)、面朝下的先芯片处理(Chip first-face down)和面朝下的后芯片处理(Chip last-face down)。接下来分别对这三种工艺进行阐述。

图2 FOWLP工艺互连结构示意图

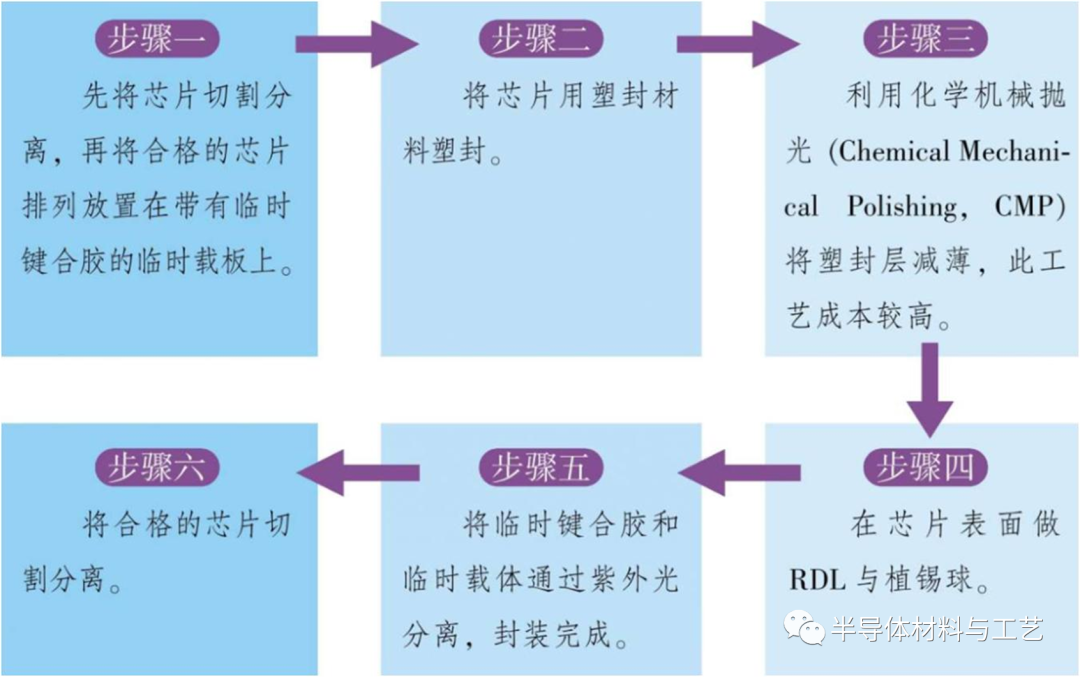

1、面朝上的先芯片处理。

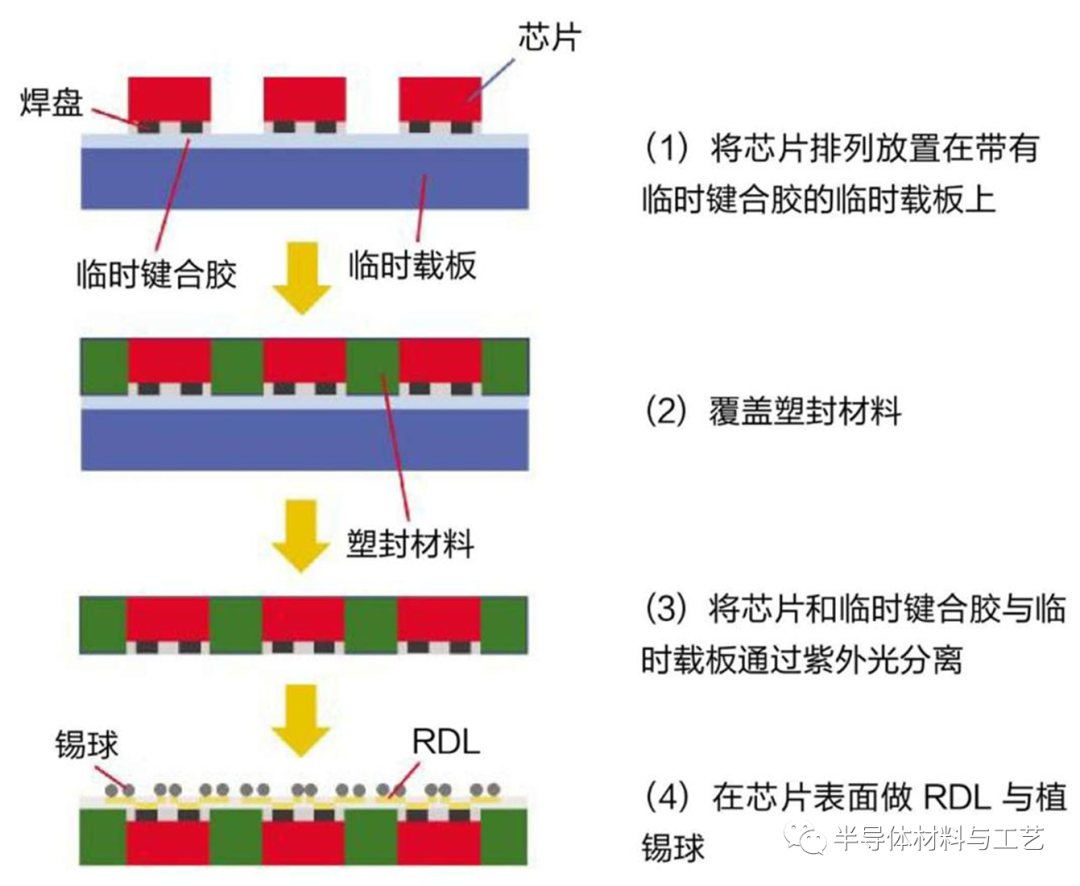

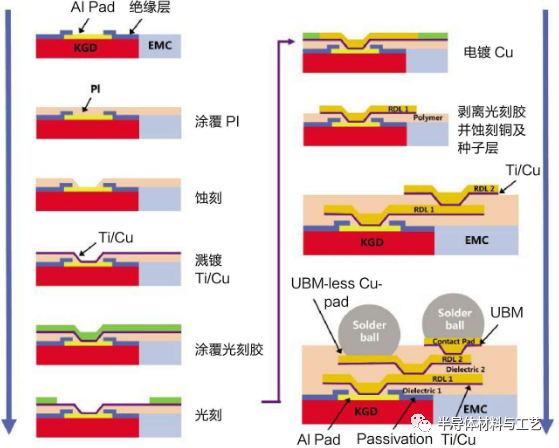

面朝上是让芯片的线路面朝上,采用RDL工艺的方式构建凸块,让I/O接触点连接,最后切割单元芯片。(见图3)

图3 面朝上的先芯片处理工艺示意图

面朝上的先芯片处理工艺流程如下:

2、面朝下的先芯片处理。

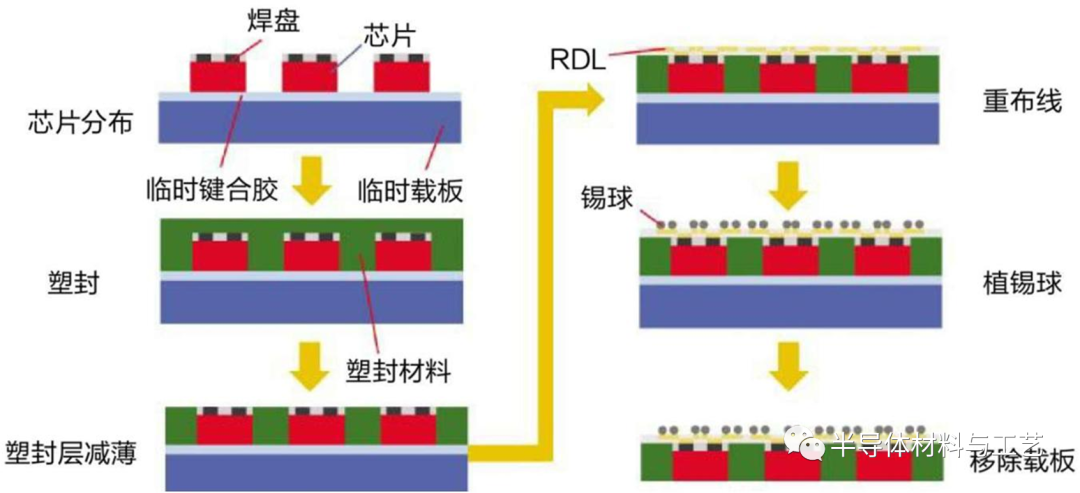

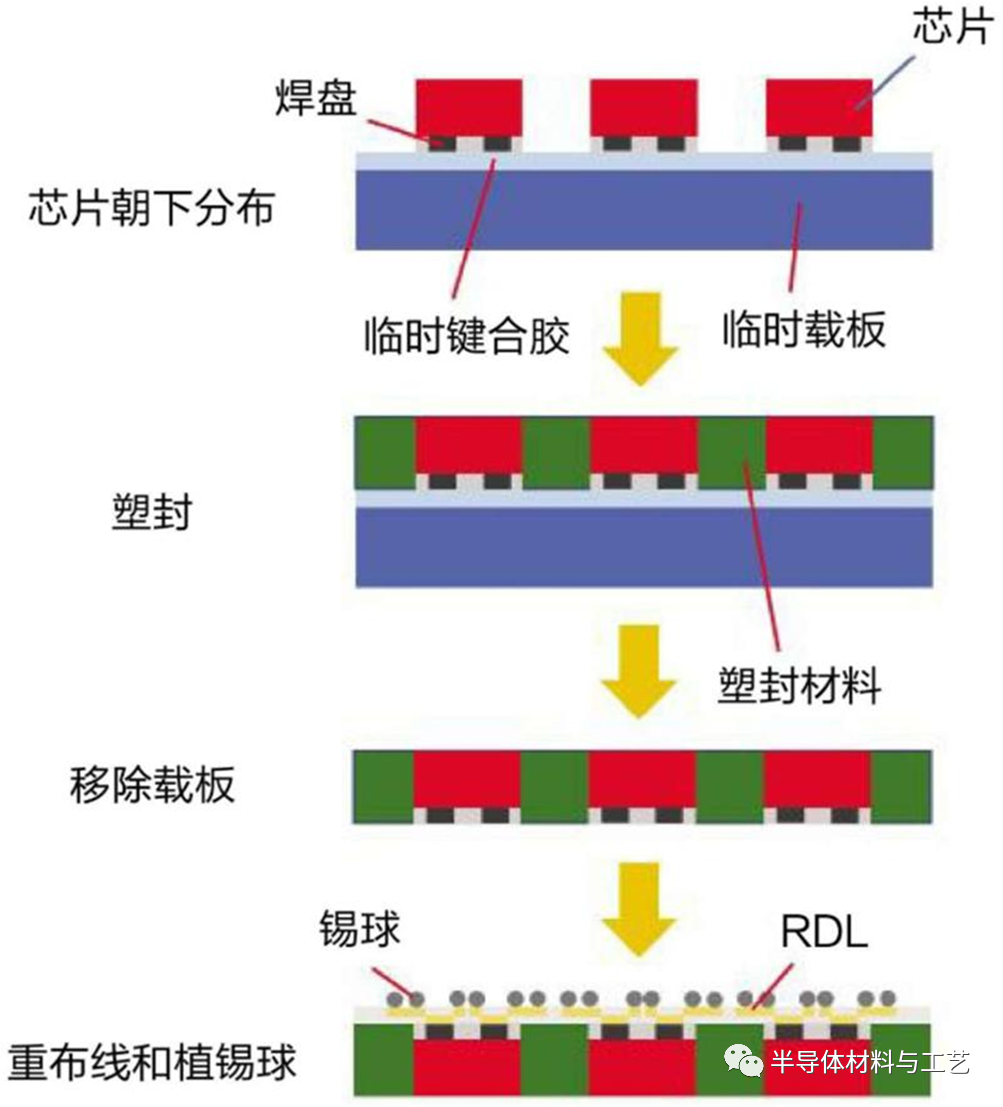

面朝下是让芯片的线路面朝下的工艺。面朝下与面朝上的区别主要在于芯片带有焊盘一侧的放置方向不同。(见图4)

图4 面朝下的先芯片处理工艺示意图

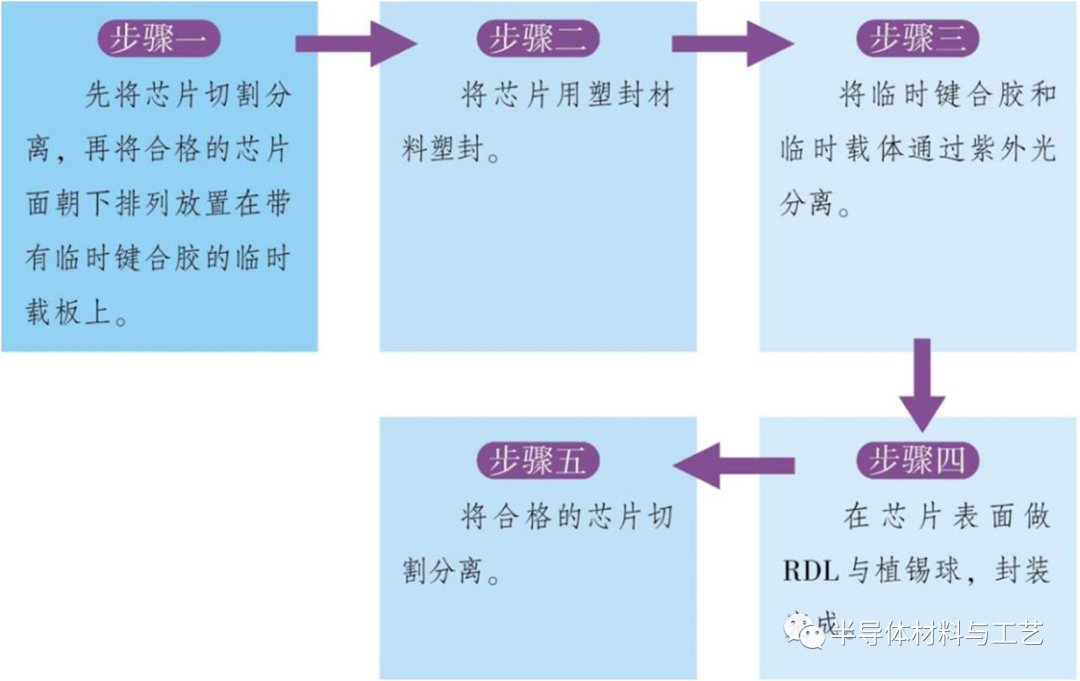

面朝下的先芯片处理工艺流程如下:

3、面朝下的后芯片处理。

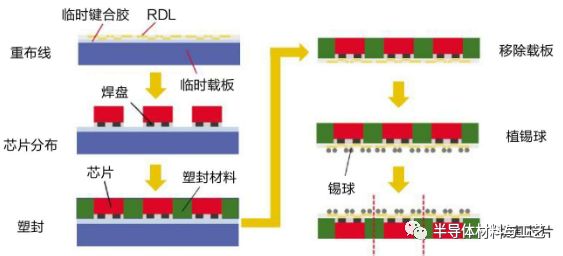

后芯片是先在临时胶带表面进行RDL工艺,然后通过面朝下的方式将芯片与RDL互连,在注塑机中进行塑封、植锡球后完成切割。其与先芯片的主要区别在于RDL的先后顺序。

图5 面朝下的后芯片处理工艺示意图

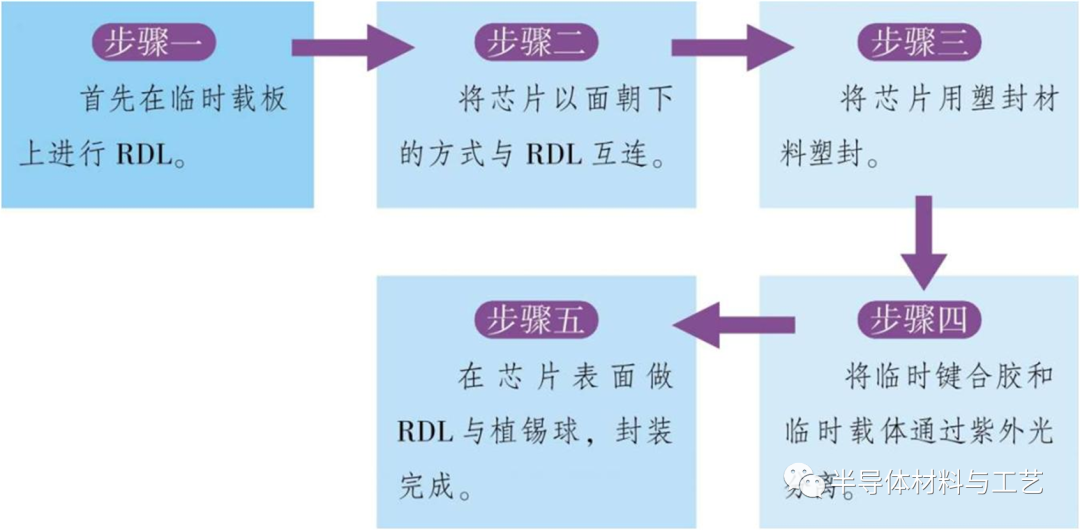

面朝下的后芯片处理工艺流程如下:

综上所述,面朝上的先芯片处理工艺由于需要利用CMP将塑封层减薄,所以此工艺成本较高,一般封装厂较少采用。面朝下的先芯片处理工艺在移除载板并添加RDL制程时易造成翘曲,所以工艺操作时需要提前防范,但是此工艺封装厂应用较多,例如苹果的A10处理器。面朝下的后芯片处理工艺先采用RDL工艺,这样可以降低芯片封装制程产生的不合格率,目前封装厂应用也较多。

在FOWLP工艺中,重布线层作为工艺中必不可少的一个环节,它是在晶圆表面沉积金属层和绝缘层形成相应的金属布线图案,采用高分子薄膜材料和Al/Cu金属化布线对芯片的I/O焊盘重新布局成面阵分布形式,将其延伸到更为宽松的区域来植锡球。

在扇出型晶圆级封装中主要有两种RDL工艺,分别是:①感光高分子聚合物+电镀铜+蚀刻;②PECVD+Cu-damascene+CMP。市场上第一种工艺应用更为广泛。接下来分别对这两种RDL工艺进行详细解读。

(1)感光高分子聚合物+电镀铜+蚀刻。首先在整个晶圆表面涂覆一层感光绝缘的PI材料,然后使用光刻机对感光绝缘层进行曝光显影;感光绝缘层在200℃的环境下烘烤一小时后形成大约5微米厚的绝缘层;在175℃的环境下通过PVD设备在整个晶圆表面溅射Ti作为阻挡层(Barrier Layer)和Cu作为导电的种子层(Seed Layer);再通过涂覆光刻胶曝光显影;接着在暴露出来的Ti/Cu层上电镀铜,用于增加铜层厚度,确保芯片线路的导电性;剥离光刻胶并蚀刻Ti/Cu种子层,此时第一层的RDL制作完成。重复上述步骤便可形成更多层的RDL线路。此工艺在扇出型封装工艺中应用较为广泛。(见图6)

图6 第一种RDL工艺流程示意图

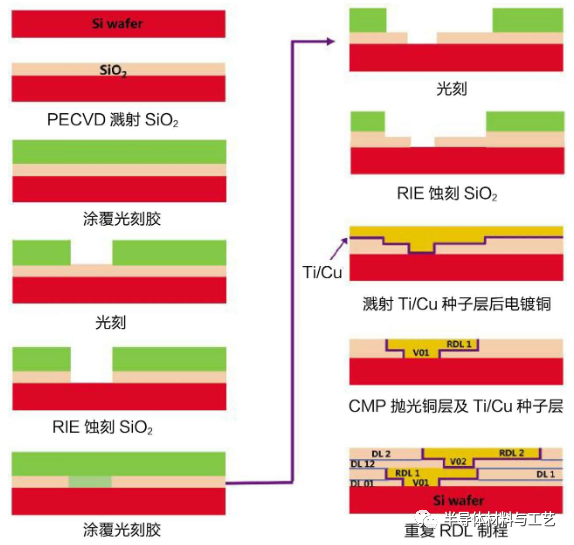

(2)PECVD+Cu-damascene+CMP。

该工艺使用SiO2或Si3N4作为绝缘层,并使用电镀工艺在整个晶圆上沉积一层铜,然后使用CMP去除凹槽外多余的铜和种子层以制备RDL的铜导电层。

首先,使用等离子体增强型化学气相沉积(Plasma Enhanced Chemical Vapor Deposition, PECVD)在晶圆表面形成一层薄的SiO2(或Si3N4)层,然后在SiO2表面涂覆一层光刻胶,随后使用光刻机对感光绝缘层进行曝光显影,并使用反应式离子蚀刻法(Reactive Ion Etching, RIE)除去SiO2,接下来剥离剩余的光刻胶。再重新涂覆光刻胶后,进行曝光显影形成图案,然后再用RIE除去开口处一定厚度的SiO2。接着在表面溅镀Ti/Cu种子层,并在整个晶圆上使用电镀工艺镀上一层铜,接下来采用CMP去除多余的电镀铜和Ti/Cu种子层,最后得到第一层的RDL线路,此方法称为双重Cu-damascene法。重复以上步骤以获得更多的RDL。(见图7)

图7 第二种RDL工艺流程示意图

扇出型封装面临的挑战

虽然FOWLP可满足更多I/O数量、具有良好的散热性能和低延时的需求,但该技术的大量应用首先必须解决以下问题:

(1)焊接点的热膨胀问题。因FOWLP的结构与BGA相似,FOWLP焊接点的热膨胀情况与BGA非常相近,FOWLP中锡球的关键位置在芯片的下方,同样在芯片和PCB之间也会发生热膨胀系数不匹配的问题。

(2)芯片位置的精确度。在重新建构排布时,必须要维持芯片从抓取到放置(Pick and Place)于载具上的位置不发生偏移,甚至在铸模作业时,也不可发生偏移。

(3)晶圆的翘曲问题。芯片放置于临时载板的过程中,晶圆经过切割后,芯片在载板上重新排布时产生的翘曲(Warpage)问题,也是一项重大挑战,因为重新建构晶圆含有塑胶、硅及金属材料,硅与胶体的比例在X、Y、Z三方向不同,铸模在加热及冷却时的热胀冷缩会影响晶圆的翘曲行为。

(4)模具移位。模具移位是另一个工艺难题,它是指放置在载体晶圆上和包覆成型过程中模具轻微移动。然而,对于基于晶圆的技术来说,模具移位是一个挑战,随着对面板级封装的尺寸变大,模具移位变得更加关键。

来源:半导体封装工程师之家

申明:感谢原创作者的辛勤付出。本号转载的文章均会在文中注明,若遇到版权问题请联系我们处理。

----与智者为伍 为创新赋能----

联系邮箱:uestcwxd@126.com

QQ:493826566