本文转自电子发烧友网

感谢电子发烧友网对新思科技的关注

自UCIe™(通用芯粒互连技术)联盟成立和UCIe 1.0规范发布以来,芯粒/Die-to-Die生态系统一直备受瞩目。要在不影响功耗、性能和面积(PPA)目标的前提下,设计和实现既能利用异构系统,又能稳健运行的设计方案,IP架构师和开发者任务艰巨。系统架构师和开发者正在努力将UCIe技术应用到下一代SoC。验证团队在收到分解的芯片RTL之前,就已开始紧锣密鼓地制定基于集成逻辑的测试和覆盖计划。

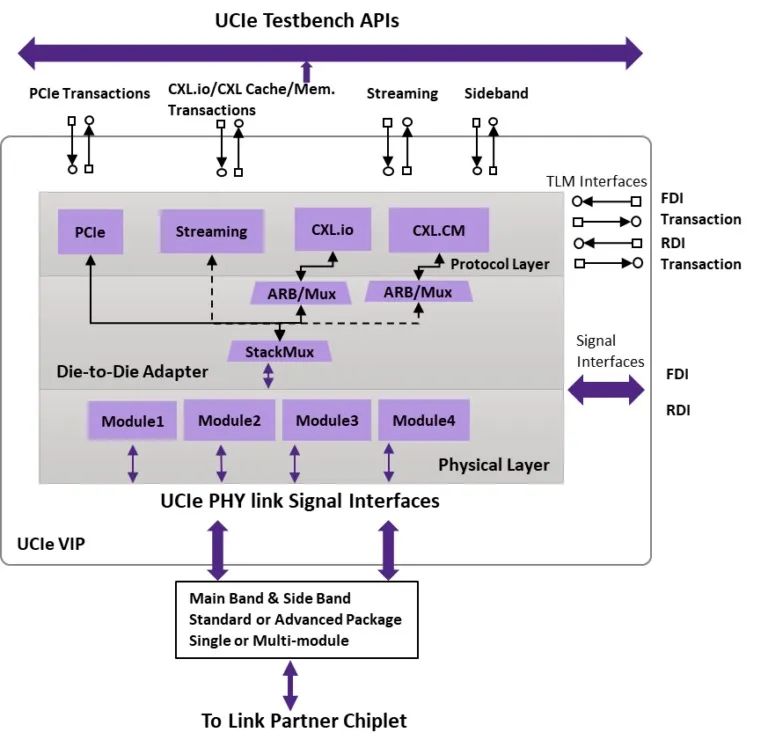

UCIe1.0版规范由以下几个部分组成:

多层协议:应用专用协议层、Die-to-Die适配器和物理层

不同层级之间的信令接口

① 协议层与Die-to-Die适配器之间的FDI(支持flit的Die-to-Die接口)

② Die-to-Die适配器与物理层之间的RDI(原始Die-to-Die接口)

③ 两个芯片之间的物理链路接口

各层均有独立的主带和边带接口

原生规范支持CXL、PCIe和自定义steaming协议

物理层接口中的单模块和多模块

1.0版规范重点关注信令和芯粒架构的功能,而1.1版则涉及一些合规性和互操作性事项,以支持多供应商异构系统。

UCIe 1.1的新功能特性

串流协议支持flit模式

串流模式支持CRC和重试

Die-to-Die适配器上的堆栈多路复用器提供两种不同协议可选

适用于steaming的非对称模式

多模块链路模式

UCIe 1.0与UCIe 1.1规范之间有何区别

在UCIe 1.0规范中,只有原始模式支持串流协议,UCIe仅用于传输层,但在UCIe 1.1规范中,串流协议中增加了flit格式。这些都是可选格式,以便通过自定义协议来使用经过延迟优化的68B/256B/256B flit适配器功能。1.1版规范还支持CRC检测,以确保对所有随机错误进行3bit检测,另外增加了相应的重播缓冲区,以便在串流模式下出现CRC错误时重启事务。

在1.0版规范中,只有Die-to-Die适配器处的堆栈多路复用器可在两个多路复用器输入端使用相同协议,但在1.1版规范中,堆栈多路复用器支持在单个UCIe实例中使用多个协议的组合。这样便可在这些协议之间共享Die-to-Die适配器的带宽。1.1版协议还支持在串流模式下采用非对称模式,通过编辑寄存器将配置设为EP(端点)或RC(根联合体)。

在单独的层设计中,还需通过多种验证拓扑结构来支持端到端验证。这些拓扑结构可在背靠背模式下支持被测设计(DUT),通过测试序列器或互操作DUT与VIP连接来产生流量。对于系统验证,最适合的拓扑结构为全栈式实现方案,即所有层都可以拼接到一起,以创建完整系统。支持这类用例的典型验证环境如图1所示。由于堆栈多路复用器支持多种协议,验证系统将封装CXL、PCIe和串流(自定义)协议,以支持所有用例。

就物理层而言,1.1版增加了用于高级封装的x32引脚模块功能,而1.0版仅支持x16和x64引脚物理层接口。

为满足UCIe DUT与UCIe参考设计之间的互操作性测试要求,额外增加了合规性和测试调试寄存器。

支持多协议的典型UCIe系统

新思科技UCIe解决方案

新思科技与业内领先企业一直保持紧密合作,以支持新版UCIe 1.1规范的功能特性和用例。

新思科技的完整通用芯粒互连技术(UCIe)IP解决方案包含控制器、PHY和验证IP。新思科技UCIe控制器和PHY IP解决方案实现了稳健可靠的Die-to-Die链路,具有针对已知良好芯片的可测试性功能和用于纠错的CRC或奇偶校验。

新思科技为硬件辅助平台提供验证IP(VIP)、测试套件和协议解决方案。合作伙伴可以利用新思科技广泛的互连产品组合,提前对芯粒设计进行验证。

新思科技IP使用独立开发的新思科技VIP进行验证,为各大公司提供出色的UCIe解决方案。完整的开箱即用解决方案让开发者可以专注于芯片设计特性和差异化,以加快产品上市。

由于UCIe的目标用途是实现Die-to-Die互联,对于芯粒RTL所需的有效载荷,需要基于硬件的快速流片前解决方案。新思科技事务处理器基于新思科技IP,可实现快速的验证硬件解决方案,包括新思科技ZeBu®硬件加速系统和用于验证用例的新思科技HAPS®原型系统。

新思科技协议验证解决方案与新思科技验证系列产品进行了原生集成,其中包括新思科技Verdi®调试和回归管理,以及新思科技VC执行管理器的自动化。

点击阅读原文了解更多关于新思科技VIP和协议解决方案的信息。