本文来自“2023新型算力中心调研报告(2023)”。更多内容参考“《海光CPU+DCU技术研究报告合集(上)》 ”,“《海光CPU+DCU技术研究报告合集(下)》 ”和“龙芯CPU技术研究报告合集”。

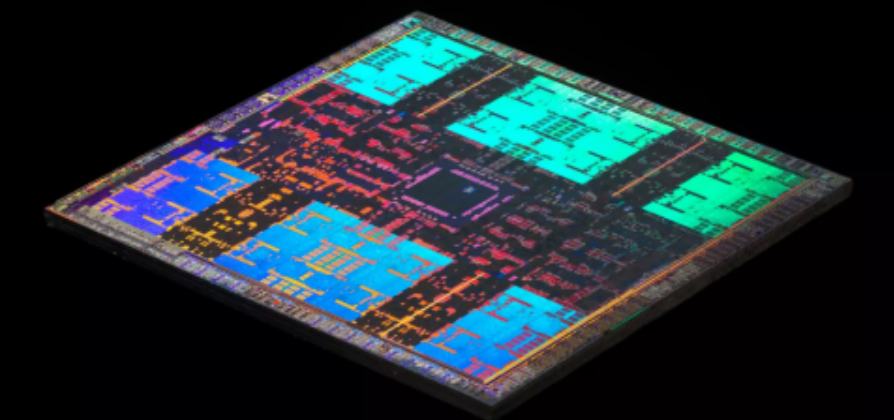

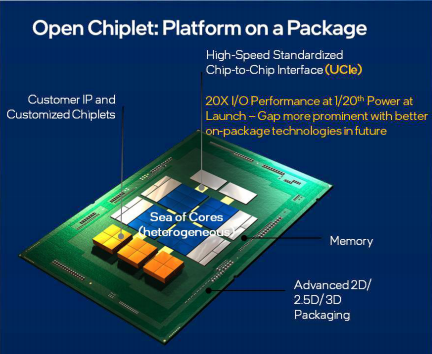

Chiplet 的优势已经获得了充分的验证,接下来的问题就是通用化、标准化。通过标准化,来自不同供应商的芯片可以更容易地实现封装内的互联,在这个前提下,部分 IP 可以固化为芯片,而不再需要分别集成到不同客户的芯片中,也不需要适配太多版本的生产工艺。在此愿景之下,2022 年 3 月,通用处理器市场的核心玩家 Intel、AMD、Arm 等联合发布了新的互联标准 UCIe(Universal Chiplet Interconnect Express,通用小芯片互连通道),希望解决 Chiplet 的行业标准问题。由于标准的主导者与 PCIe 和 CXL(Compute Express Link)已有千丝万缕的关系,因此,UCIe 非常强调与 PCIe/CXL 的协同,在协议层本地端提供 PCIe 和 CXL 协议映射。与 CXL 的协同,说明 UCIe 的目标不仅仅是解决芯片制造中的互联互通问题,而是希望芯片与设备、设备与设备之间的交互是无缝的。在 UCIe1.0 标准中,即展现了两种层面的应用:Chiplet(In package)和Rackspace(Off package)。

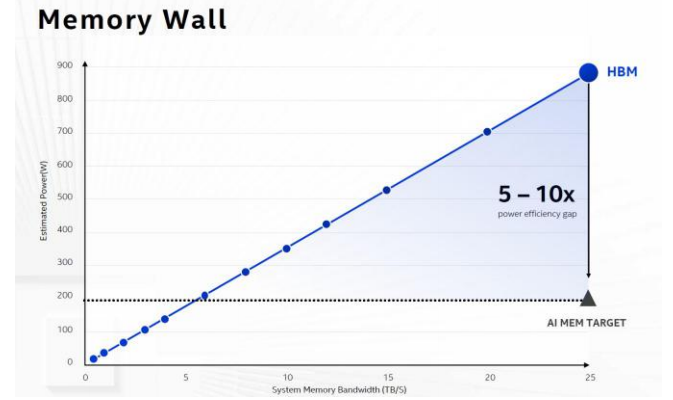

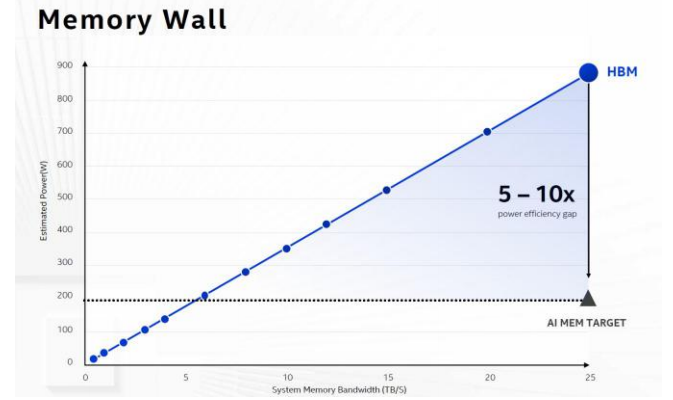

过去十年间,CPU 的核心数量从 8~12 个的水平,增长到了 60 乃至 96 核,Arm 已有 192 核的产品,而每插槽 CPU 的内存通道数仅从 4 通道增加到 8 或 12 通道。每通道的内存在此期间也经过了三次大的迭代,带宽大概增加 1.5~2 倍,存储密度大约为 4 倍。从发展趋势来看,每个 CPU 核心所能分配到的内存通道数量在明显下降,每核心可以分配的内存容量和内存带宽其实也有所下降。这是内存墙的一种表现形式,导致 CPU 核心因为不能充分得到数据来处于满负荷的运行状态,会导致整体计算效率下降。

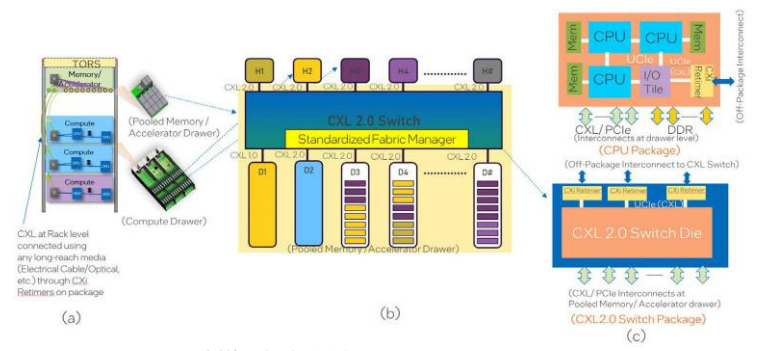

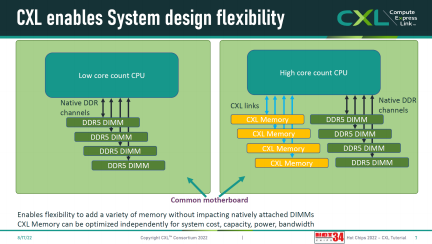

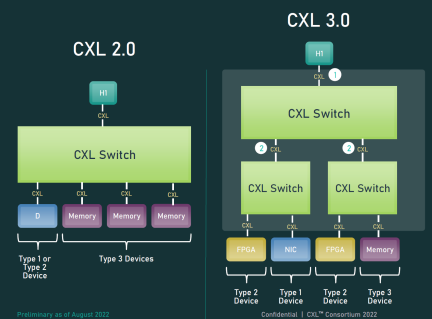

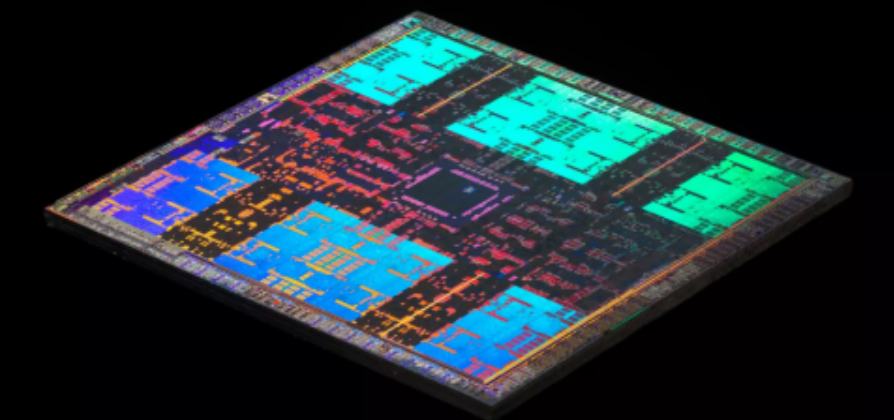

为什么增加内存通道如此缓慢?因为增加内存通道不仅仅需要增加芯片面积,还需要扩展对外接口,在电气连接方式没有根本性改变的情况下,触点数量的大量增加会导致 CPU 封装面积剧增。10 年前的英特尔至强(Intel Xeon)处理器的 LGA2011 封装尺寸为 52.5mm×45.0mm(毫米),当前 Xeon 所用 LGA 4677 封装尺寸为 77.5mm×56.5mm,触点数量增加了 1.33 倍,封装面积增加了 1.85 倍。而 AMD 第四代 EPYC 启用的新封装 SP5 更大,有 6096 个触点,封装面积达到 75.4mm×72mm,跟一张扑克牌差不多大了,毕竟它的内存通道数量达到了 12 个。为了与 AMD 和 Arm 继续“核战”,英特尔代号 Granite Rapids 和 Sierra Forest 的下一代 Xeon 将启用 LGA 7529 插槽,尺寸 105mm×70.5mm。作为参考,iPhone 4的正面尺寸是 115.2mm×58.6mm,iPhone 8 则为 138.4mm×67.3mm。同时,主板上内存相关的走线数量和距离也需要相应增加,保证信号质量的难度加大。CPU 插槽面积增加、内存槽数量增加,还受到主板面积的限制。按照英特尔和 AMD 的通用处理器的这个发展趋势, 双路服务器的主板布局将会愈加困难,其市场份额可能会逐步下降。通过 CXL 扩展内存,可以将 CPU 与内存从沿革多年的紧耦合关系变为松耦合,利用 PCIe/CXL 通道的物理带宽增加内存总带宽,而不仅仅限于内存控制器自身的通道总数(即使前者的带宽相对较低,但也是增量),利用机箱的立体空间容纳更大容量的内存,而不再受主板面积的约束。考虑到人工智能,尤其是机器学习领域的发展,模型容量在过去 5 年间大致增加了 50 倍,内存容量的扩展方式确实值得突破一下。不过这也不是一蹴而就的,毕竟第四代英特尔至强可扩展处理器每插槽 CPU 只支持 4 个 CXL 设备,给计算卡之类的一分就没了。所以也就不用纠结它暂时没有宣布支持 CXL Type 3 Device(Memory Buffer)。在第四代可扩展至强处理器平台上,如果支持 CXL 1.1 的加速卡、计算卡 、智能网卡能够提供比 PCIe 5.0 更好的性能,稍微拉近跟 SMX 接口(NVLink)的性能落差,那就非常开心了。而 AMD 则反过来,处理器大核确实多,而且不论单路还是双路处理器,内存槽上限都是 24 条,如果不优先另辟蹊径扩展内存容量,每个核心能够分配到的内存资源其实反而会落了下风,补短板看起来更迫切。但是,AMD 同样也会面临内存扩展与计算卡抢PCIe 通道数量的问题。总之,不论这两家通用处理器具体各怀啥心思,CXL 的第一轮普及工作就是不尽如人意,顾此失彼。甚至现在还不到纠结内存扩展的时候,即使 CXL 内存模组已然是各种技术论坛中样品最接近现实的 CXL 设备。在这个阶段,解决 CXL 设备的有无问题,借机逐步导入 EDSFF,初步形成生态环境,就算是成功。至于内存的大事情,且得看下一代平台以及更新版本的 CXL。到了 CXL 2.0,通过 CXL Switch,内存扩展将可以跨 CPU 实现。这个阶段将构建机柜级的资源池化。这其中的好处多多,此处主要集中在云服务的需求角度去看。微软曾调研了 Azure 公有云数据中心的内存使用情况,其结论是:有约 50% 的服务器的实际内存利用率不到一半。这是由于内存的分配是与 CPU 核心绑定的,当客户按照预设的实例配置租用资源时,每个核心便搭配了固定容量的内存,譬如 2GB。当主机的 CPU 核心数量被分配完毕后,未被搭配的内存便被闲置了。考虑到预先配置的内存容量相对核心数量必然是超配的,譬如 56 核的至强,搭配 128GB 内存,每个实例配 2GB 内存的话,那注定有 128-2×56=16 GB 内存将会被闲置。如果服务器核心未被充分利用,被闲置的内存将会更多。而运行中的实例,其实际内存占用率通常也不高。由此,无从分配的、未被分配的、分配但未充分使用的,这三种性质的浪费叠加之后,主机的实际内存浪费相当惊人。由此,微软提出通过内存池来解决这个问题。各主机搭配容量较少的内存,其余内存放入内存资源池。当 CPU 本地内存不足时,再到内存池调用。这虽然增加了一些访问延迟,但会降低内存的总成本。如果减少 10% 的内存搭配数量,对于大型数据中心而言也是数以亿计的资金节约。微软预计通过 CXL 和内存池化,可以为云数据中心减少 4~5% 的成本。除了节约总内存投入,内存池化还可以带来内存持久化、内存故障热迁移等等新的功能特性以供业界进一步挖掘,此处暂不展开。CXL 的完整愿景,需要到 CXL 3.0 规范才能实现。首先是带宽,CXL 3.0 基于 PCIe 6.0,更换了 PCIe 沿革多年的 NRZ 调制方案,变为 PAM-4 脉冲幅度调制编码,在电气特性变化不大的情况下,链路带宽翻倍,从 32GT/s 提升到了 64GT/s。其次,CXL3.0 增加了对二层交换机的支持,也就是叶脊(Leaf-Spine)网络架构,资源池化也不再局限于内存,而是可以实现 CPU 资源池、加速器资源池、网卡资源池等。CXL 2.0 实现的是机柜内的池化,CXL 3.0 除了可以在一个机柜内实现计算资源和存储资源的解耦和池化,还可以在多个机柜之间建立更大的资源池。跨主机、跨机柜调度规模巨大的计算资源,已经是超算的范畴了。然后,CXL 3.0 网络可以支持 4096 个 CXL 节点!单纯从数量上看,这远远超过了 NVLink 网络 256 个节点的规模(见下一章)。这将是 CXL 对私有但标榜高性能的 NVLink 最有力的挑战。当然,CXL 3.0 依旧暂时还未落地,而 NVIDIA 新一代的系统已经正式发布了。二者在机柜互联方面的带宽远超 400G InfiniBand(IB)或者以太网,实际运行效率都是非常值得期待的。

2、迈向智能世界白皮书2023版(云计算)

3、迈向智能世界白皮书2023版(数字金融)

4、迈向智能世界白皮书2023版(数据通信)

5、迈向智能世界白皮书2023版(数据存储)

《FMS 2023闪存峰会CXL合集(1)》

3、数据中心绿色设计白皮书(2023)

4、新型数据中心高安全技术体系白皮书

3、未来网络白皮书——白盒交换机技术白皮书.pdf1、算力网络关键技术及发展挑战分析

2、中国算力网络全景洞察白皮书

3、算力感知网络CAN技术白皮书(中国移动)

4、算力时代网络运力研究白皮书

5、数字中国建设关键基础设施,算力网络时代来临(2023)

6、算力网络技术白皮书7、算力网络场景下SLA约束的能耗优化微服务调度策略(2023)

8、网络算力接入时延圈绘制展示研究和实践(2023)

9、浅析面向算力时代全光底座的构建

10、云渲染任务智能算力调度策略研究(2023)

11、算力网络推进金融元宇宙落地(2023)

12、全光算力网络关键技术及建设策略研究(2023)数据中心绿色设计白皮书(2023)

存储系统性能和可靠性基础知识

云基建专题:AI驱动下光模块趋势展望及弹性测试

精华:数据库系统的分类和评测研究

可重构计算:软件可定义的计算引擎

近存及存内计算专题简介

集装箱冷板式液冷数据中心技术规范

浸没式液冷发展迅速,“巨芯冷却液”实现国产突破

两相浸没式液冷—系统制造的理想实践

浸没液冷服务器可靠性白皮书

天蝎5.0浸没式液冷整机柜技术规范

AIGC加速芯片级液冷散热市场爆发

某液冷服务器性能测试台的液冷系统设计

《智能存储与磁盘故障预测合集》

《内存技术应用研究及展望合集》

本号资料全部上传至知识星球,加入全栈云技术知识星球下载全部资料。

免责申明:本号聚焦相关技术分享,内容观点不代表本号立场,可追溯内容均注明来源,发布文章若存在版权等问题,请留言删除,谢谢。

温馨提示:扫描二维码关注“全栈云技术架构”公众号,点击阅读原文进入“全栈云技术知识”星球获取10000+技术资料。