今天看皮皮虾的时候看见一个视频真的不是滋味,一位摄影家给一位农民一张照片。

他拿着照片陷入沉思,是迷茫,是震惊,是苦涩。仔仔细细看着照片中的人,很陌生又很熟悉:难道我已经这么老了吗?

劳碌半生不识君,今日方知我是我

水浒传

中国确实是这样,有说不清的人就像被抛弃,一边是快速发展的光鲜亮丽,一边是这样的不知道怎么办的人,守着父辈的东西一直下去。

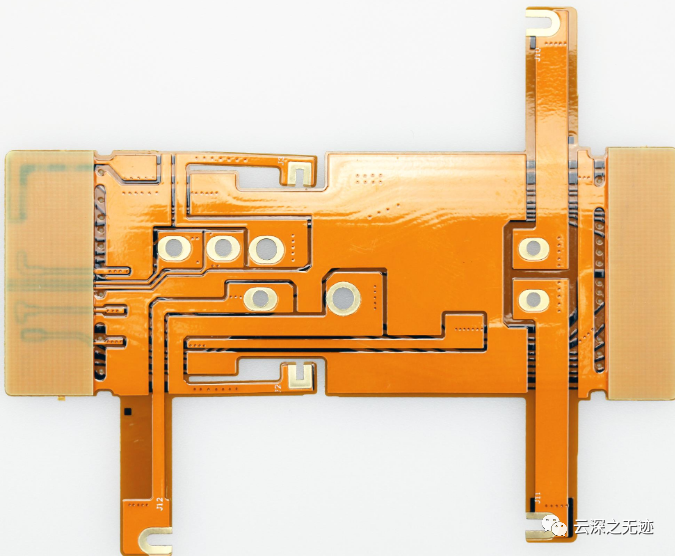

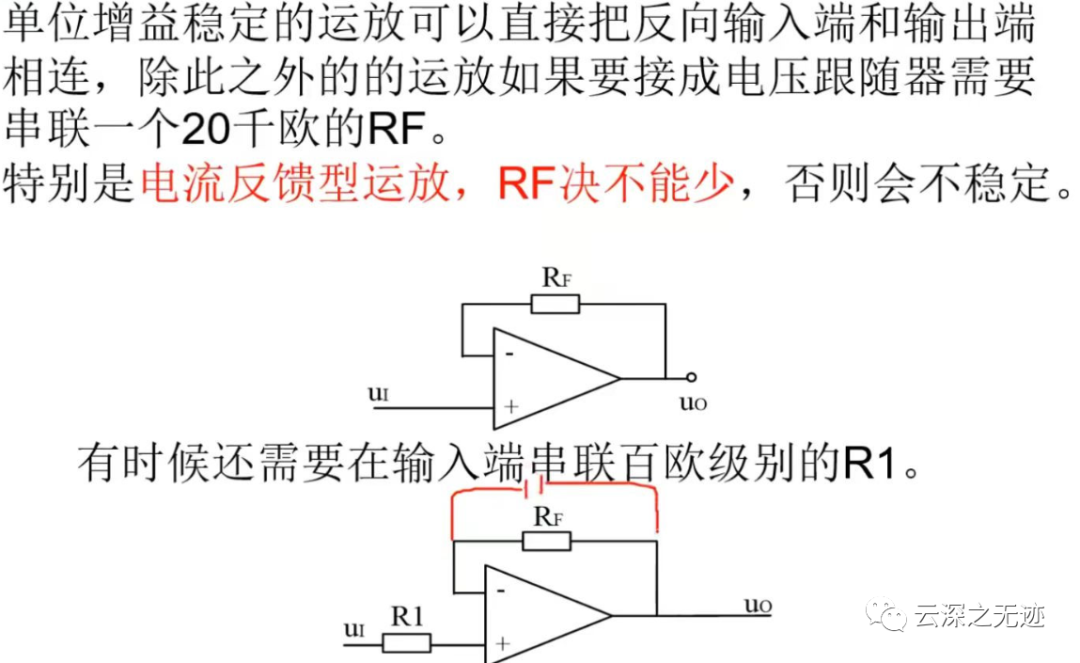

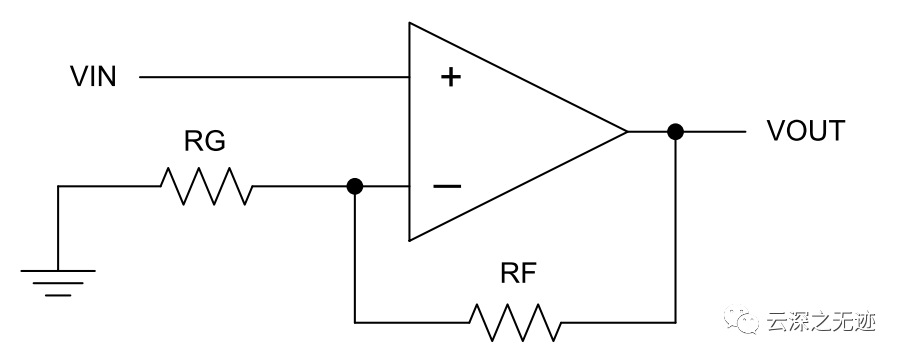

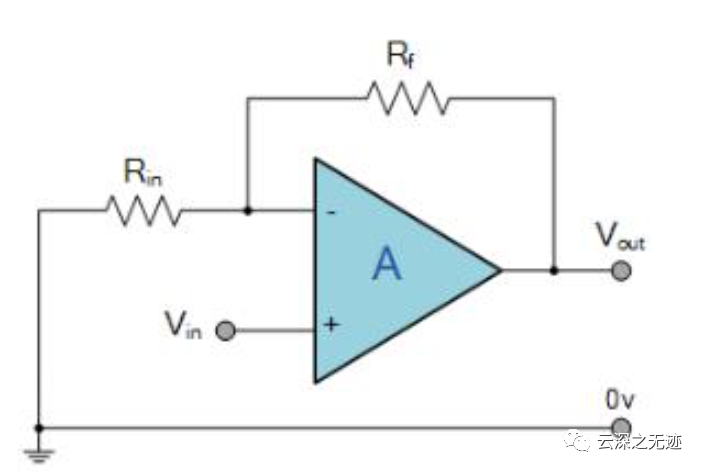

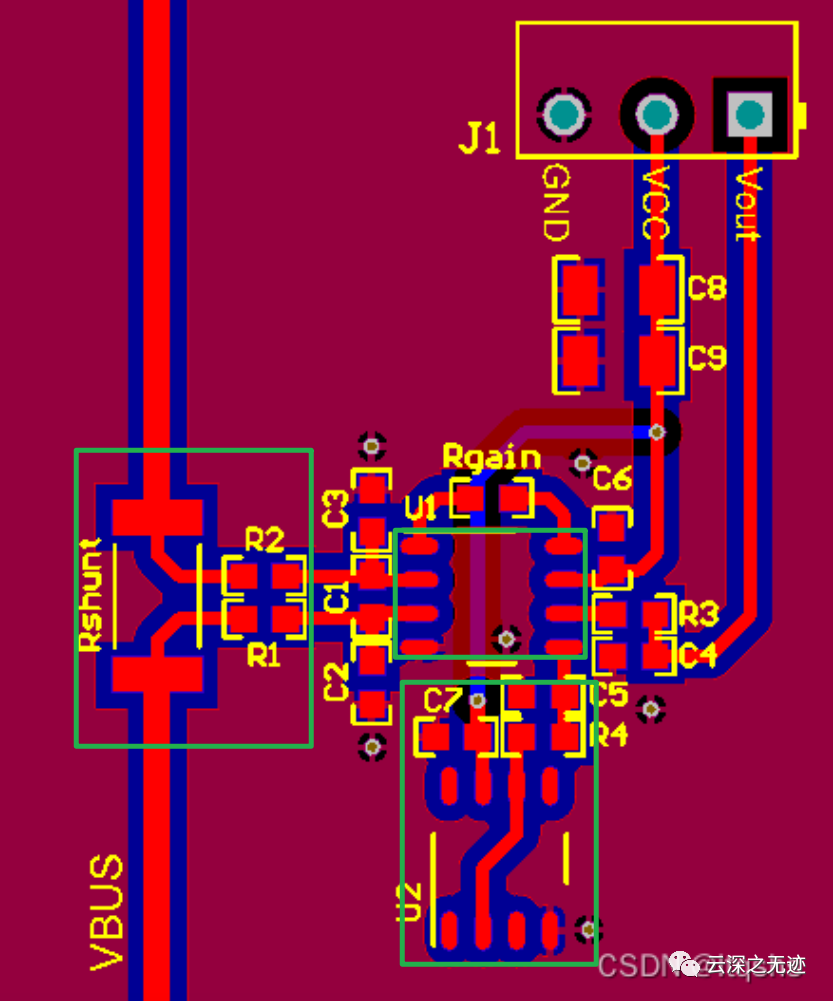

很离谱,看了这么多的文章视频,都是搬运,不像我,我还至少写俩个字。反正看了这么多文章来讲,对布线这个事情,应该是器件的摆放最重要。因为原理图设计的时候应该都是一个主要的芯片加一些外围的电路,然后就是留下来了输入和输出的接口。按照摆放以外,还需要注意的事情就是布局的时候按照的是信号的流向,就是最好信号的传输距离越短越好,不过在低速里面无所谓了。

现在用嘉立创先绘制几个板子,之后转别的,因为功能还是有点羸弱的。比如就没有原理图和PCB同框,只有下面这两个功能,不过倒是也够用了,我指的是你有两个屏幕,交叉的对照。

不过有的教程说的是要先布局电源。

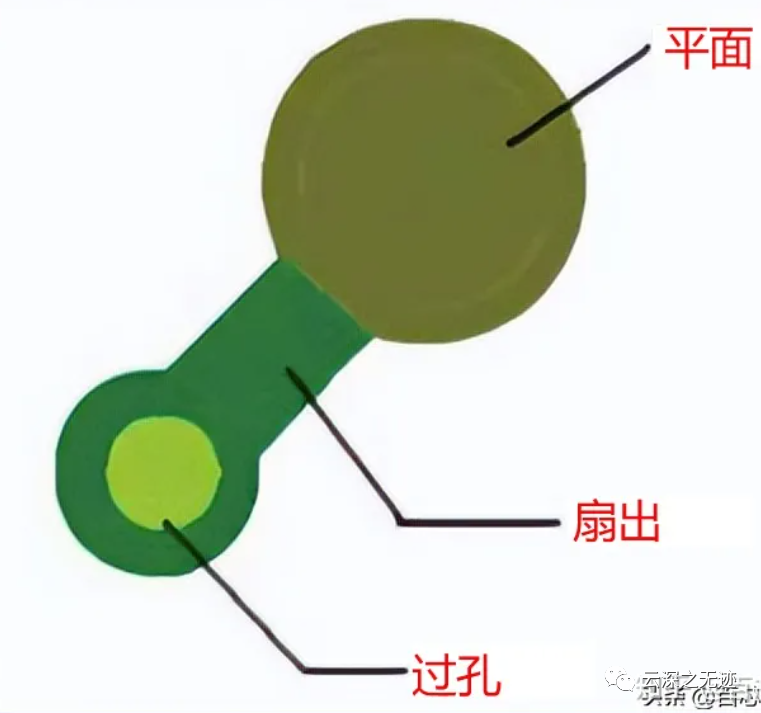

不过在B战看到一个教程觉得不错,在完成上面的布局以后就是要进行一个工作叫扇出?找了一下这个其实是服务于BGA封装的,就是下面实在是不好走线,就提前把上面的焊盘都引出来。

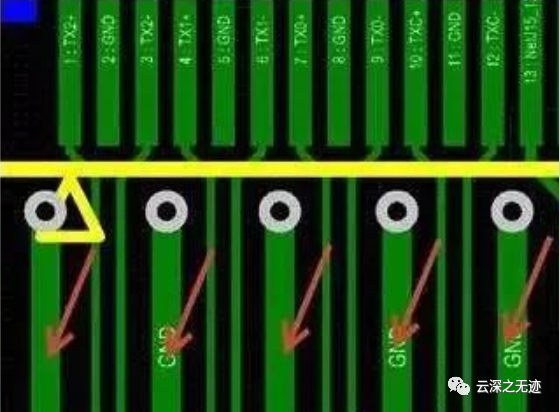

扇孔的目的有两个,打孔占位,减少回流路径!

比如GND孔,就近扇孔可以做到缩短路径的目的!预先打孔是为了防止不打孔后面走线的时候很密集的时候无法打孔下去,绕很远链一根GND线,这种就很长的回流路径了。

这种做高速PCB设计及多层PCB设计的时候经常遇到。预先打孔后面可以删除很方便,反之等你走线完了再想去加一个过孔,很难,这时候你通常的想法就是随便找根线连上便是,不能考虑到信号的SI,不太符合规范做法

就是这样的感觉

说简单点就是给所有的过孔上面引出东西,因为线走的密集了以后就不知道哪里会被干扰到。

还有就是多层板走线的时候,是看不见除了自己当前层之外的层里面的这个位置有没有东西的,你打个孔就不一样了。

还有就是多层板的理解也稍微的深刻了那么一点点、我以为的是底层和顶层就走所谓的信号线,第二层是地,第三层是Poewr。

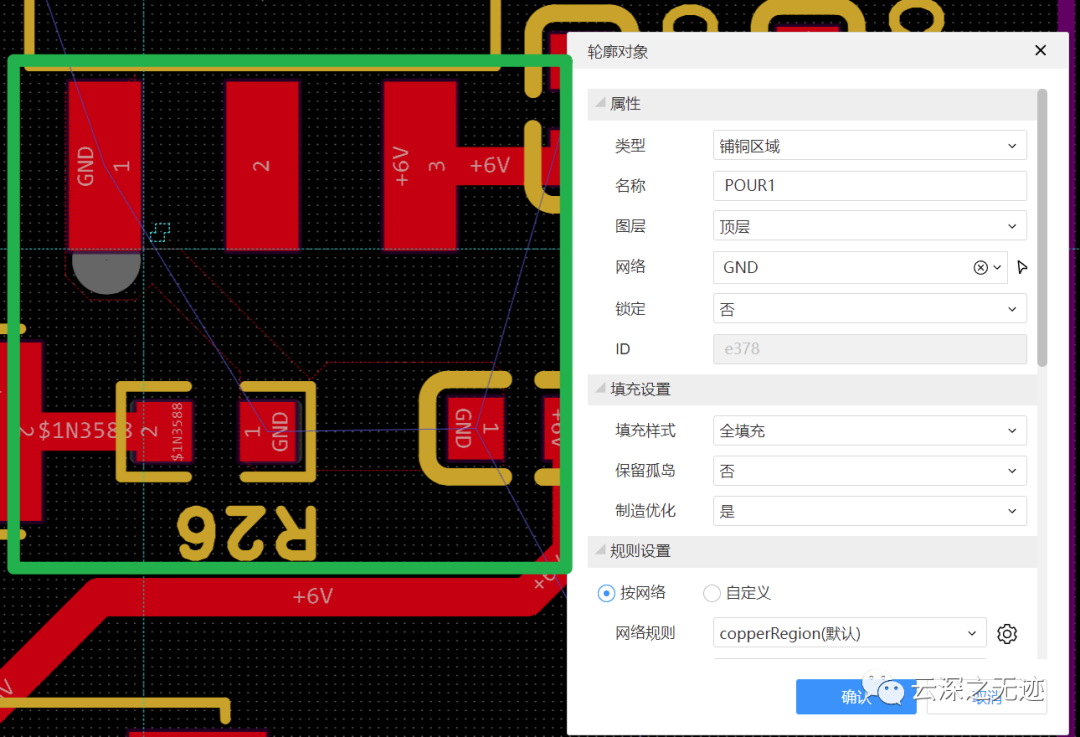

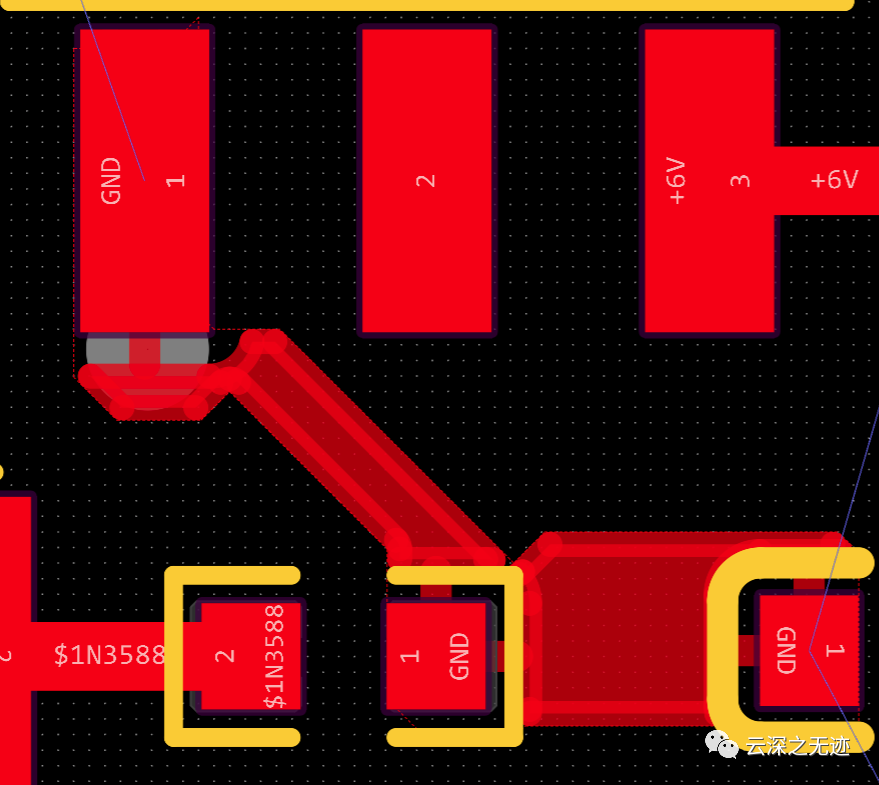

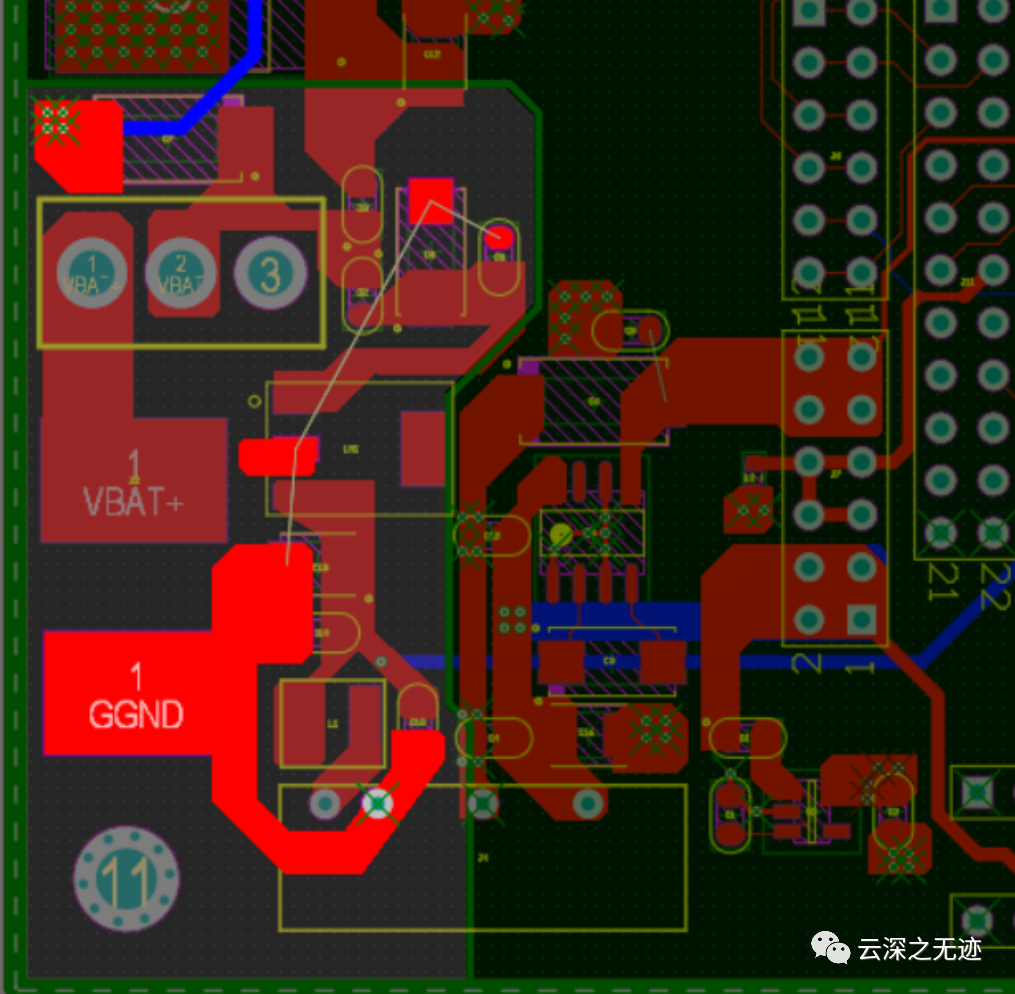

但是我看教程里面是这样做的,在扇出的阶段就把一些离的很近的GND,注意!就是GND,给铺铜了(覆铜,灌铜都可以)。我一直以为铺铜就是一个最后的工序而已,但是我觉得在前面完成这个过程好像挺合理的。

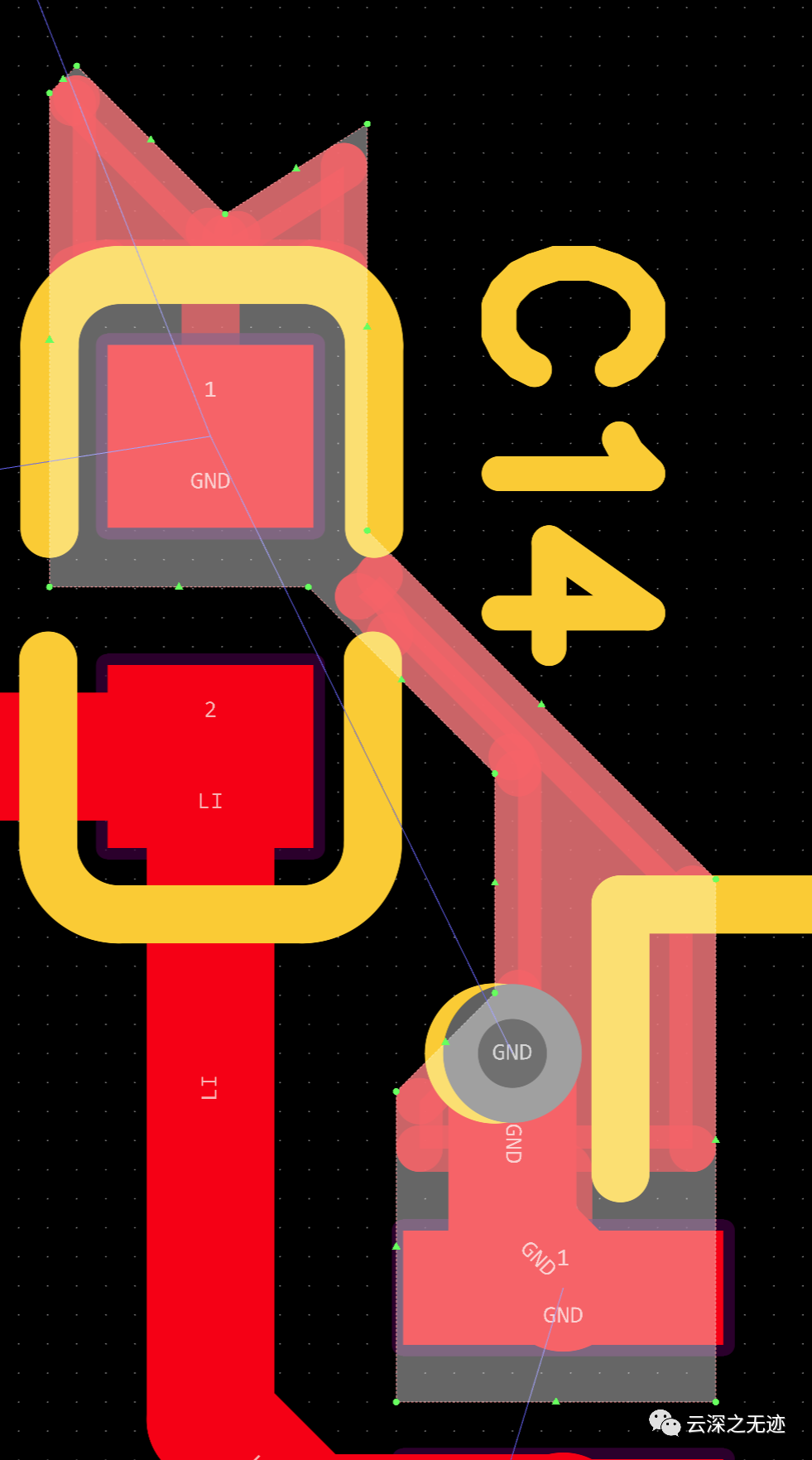

就是我现在这样

可能灌的不好,但就是这样这样的意思

有点难看,反正也就是这样就灌完了

所谓覆铜,就是将电路板上闲置的空间作为基准面,然后用固体铜填充,这些铜区又称为灌铜。

覆铜的意义在于,减小地线阻抗,提高抗干扰能力;降低压降,提高电源效率;与地线相连,还可以减小环路面积。

也出于让PCB焊接时尽可能不变形的目的,大部分PCB 生产厂家也会要求PCB 设计者在PCB 的空旷区域填充铜皮或者网格状的地线,

注意这个地方说的是!!!在空闲的位置,就是正好几个元件的GND在一块,其实在布局的时候也要有意识的去摆放。这个时候就铺一下。然后铺的时候或者是看见GND就赶紧打个孔下去,你放心,你还看我的文章,证明你还没有到玩高速的段位,无所吊谓的,打孔就对了。

印刷电路板上的布线的分布电容会起作用,当长度大于噪声频率相应波长的1/20 时,就会产生天线效应,噪声就会通过布线向外发射,如果在PCB中存在不良接地的覆铜话,覆铜就成了传播噪音的工具,因此,在高频电路中,千万不要认为,把地线的某个地方接了地,这就是“地线”,一定要以小于λ/20 的间距,在布线上打过孔,与多层板的地平面“良好接地”。

这个孔的电容其实有个公式来着。不记得了。

还有就是我以为4层板的电源是一定要走到稍微的电源层的,其实不是,实现PCB走线的第一个点就是将对应的地方联通就行!!!这个教程里面我如果没有看错,电源就没有走电源层,就是上下俩层来回走。但是有的也说电源优先走电源层,但是一些小电流电源可能会走到信号层。

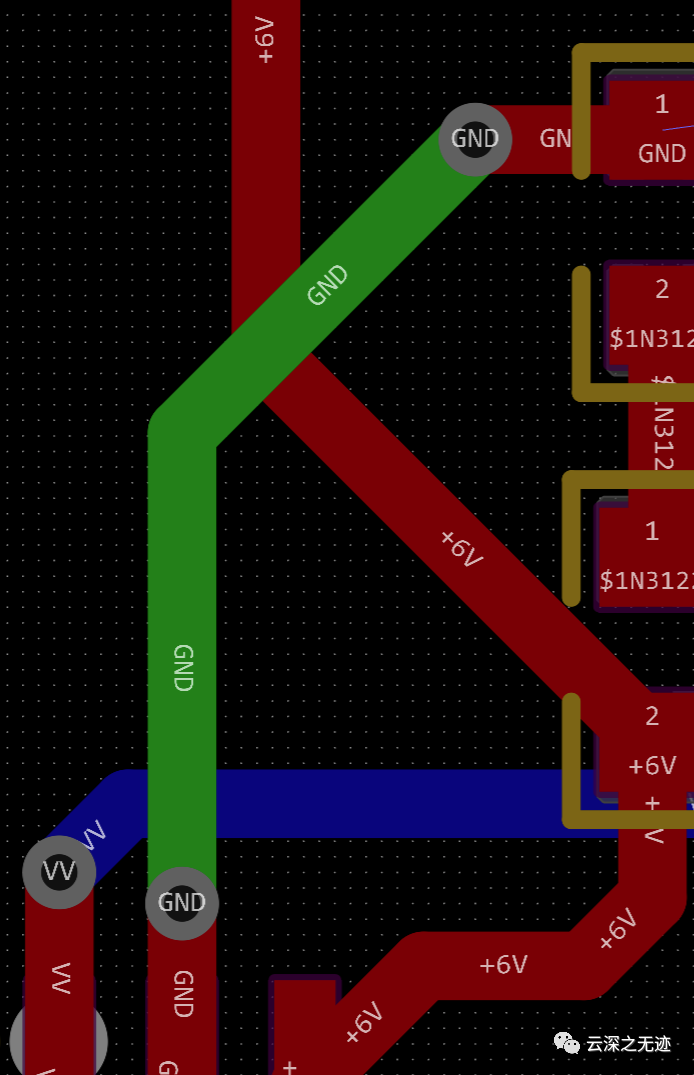

这个绿色的就是电源层,完全是可以可以走的

就是在走完GND,和信号线的时候再走电源线,但是要注电源平面分割的事情,就是GND也有很多。这里就简单的说是模拟和数字地。

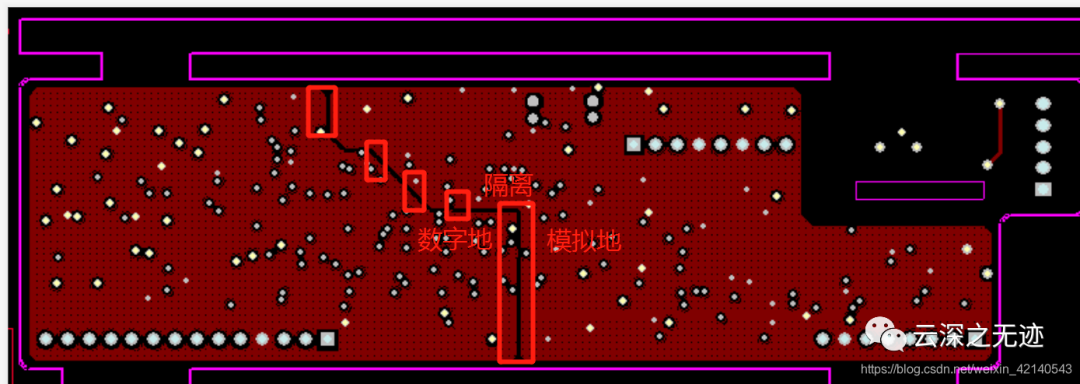

这个图是我找到的一个比较好的图

现在许多PCB不再是单一的数字或模拟电路,而是由数字电路和模拟电路混合构成的。因此布线的时候需要考虑它们之间的相互干扰问题,特别是地线上的噪声干扰。

数字地、模拟地和保护地要分开,并且保持2.5mm间距;数字地、模拟地保持1mm的间距。

这里没有截图

这就是割开了

这个图也好,就是说包地处理:邻近GND层走线,空间足够的情况下进行包地处理。

对了说下信号线:能不打孔则不打孔,减少走线长度。

孔的作用:一个面无法走的线,可以通过打孔,在另一个面进行走线。

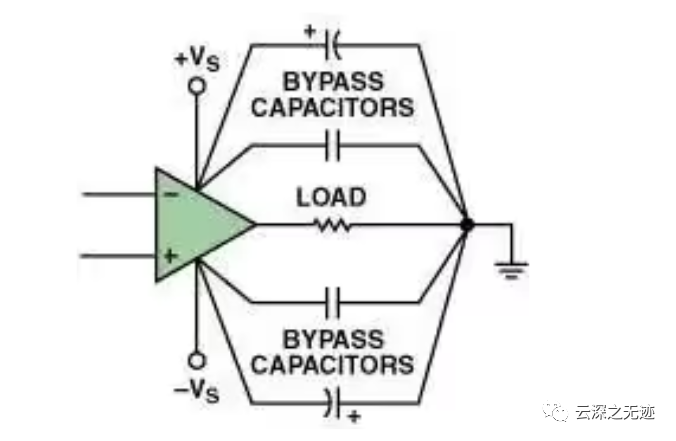

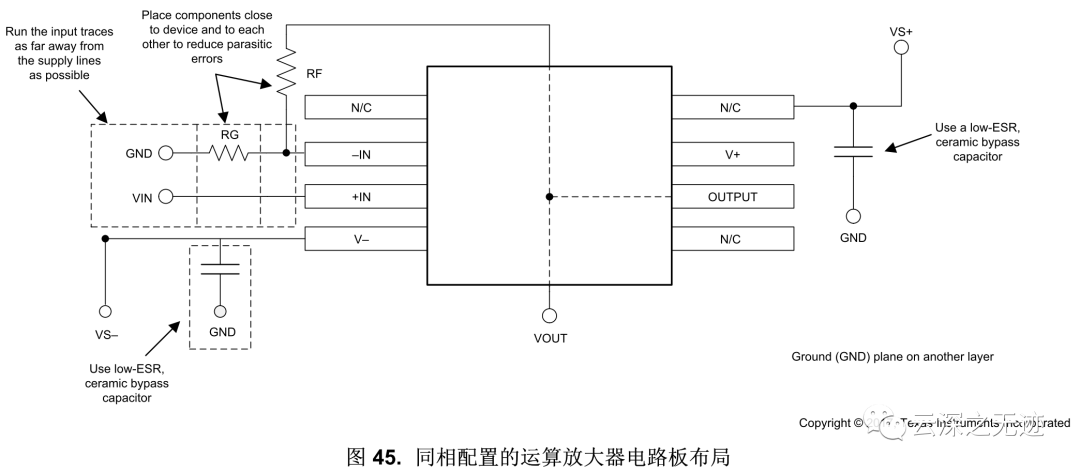

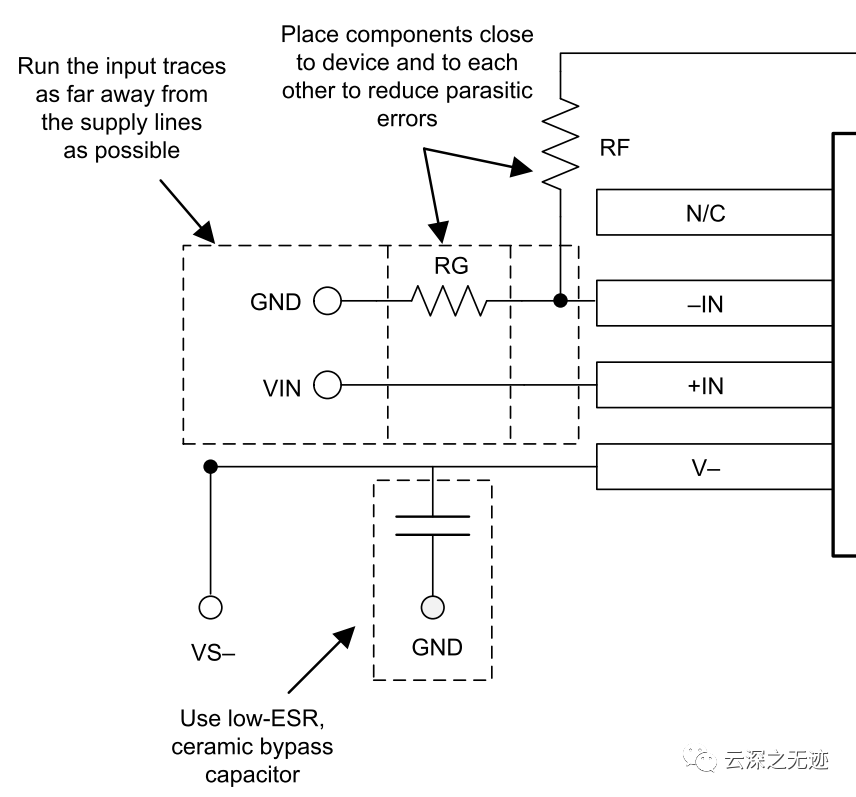

直接从运算放大器的电源引脚入手;具有最小电容值和最小物理尺寸的电容器应当与运算放大器置于PCB的同一面——而且尽可能靠近放大器。

电容器的接地端应该用最短的引脚或印制线直接连至接地平面。上述的接地连接应该尽可能靠近放大器的负载端以便减小电源端和接地端之间的干扰。

去耦电容应该尽量靠近芯片的电源引脚。如果使用了多个去耦电容器,应该将较小的去耦电容(旁路电容)放在离电源引脚最近的位置,将较大的去耦电容(库电容)放在远离电源引脚的位置。

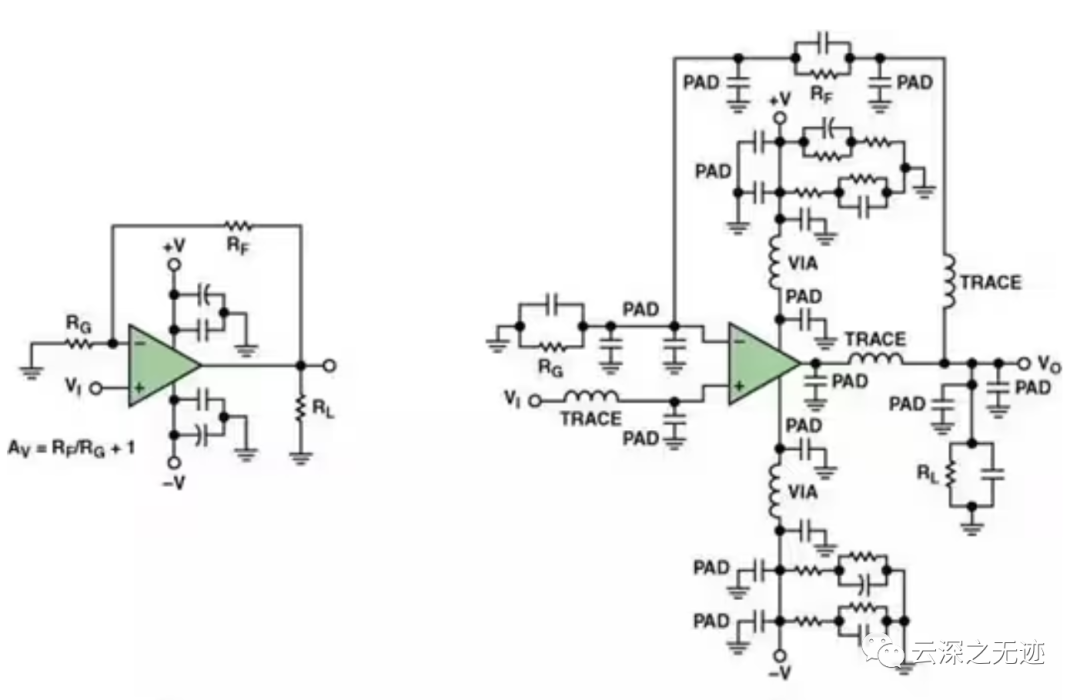

这个图是考虑寄生效应的

寄生效应就是那些溜进你的PCB并在电路中大施破坏、头痛令人、原因不明的小故障(按照字面意思)。它们就是渗入高速电路中隐藏的寄生电容和寄生电感。其中包括由封装引脚和印制线过长形成的寄生电感;焊盘到地、焊盘到电源平面和焊盘到印制线之间形成的寄生电容;通孔之间的相互影响,以及许多其它可能的寄生效应。图3(a)示出了一个典型的同相运算放大器原理图。但是,如果考虑寄生效应的话,同样的电路可能会变成图3(b)那样。

不要将过孔(Via)置于去耦电容和电源引脚之间。

过孔本身拥有一些寄生参数,会影响去耦电容的滤波效果。

对于双电源供电模式,在V+和V-之间接一个滤波电容,可以减少电路中的偶数次高次谐波。

电容器的电容值应该根据处理信号的频率按以下的标准确定(下列值是根据经验得出的)。

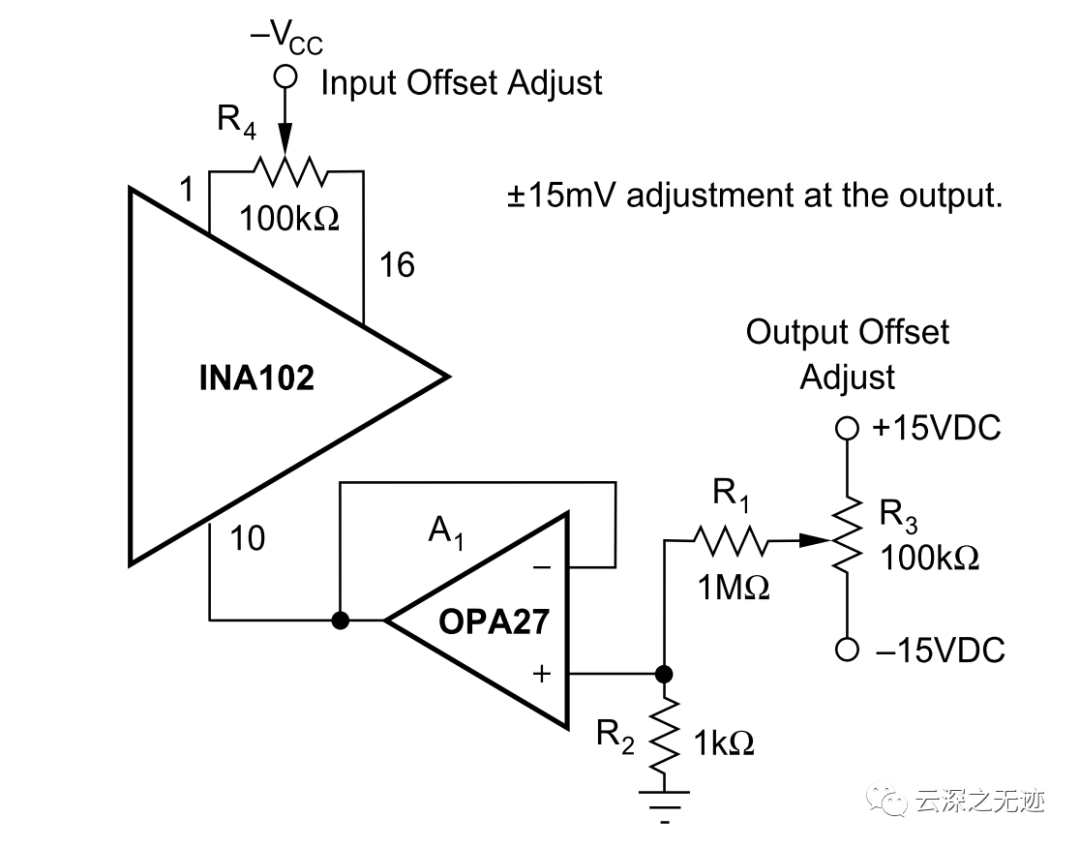

参考引脚缓冲电路定位在远离参考引脚的地方,这增加了连接到参考引脚的电阻,并为噪声和其他信号耦合到跟踪打开了可能性。

参考引脚上的附加电阻将降低大多数INAs提供的高共模抑制比(CMRR)。因此,将参考引脚缓冲电路尽可能靠近INA的参考引脚。

因为REF端并不需要大的输入电流,也不需要阻抗匹配,所以直接接参考电压就可以的。

1.对于电路中可能会出现大的开关电流的元件要尽量远离仪表放大器。

2.仪表放大器接地要放在远端,而把大电流的元件或频繁开关的元件放在接地的近端。

3.仪表放大器接地时加入耦合电容。

现在搬到南山了,变成了活不起的南山人

在工位就可以看到大家都喜欢的DJI-天空之城

今天是保研的日子,朋友圈又有不少保研的,哈哈哈,说不尽的羡慕。如果不是这帮人我可能去考个物理的研究生。我狠这种不公平,草你妈。

最后还是祝大家中秋快乐

在12点前吃到了月饼!

https://iam-tutu.blog.csdn.net/article/details/127818437?spm=1001.2101.3001.6650.1&utm_medium=distribute.pc_relevant.none-task-blog-2%7Edefault%7EBlogCommendFromBaidu%7ERate-1-127818437-blog-118079698.235%5Ev38%5Epc_relevant_sort_base3&depth_1-utm_source=distribute.pc_relevant.none-task-blog-2%7Edefault%7EBlogCommendFromBaidu%7ERate-1-127818437-blog-118079698.235%5Ev38%5Epc_relevant_sort_base3&utm_relevant_index=2http://www.china-fpc.com/NewsDetails-2181.htmlhttps://blog.csdn.net/qq_21794157/article/details/123277502https://murata.eetrend.com/article/2018-05/1001634.htmlhttps://blog.csdn.net/weixin_62179882/article/details/128941597