本文来自“2023新型算力中心调研报告(2023)”。更多内容参考“《海光CPU+DCU技术研究报告合集(上)》 ”,“《海光CPU+DCU技术研究报告合集(下)》 ”和“龙芯CPU技术研究报告合集”。

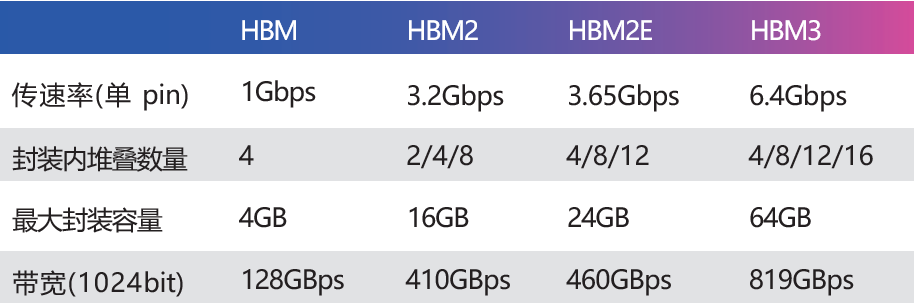

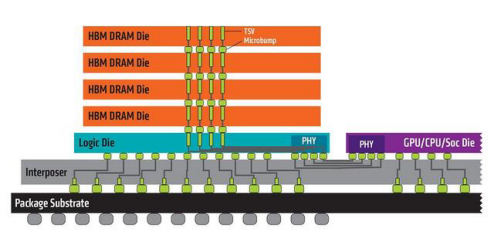

HBM(High Bandwidth Memory,高带宽内存)是 2014 年 AMD、SK海力士(SK Hynix)共同发布的,使用 TSV 技术将数个 DRAM Die(晶片)堆叠起来,大幅提高了容量和数据传输速率。

随后三星、美光、NVIDIA、Synopsys 等企业积极参与这个技术路线,标准化组织 JEDEC 也将 HBM2 列入标准(JESD235A),并陆续迭代了HBM2e(JESD235B)以及HBM3(JESD235C)。得益于堆叠封装,以及巨大的位宽(单封装 1024bit),HBM 提供了远超其他常见内存形态(DDR DRAM、LPDDR、GDDR 等)的带宽和容量。

典型的实现方式是通过 2.5D 封装将 HBM 与处理器核心连接,这在 CPU、GPU 等产品中均有应用。早期也有观点把 HBM 视作 L4 Cache,从 TB/s 级的带宽角度看,也算合理。而从容量角度,HBM 就比 SRAM 或 eDRAM 大太多了。由此,HBM 既可以胜任(一部分)的工作,也可以当做高性能内存使用。

AMD 是 HBM 的早期使用者,发展至今,AMD Instinct MI250X 计算卡在单一封装内集成了 2 颗计算核心和 8 颗 HBM2e,容量共 128GB,带宽达到 3276.8GB/s。

NVIDIA 应用 HBM 的主要是专业卡,其 2016 年的 TESLA P100 的 HBM 版搭配了 16GB HBM2,随后的 V100 搭配了 32GB HBM2。目前当红的 A100 和 H100 也都有 HBM 版,前者最大提供 80GB HBM2e、带宽约 2TB/s;后者升级到 HBM3,带宽约 3.9TB/s。

华为的昇腾 910 处理器也集成了 4 颗 HBM。对于计算卡、智能网卡(SmartNIC)、高速 FPGA 等产品,HBM 作为一种 GDDR 的替代品,应用已经非常成熟了。

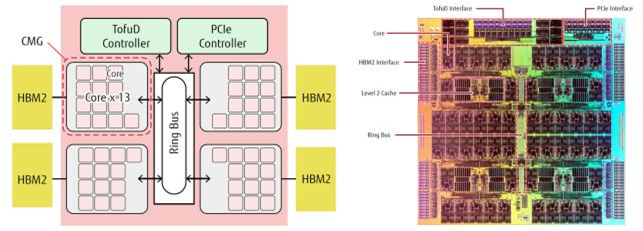

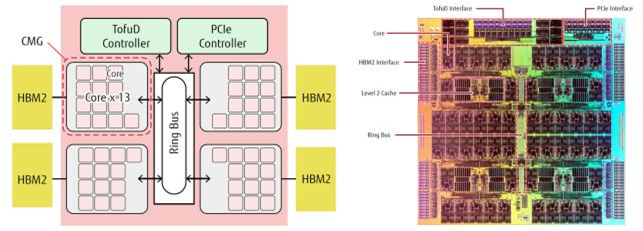

CPU 也已开始集成 HBM,其中最突出的案例是曾经问鼎超算 TOP500 的富岳(Fugaku),使用富士通研发的 A64FX 处理器。A64FX 基于 Armv8.2-A,采用 7nm 制程,每封装内集成了 4 颗 HBM2,容量 32GB,带宽 1TB/s。

△ 富士通 A64FX CPU

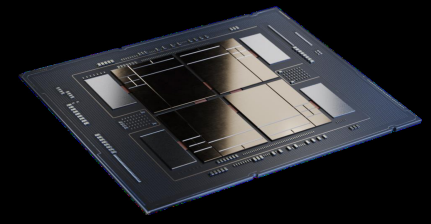

英特尔在 2023 年 1 月中与第四代至强可扩展处理器一同推出的至强 Max 系列,在前者的基础上集成了 64GB 的 HBM2e。这些 HBM2e 可以作为内存独立使用(HBM Only 模式),也可以搭配 DDR5 内存共同使用(HBM Flat Mode 和 HBM Caching Mode 两种工作模式)。

△ Intel Xeon Max 系列,注意外围的 4 颗 HBM 芯片

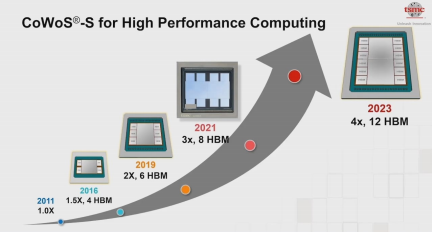

中介层:CoWoS 与 EMIB

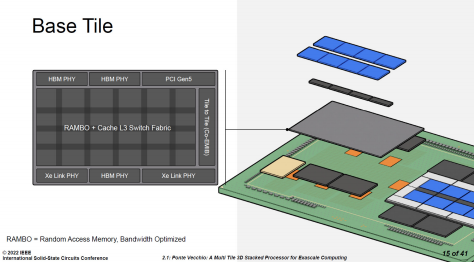

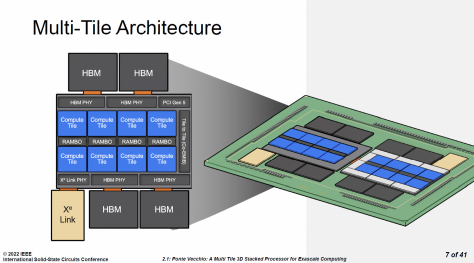

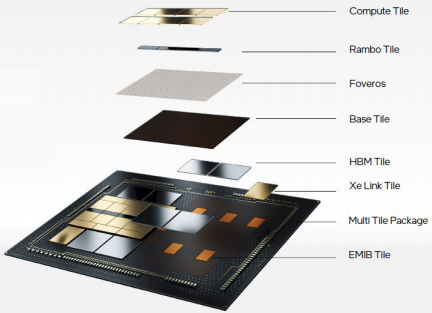

英特尔数据中心 Max GPU 系列引入了 Base Tile的概念,姑且称之为基础芯片。相对于中介层的概念,我们也可以把基础芯片看作是基础层。基础层表面上看与硅中介层功能类似,都是承载计算核心、高速 I/O(如 HBM),但实际上功能要多得多。硅中介层的本质是利用成熟的半导体光刻、沉积等工艺(65nm 等级),在硅上形成超高密度的电气连接。而基础层更进一步:既然都要加工多层图案,为什么不把逻辑电路之类的也做进去呢?

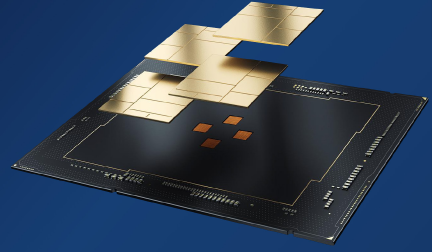

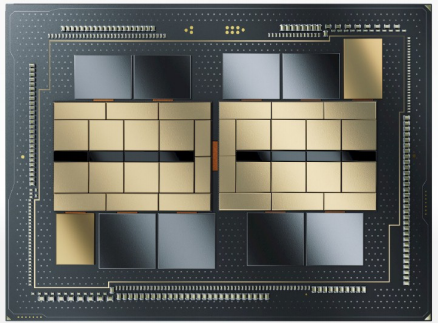

△ 英特尔数据中心 Max GPU

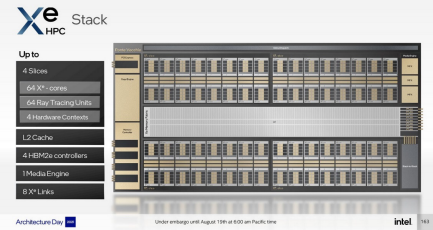

Intel 在 ISSCC2022 中展示了英特尔数据中心 Max GPU 的Chiplet(小芯片)架构,其中,基础芯片面积为 640mm²,采用了 Intel 7 制程——这是目前Intel用于主流处理器的先进制程。为何在“基础”芯片上就需要使用先进制程呢?因为 Intel 将高速 I/O 的 SerDes 都集成在基础芯片中了,其作用有点儿类似 AMD 的 IOD。这些高速 IO 包括 HBM PHY、Xe Link PHY、PCIe 5.0,以及,这一节的重点:Cache。这些电路都比较适合 5nm 以上的工艺制造,将它们与计算核心解耦后重新打包在一个制程之内是相当合理的选择。

△ 英特尔数据中心Max GPU的基础芯片。注意,此图中的两组 Xe Link PHY应为笔误。芯片下方应为两个 HBM PHY 和一个Xe Link PHY

英特尔数据中心 Max GPU 系列通过 Foveros 封装技术在基础芯片上方叠加 8 颗计算芯片(Compute Tile)、4 颗 RAMBO 芯片(RAMBO Tile)。计算芯片采用台积电 N5 工艺制造,每颗芯片都自有 4MB L1 Cache。RAMBO是“Random Access Memory, Bandwidth Optimized”的缩写,即为带宽优化的随机访问存储器。独立的 RAMBO 芯片基于 Intel 7 制程,每颗有 4 个 3.75MB 的 Bank,共 15MB。每组 4 颗 RAMBO 共提供了 60MB 的 L3 Cache。此外,在基础芯片中也有 RAMBO,容量有 144MB,外加 L3 Cache 的交换网络(Switch Fabric)。

△ 英特尔数据中心 Max GPU 的 Chiplet 架构

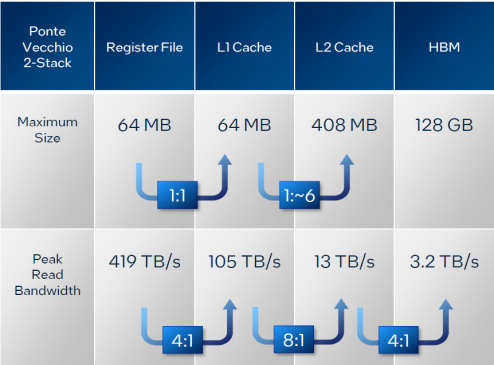

因此,在英特尔数据中心 Max GPU 中,基础芯片通过了 Cache 交换网络,将基础层内的 144MB Cache,与 8 颗计算芯片、4 颗 RAMBO 芯片的 60MB Cache 组织在一起,总共 204MB L2/L3 Cache,整个封装是两组,就是 408MB L2/L3 Cache。

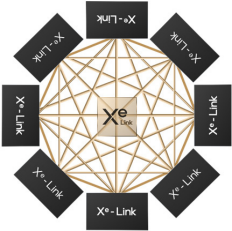

英特尔数据中心 Max GPU 的每组处理单元都通过 Xe Link Tile 与另外 7 组进行连接。Xe Link 芯片采用台积电 N7 工艺制造。

△ Xe HPC 的逻辑架构

△ Xe Link 的网状连接

前面已经提到,I/O 芯片独立是大势所趋,共享 Cache 与 I/O 拉近也是趋势。英特尔数据中心 Max GPU 将 Cache 与各种高速 I/O 的 PHY 集成在同一芯片内,正是前述趋势的集大成者。至于 HBM、Xe

Link 芯片,以及同一封装内相邻的基础芯片,则通过 EMIB(爆炸图中的橙色部分)连接在一起。

△ 英特尔数据中心Max GPU爆炸图

根据英特尔在 HotChips 上公布的数据,英特尔数据中心 Max GPU 的 L2 Cache 总带宽可以达到 13TB/s。考虑到封装了两组基础芯片和计算芯片,我们给带宽打个对折,基础芯片和 4 颗 RAMBO 芯片的带宽是 6.5TB/s,依旧远远超过了目前至强和 EPYC 的 L2、L3 Cache 的带宽。其实之前 AMD 已经通过了指甲盖大小的 3D V-Cache 证明了 3D 封装的性能,那就更不用说英特尔数据中心 Max GPU 的 RAMBO 及基础芯片的面积了。

△ 英特尔数据中心Max GPU的存储带宽

回顾一下 3D V-Cache 的弱点——“散热”不良,我们还发现将 Cache 集成到基础芯片当中还有一个优点:将高功耗的计算核心安排在整个封装的上层,更有利于散热。再往远一些看,在网格化的处理器架构中,L3 Cache 并非简单的若干个块(切片),而是分成数十甚至上百单元,分别挂在网格节点上的。基础芯片在垂直方向可以完全覆盖(或容纳)处理器芯片,其中的 SRAM 可以分成等量的单元与处理器的网格节点相连。

换句话说,对于网格化的处理器,将 L3 Cache 移出到基础芯片是有合理性的。目前已经成熟的 3D 封装技术的凸点间距在 30~50 微米的量级,足够胜任每平方毫米内数百至数千个连接的需要,可以满足当前网格节点带宽的需求。更高密度的连接当然也是可行的,10 微米甚至亚微米的技术正在推进当中,但优先的场景是 HBM、3D NAND 这种高度定制化的内部堆栈的混合键合,未必适合 Chiplet 对灵活性的要求。

人工智能专题报告:智算中心—赋能AI产业化、产业AI化(2023)

多样性算力:新一代计算架构超异构计算

聚力“高广深”打造先进算力网络

生成式AI:产业变革与机会(2023论坛合集)

《“东数西算”技术分析合集》

《2023年液冷技术白皮书汇总》

世界AI大会系列:数据为核,迈向多模态AI大模型时代

本号资料全部上传至知识星球,更多内容请登录智能计算芯知识(知识星球)星球下载全部资料。

免责申明:本号聚焦相关技术分享,内容观点不代表本号立场,可追溯内容均注明来源,发布文章若存在版权等问题,请留言联系删除,谢谢。

温馨提示:

请搜索“AI_Architect”或“扫码”关注公众号实时掌握深度技术分享,点击“阅读原文”获取更多原创技术干货。