前言

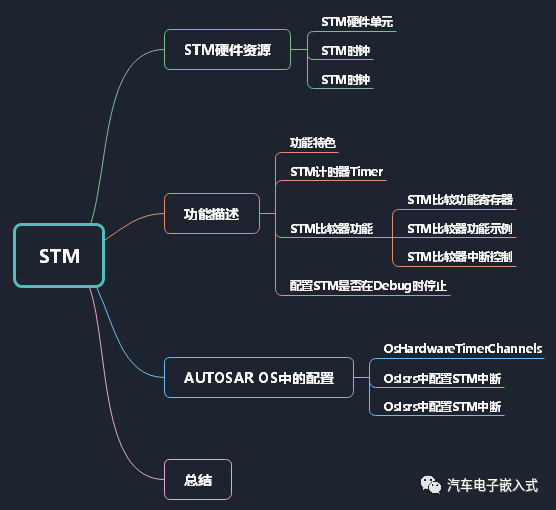

基于Aurix芯片的Davinci工具链的MICROSAR OS的系统Counter(系统心跳)使用的硬件时钟STM(System Timer),在学习OS前有必要了解下Aurix芯片的STM模块。本文就来详细介绍下Aurix芯片的STM模块。

缩略词

简写 | 全称 |

STM | System Timer |

CMCON | Compare Match Control Register |

参考文档:

1. TriCoreTM TC1.6.2 core architecture manual

2. AURIXTC3XX_um_part1_v2.0.pdf

3. TC37x_appx_um_v2.0.pdf

注:本公众号文章中使用了一些第三方工具和文档,若有侵权,请联系作者删除!

正文

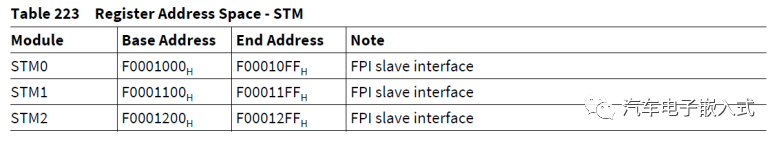

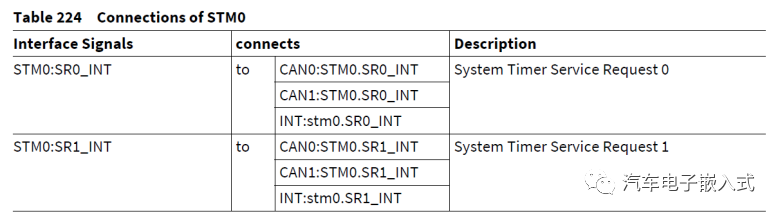

TC37x芯片有3个STM模块,每个STM模块可以产生两个SRx_INT中断信号(通过STM模块的Compare功能实现,下文介绍),Davinci OS中的硬件定时器就是使用STM模块的SRx_INT中断信号。

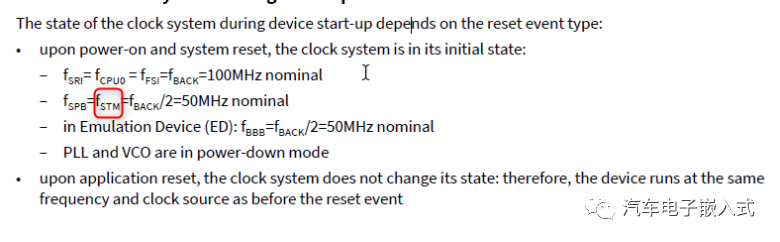

系统冷启动或者系统复位后,fSTM=50MHz,也就是fSTM的一个tick为1/(50*(10^6)) = 0.00000002 s = 20ns.

Note: TC37x的时钟系统后面的文章再介绍,本文默认系统启动后fSTM就为50MHz.

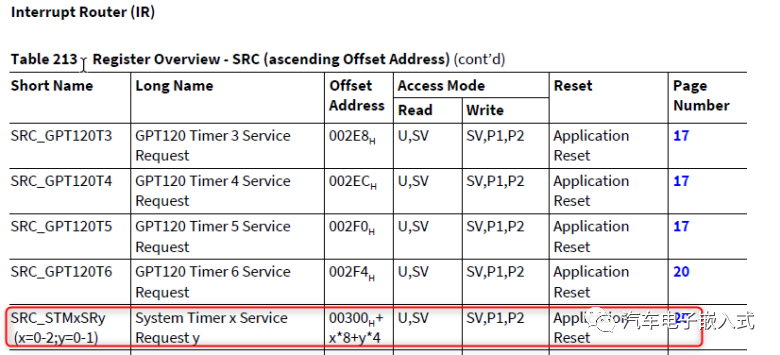

在1.1章节中介绍了TC37x有3个STM硬件单元,每个STM硬件单元可以产生两个中断信号,中断号计算公式如下截图所示:

e.g. STM0的SR0_INT = 0x300 + 0*8 + 0*4 = 0x300 = 768.

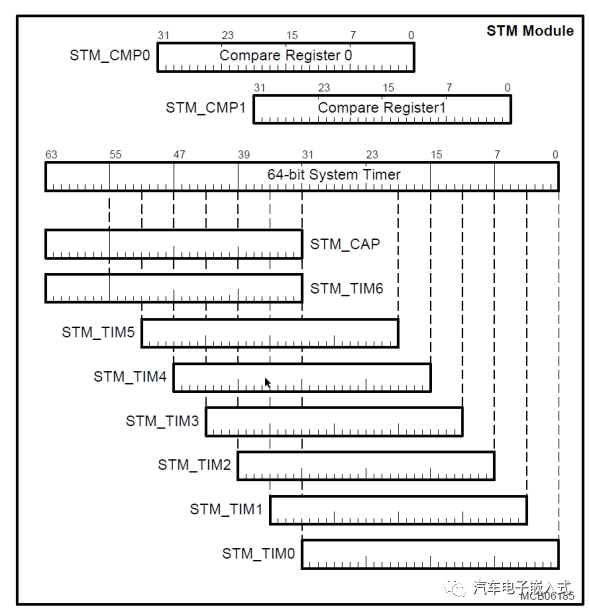

一个不受约束的64-bit计数器,也就是能产生一个0 – 2^64的计数,如果我们使用fSTM = 50MHz,那么计数器的最大计数值对应的最大时间为:2^64 * 20ns = 4270079.647..天 = 11698 年,也就说实际使用中这个计数器不可能溢出。

这个64b-bit计数器可以同步读出。理论上,TC37x是32-bit系统,每个指令周期顶多能读32-bit数据,TC37x芯片是怎么保证64-bit计时器值同步读出来的了?-- 通过STM_CAP寄存器机制,后面介绍。

64 位计数器的不同 32 位部分可以同步读取。STM的64-bit提供了6个32-bit Timer可以同步读出来,后文介绍。

基于与部分 STM 内容的比较匹配,灵活地生成服务请求。通过STM_CMPx的比较机制灵活的产生服务请求事件,后文具体介绍。

系统启动后,STM自动启动。

如果ARSTDIS.STMxDIS被清除,则Application Reset也会Reset STM registers;如果ARSTDIS.STMxDIS没有被清除,则Application Reset不会Reset STM registers,只有System Reset才会Reset STM registers.

STM作为Timer时,可以提供7个不同基准的Timer:

STM_TIM0: 基准为2^0 tick = 1 tick = 20 ns,也就是每20 ns,计数器加1.

STM_TIM1: 基准为2^4 tick = 16 tick = 320 ns,…

STM_TIM2: 基准为2^8 tick = 256 tick = 5120 ns = 5.120 us,…

STM_TIM3: 基准为2^12 tick = 4096 tick = 81920 ns = 81.92 us,…

STM_TIM4: 基准为2^16 tick = 65536 tick = 1310720 ns = 1.31072 ms,…

STM_TIM5: 基准为2^20 tick = 1048576 tick = 209715220 ns = 0. 20971522 s,…

STM_TIM6: 基准为2^32 tick = 4294967296 tick = 85899345920 ns = 85.899345920 s,…

理论上,TC37x是32-bit系统,每个指令周期顶多能读32-bit数据且在读取32-bit数据的时候STM是不会停下来等你再读另一个32-bit的数据的,TC37x芯片是怎么保证64-bit计时器值同步读出来的了?-- 通过STM_CAP寄存器机制,每次读取其中一个寄存器 TIM0 至 TIM5 时,它都会锁定 STM 高部分的内容。因此,在读取下部时, CAP 完全同时保存计时器的上限值。然后,第二个读取操作将读取 CAP 的内容以获得完整的计时器值。

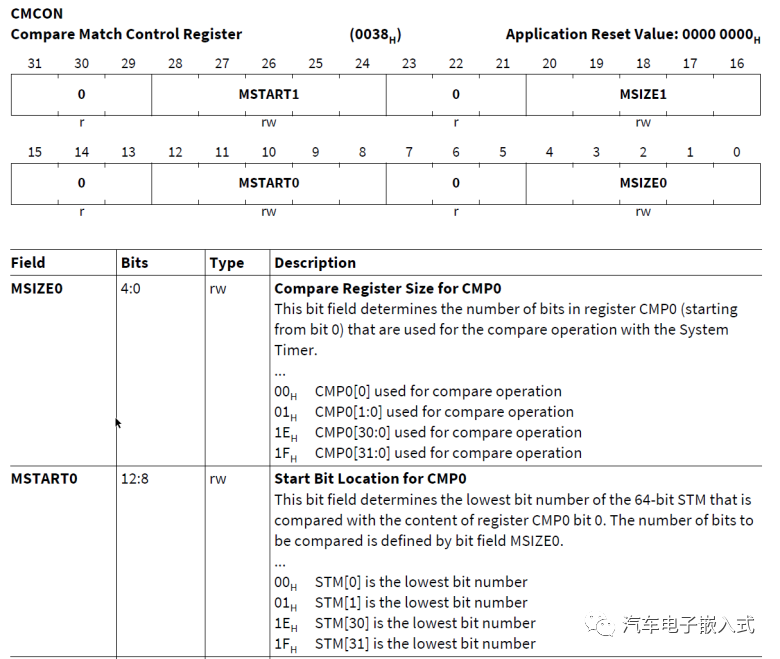

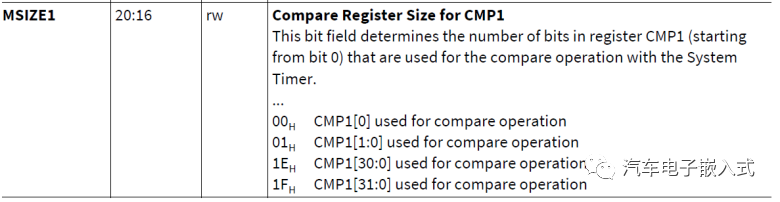

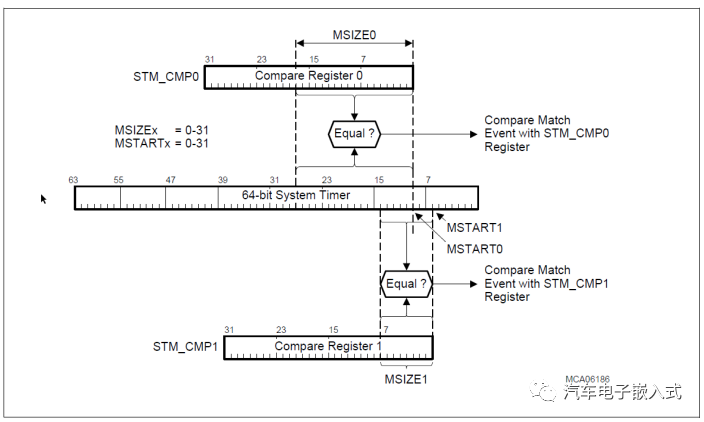

64 位系统计时器的内容可以与 CMP0 和 CMP1 寄存器中存储的两个比较值的内容进行比较。服务请求可以在 STM 与 CMP0 或 CMP1 寄存器的比较匹配上生成。

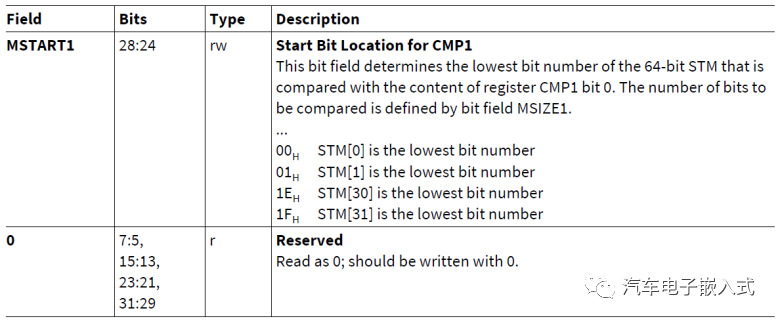

CMCON(Compare Match Control Register)寄存器的MSIZEx位域配置CMPx寄存器从0-bit开始多少位用来和STM比较,MSTARTx位域配置STM Counter的哪一位开始和CMPx寄存器比较。

如下图所示,对应的CMCOM的配置为:

MSIZE0 = 10001B = 17D; MSTART0 = 01010B = 10D

MSIZE1 = 00111B = 7D; MSTART1 = 00111B = 7D

MSIZE0 = 10001B = 17D : Compare Register0从0-bit开始的7个bit用于比较

MSTART0 = 01010B = 10D : 和STM的第10-bit位开始的7个bit比较

CMP1类似……

Compare成功后,就会产生Event,Event可用于配置中断。

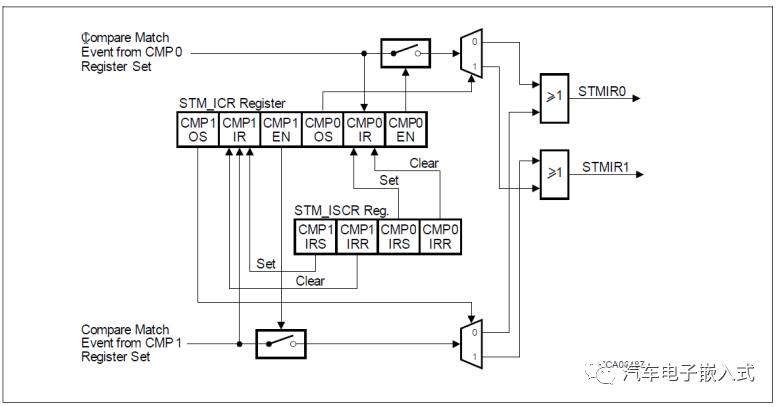

Compare中断事件产生举例:

第1步:配置STMx_CMCON. MSTARTx位域,设置比较寄存器在STM中的起始位置

第2步:配置STMx_CMCON.MSIZEx使用STM_CMPx的宽度(多少bit)

第3步:配置STM_CMPx. CMPVAL[31:0]定时器值

第4步:配置STM_ICR.CMPxOS到时触发STMIR0还是STMIR1中断

第5步:配置STM_ICR.CMPxEN使能中断,等待定时中断触发

中断触发后:在中断服务例程(ISR,中断服务函数)里设置STM_ISCR.CMPxIRR=1清除中断,并重复上述第5步操作重新使能中断,等待中断触发

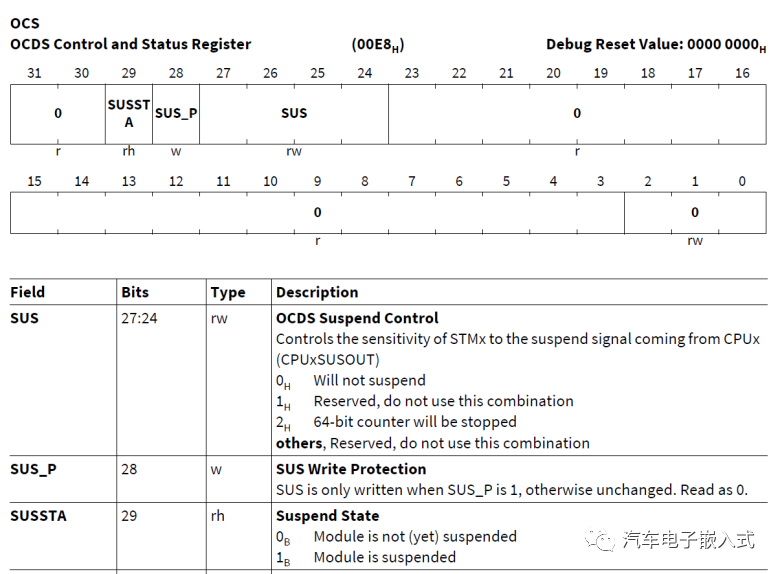

OCS. SUS[27:24]位域配置为0时,STM计时不会被外部调试器的操作打断; OCS. SUS[27:24]位域配置为2, 在使用调试器Stop程序的时候,STM会同步Stop计时。

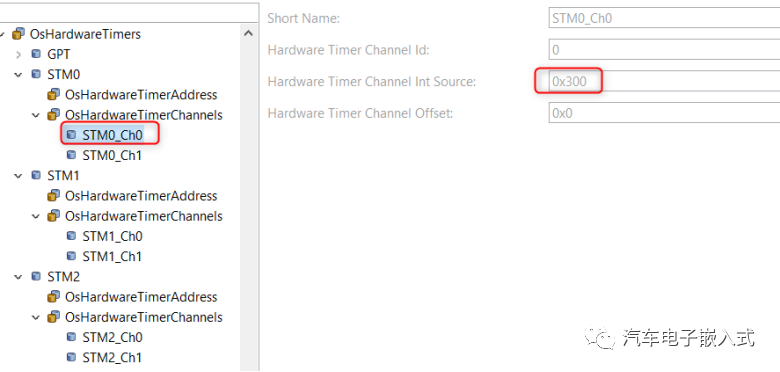

Davinci的SIP包中硬件相关的配置都是默认配置好,TC37x芯片有三个STM定时器,每个STM有两个通道(也就每个STM能产生两个中断事件)。

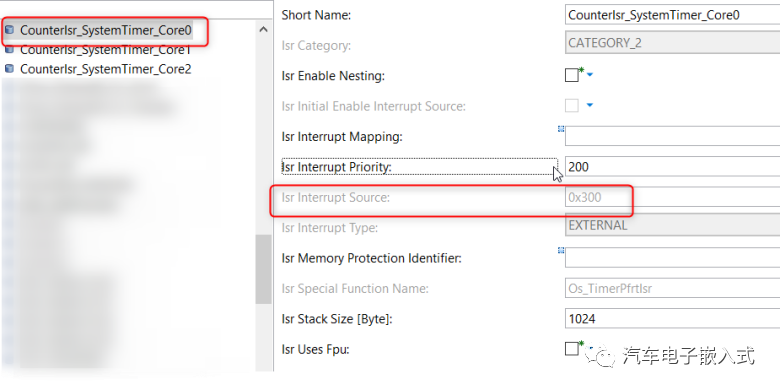

OsIsrs中关于STM产生的中断也是默认配置好的,使用三个STM的Channel0通道。

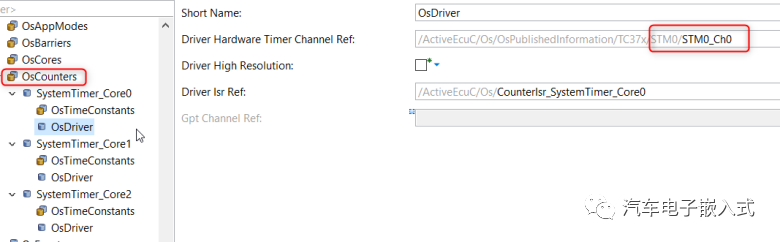

OsCounsters使用硬件定时器STM,需要引用STM的配置。

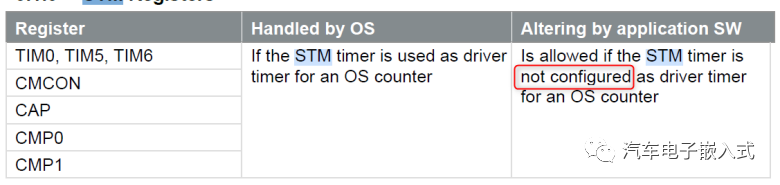

STM一般用作Os的Timer,如果OS中配置使用了STM,那么应用就不能再使用了。具体怎么使用,那就是Os的静态代码实现的了。作为学习,我们理解了STM的Compare Operation机制就能去阅读Os是怎么配置寄存器实现Timer功能的了。

End

「汽车电子嵌入式在CSDN上同步推出AUTOSAR精进之路专栏,本专栏每个模块完全按实际项目中开发及维护过程来详细介绍。模块核心概念介绍、实际需求描述、实际工程配置、特殊需求介绍及背后原理、实际工程使用经验总结。目的是让读者看完每一个章节后能理解原理后根据需求完成一个模块的配置或者解决一个问题。」

点击文章最后左下角的阅读原文可以获取更多信息

或者复制如下链接到浏览器获取更多信息

https://blog.csdn.net/qq_36056498/article/details/132125693

注:本公众号文章中使用了一些第三方工具和文档,若有侵权,请联系作者删除!

推荐阅读

汽车电子嵌入式精彩文章汇总第一期:20210530-20230703

AUTOSAR 架构下EcuM唤醒源事件详解

AUTOSAR架构下NVM Block连续写及Default Value问题分析

AUTOSAR架构下NvM模块详细分析

AUTOSAR架构下报文掉线超时不上报问题分析

Classic Autosar下的以太网通讯架构概览

通信中间件Someip服务化通信

AUTOSAR架构下Fee详细分析

TC37x芯片FLASH基本概念介绍

AUTOSAR架构下Fls详细分析

TC3xx芯片DMU介绍

TC3xx芯片MPU介绍

End

欢迎点赞,关注,转发,在看,您的每一次鼓励,都是我最大的动力!

汽车电子嵌入式

微信扫描二维码,关注我的公众号