TI家的精密运放都是用的同一个小板子,以前写过,浮在表面,做的时候才发现一地鸡毛。

PCB学习-差分走线

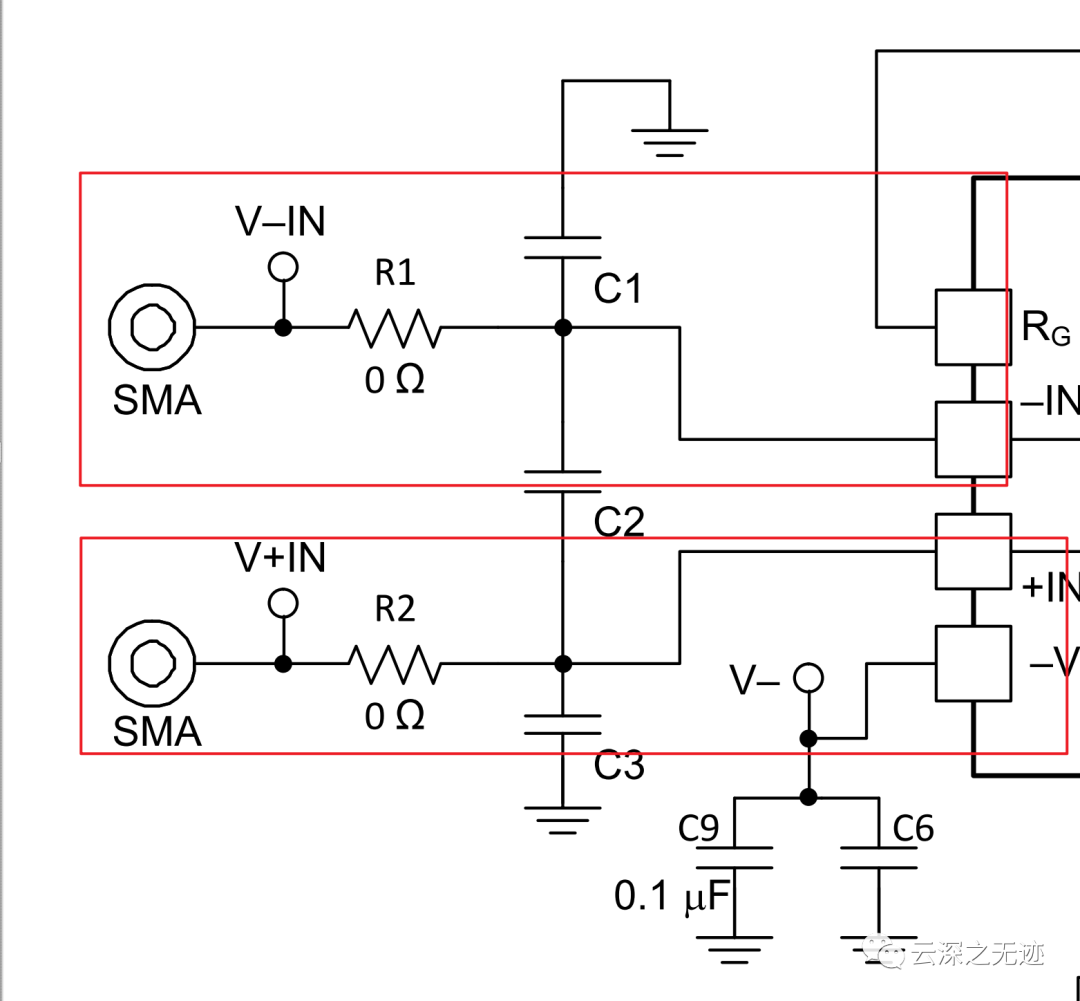

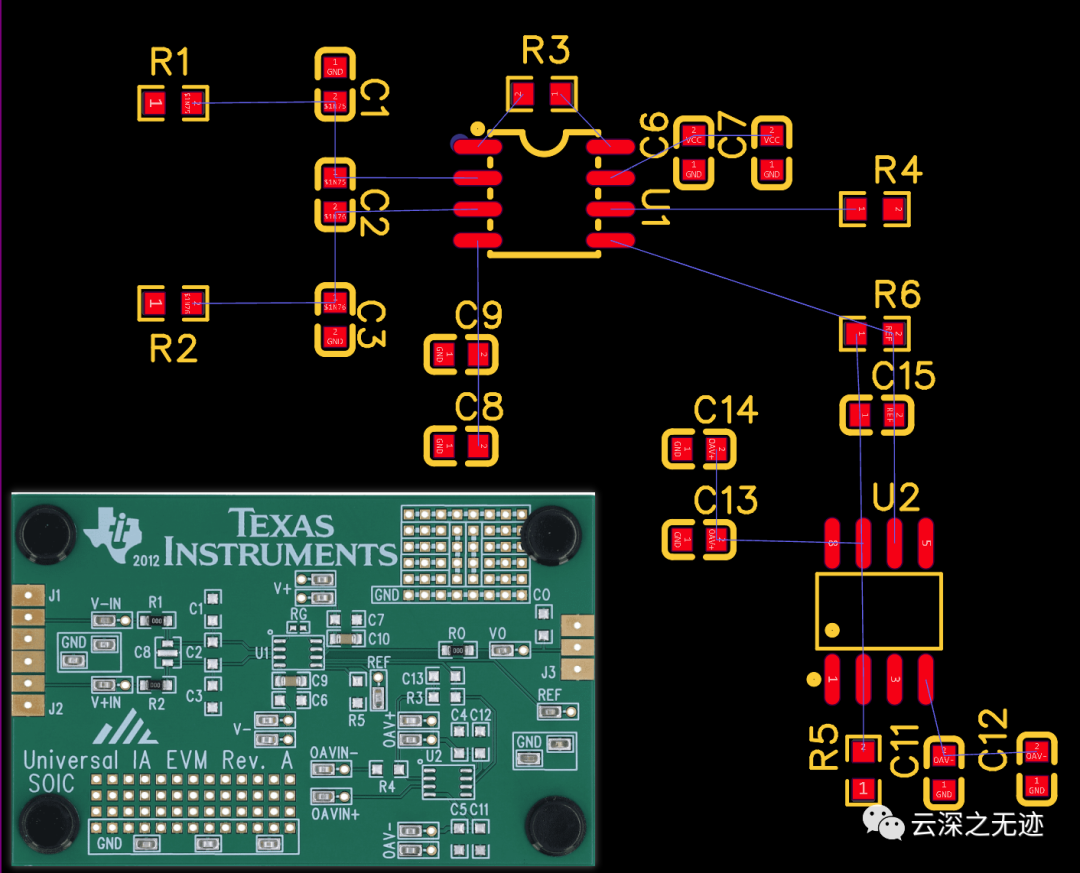

通用仪表放大器 EVM

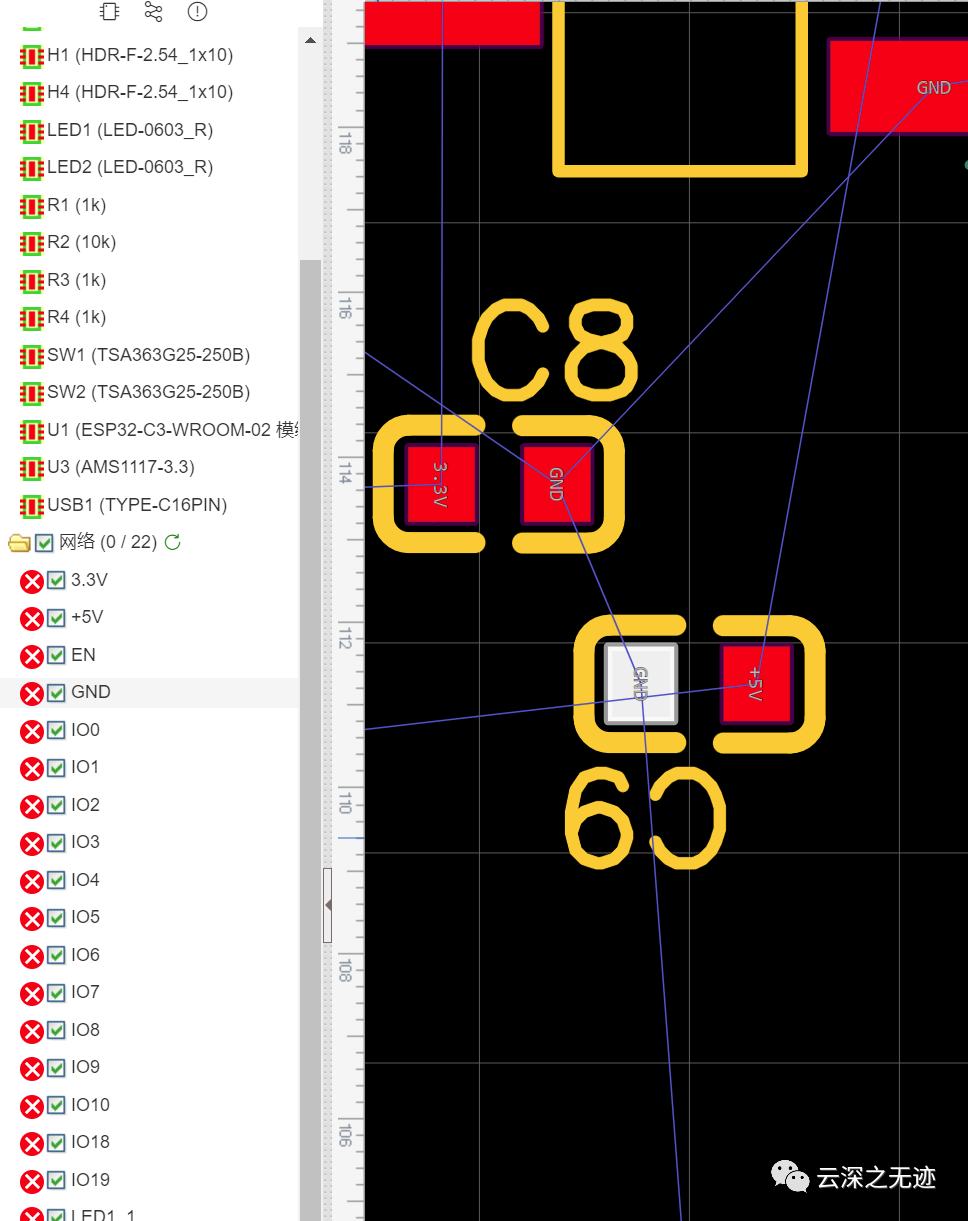

使用的是JLC的专业版,普通版的功能确实是有点问题,而且很影响体验,还有就是建议两快屏幕,一块真的不够用。

板子的话,低速的线应该俩层都能布完,有个呆逼51搞4层板,直接叉出去。

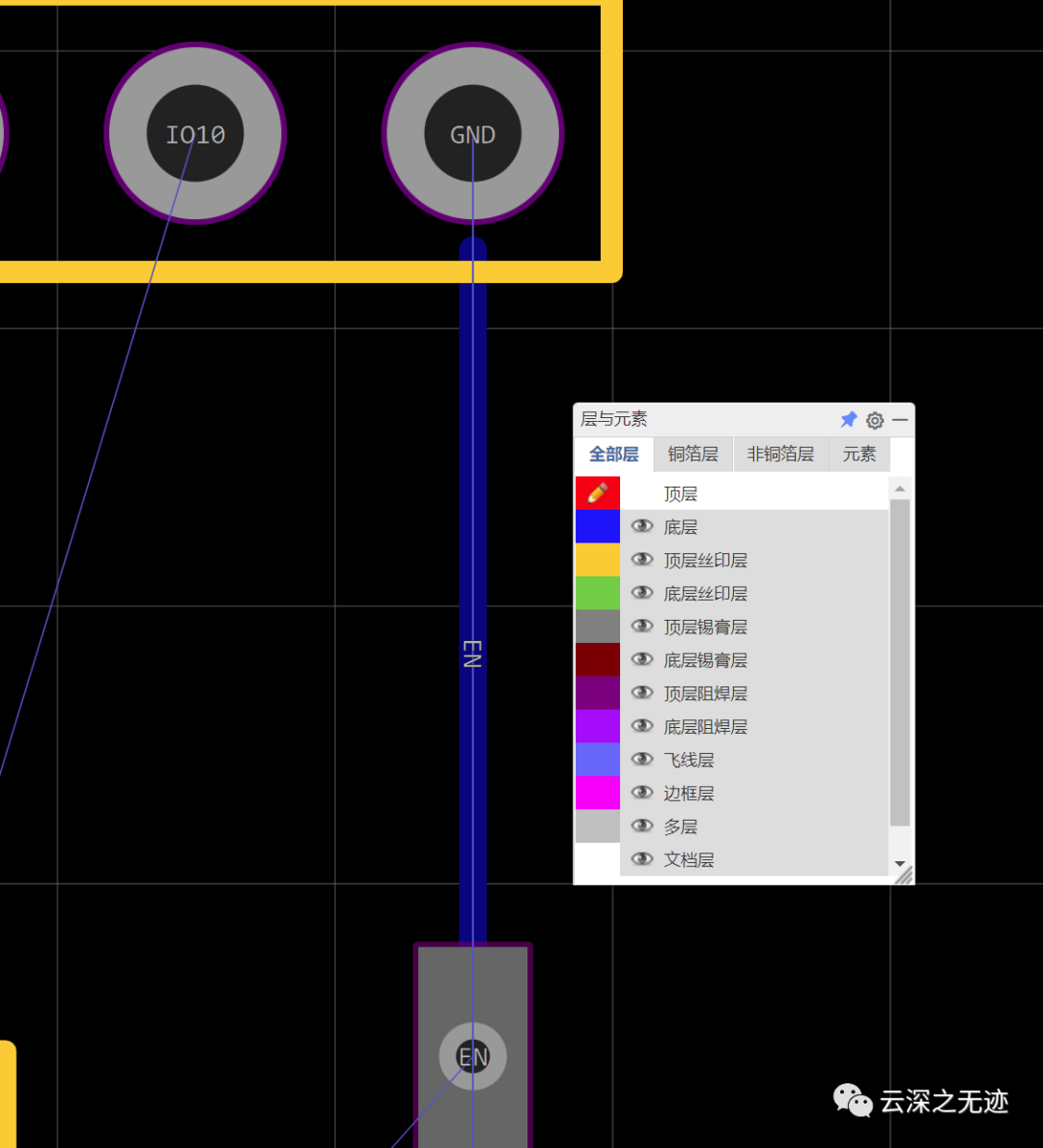

下面就是一些基础的知识了,不知道就起步不了。

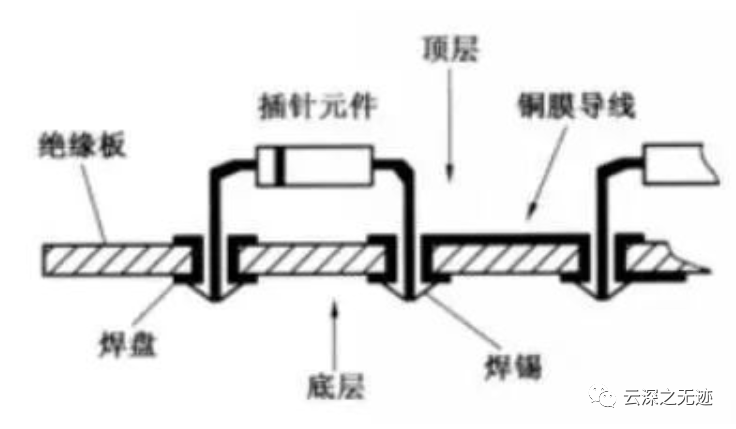

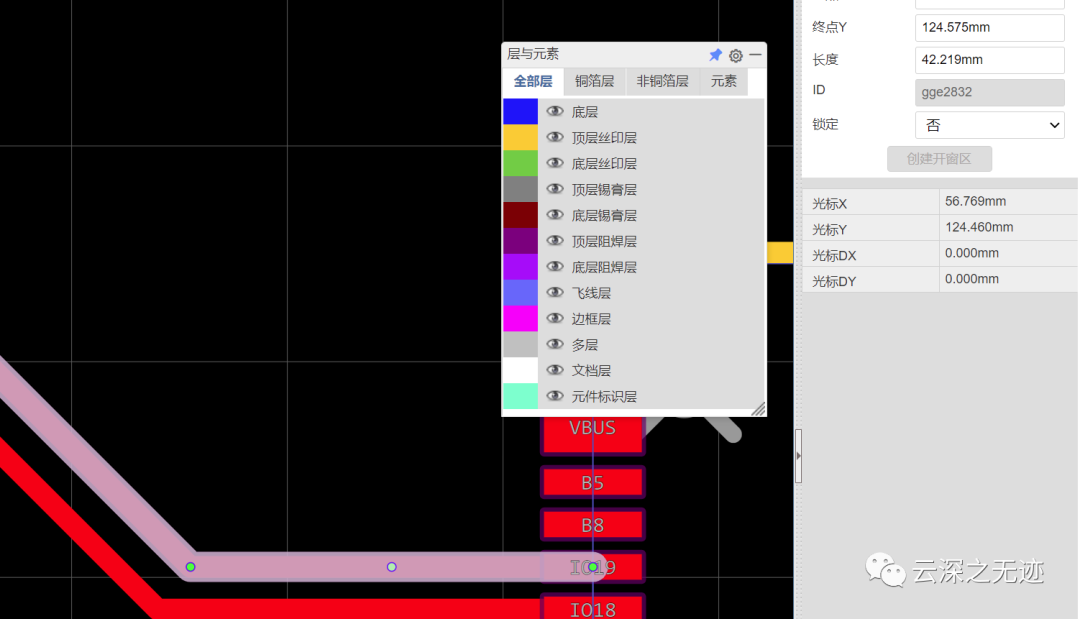

顶层/底层:PCB板子顶面和底面的铜箔层,信号走线用。

内层:铜箔层,信号走线和铺铜用。可以设置为信号层和内电层。

顶层丝印层/底层丝印层:印在PCB板的白色字符层。

顶层锡膏层/底层锡膏层:该层是给贴片焊盘制造钢网用的层,帮助焊接,决定上锡膏的区域大小。做的板子不需要贴片的话这个层对生产没有影响。也称为正片工艺时的助焊层。

顶层阻焊层/底层阻焊层:板子的顶层和底层盖油层,一般是绿油,绿油的作用是阻止不需要的焊接。该层属于负片绘制方式,当你有导线或者区域不需要盖绿油则在对应的位置进行绘制,PCB在生成出来后这些区域将没有绿油覆盖,方便上锡等操作,该动作一般被称为开窗。

边框层:板子形状定义层。定义板子的实际大小,板厂会根据这个外形进行生产板子。生成的制造文件Gerber会生成在 GKO 文件。

顶层装配层/底层装配层:元器件的简化轮廓,用于产品装配和维修。用于导出文档打印,不对PCB板制作有影响。

机械层:记录在PCB设计里面在机械层记录的信息,仅做信息记录用。

生产时默认不采用该层的形状进行制造。

一些板厂再使用AD文件生产时会使用机械层做边框,在嘉立创EDA,该层不影响板子的边框形状,该层仅做文字标识用。比如:工艺参数;V割路径等。

如果机械层有闭合的导线,嘉立创在生产板子的时候会优先使用机械层作为板子形状,如果没有机械层的外框才会使用 GKO 作为边框(AD文件的历史影响),需要注意在设计的时候注意机械层的使用。

文档层:与机械层类似。但该层仅在编辑器可见,生成在Gerber文件里不参与制造生产。

飞线层:PCB网络飞线的显示,这个不属于物理意义上的层,为了方便使用和设置颜色,故放置在层管理器进行配置。

孔层:与飞线层类似,这个不属于物理意义上的层只做通孔(非金属化孔)的显示和颜色配置用。

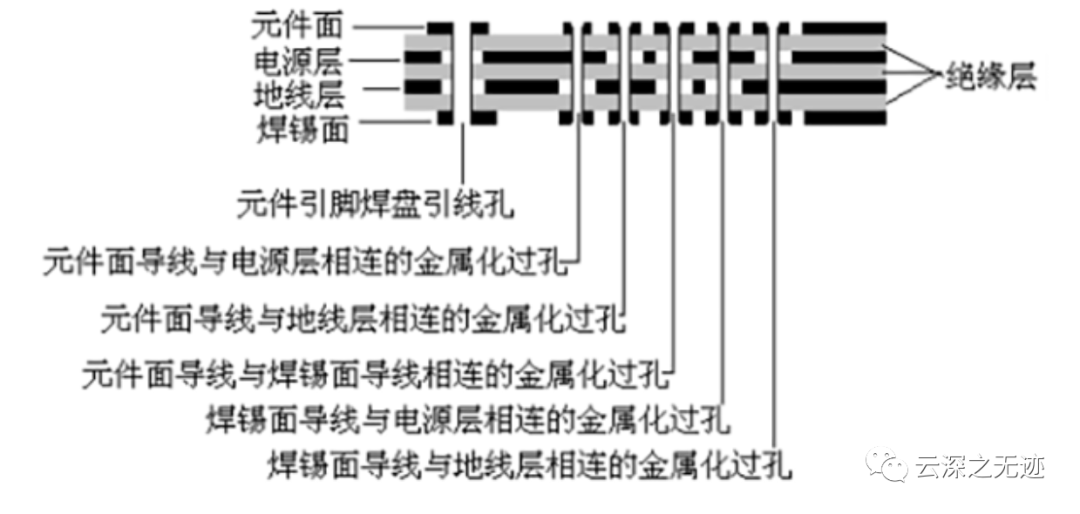

多层:与飞线层类似,金属化孔的显示和颜色配置。当焊盘层属性为多层时,它将连接每个铜箔层包括内层。

错误层:与飞线层类似,为DRC(设计规则错误)的错误标识显示和颜色配置用。

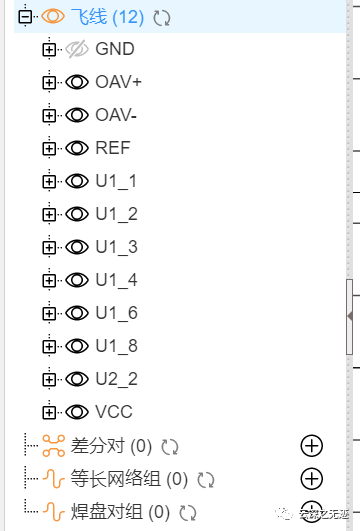

布线生成

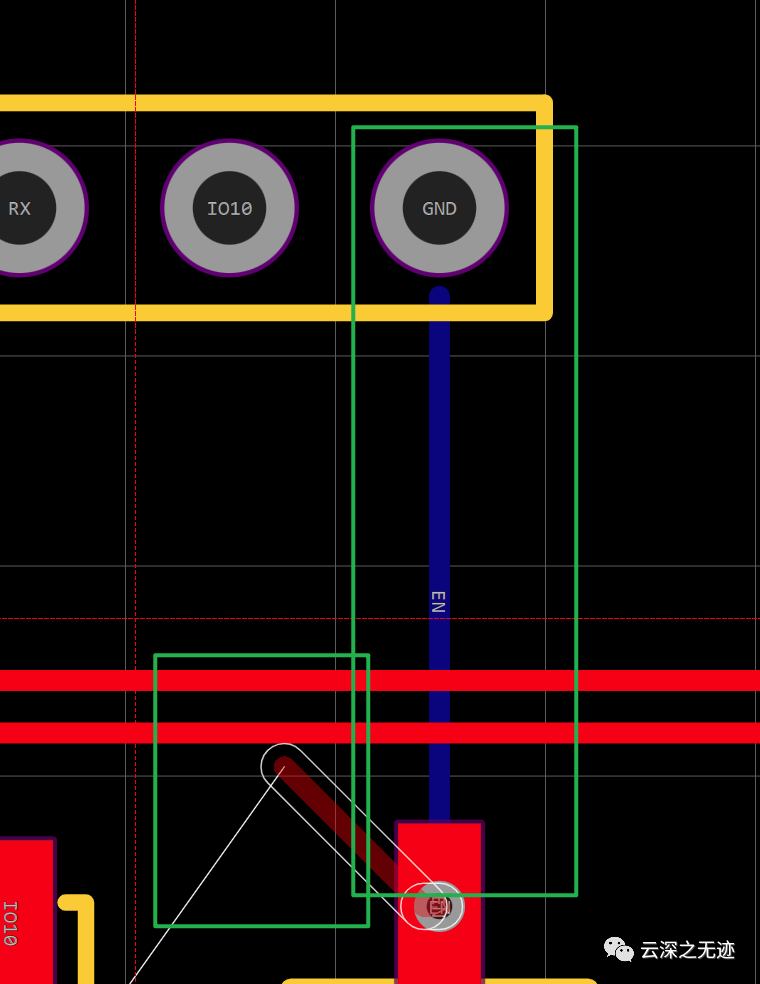

关掉表面的丝印

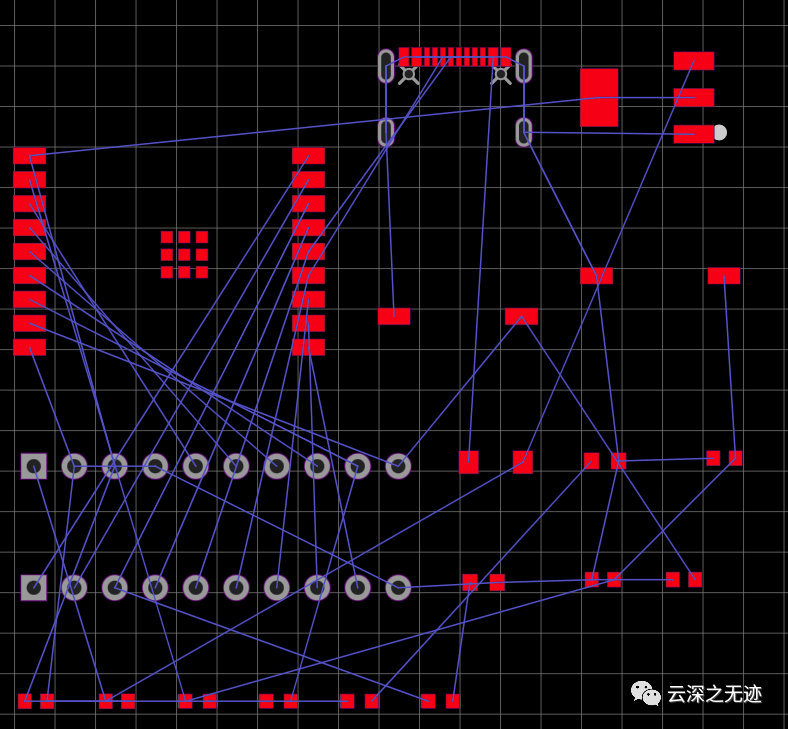

飞线关闭

双面板是包括Top(顶层)和Bottom(底层)的双面都敷有铜的印制电路板,双面都可以布线焊接,中间为一层绝缘层,为常用的一种印制电路板。两面都可以走线,大大降低了布线的难度,因此被广泛采用。

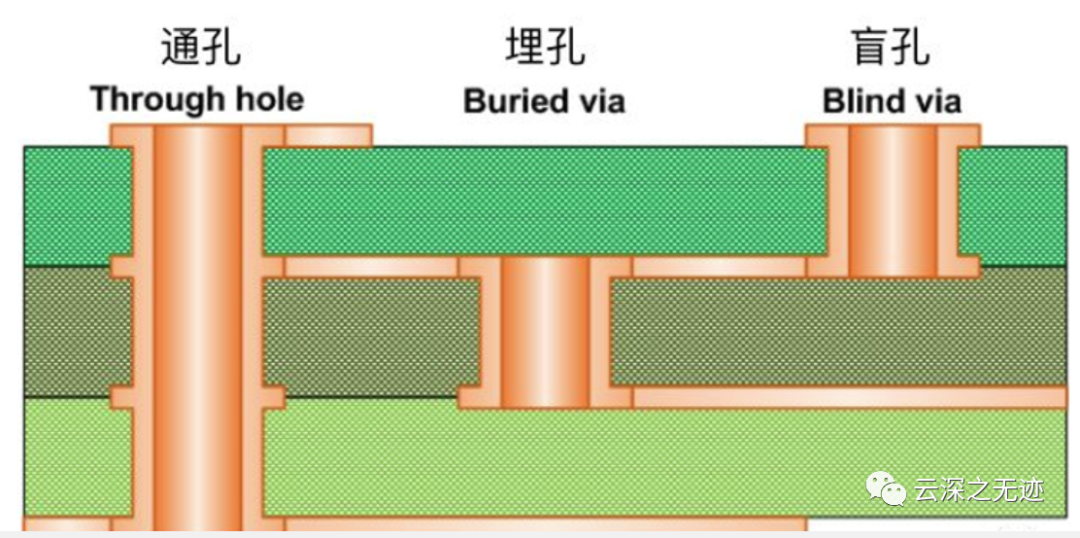

盲孔:就是将PCB中的最外层电路与邻近内层以电镀孔来连接,因为看不到对面,所以称为盲通。同时为了增加PCB电路层间的空间利用,盲孔就应用上了。也就是到印制板的一个表面的导通孔。特点:盲孔位于电路板的顶层和底层表面,具有一定的深度,用于表层线路和下面的内层线路的链接,孔的深度通常不超过一定的比率(孔径)。这种制作方式就需要特别注意钻孔的深度(Z轴)要恰到好处,不注意的话会造成孔内电镀困难所以几乎无厂采用,也可以把事先需要连通的电路层在个别电路层的时候就先钻好孔,最后再黏合起来,可是需要比较精密的定位及对位装置。

埋孔,就是PCB内部任意电路层间的链接但未导通至外层,也是未延伸到电路板表面的导通孔意思。特点:在这个制程无法使用黏合后钻孔的方式达成,必须要在个别电路层的时候就执行钻孔,先局部黏合内层之后还的先电镀处理,最后才能全部黏合,比原来的导通孔和盲孔要更费工夫,所以价钱也是最贵的。这个制程通常只使用於高密度的电路板,来增加其他电路层的可使用空间在PCB生产工艺中,钻孔是非常重要的,不可马虎。因为钻孔就是在覆铜板上钻出所需要的过孔,用以提供电气连接,固定器件的功能。如果操作不当,过孔的工序出现了问题,器件不能固定在电路板上面,轻则影响使用,重则整块板子都要报废掉,所以钻孔这个工序是相当重要的。

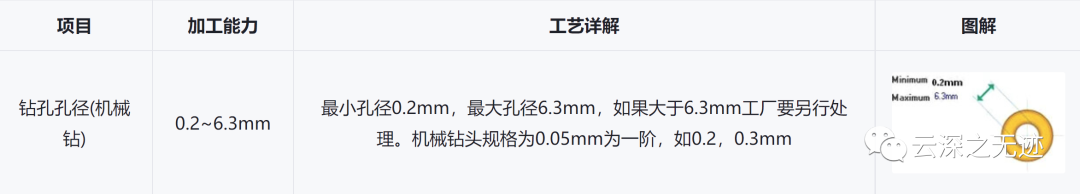

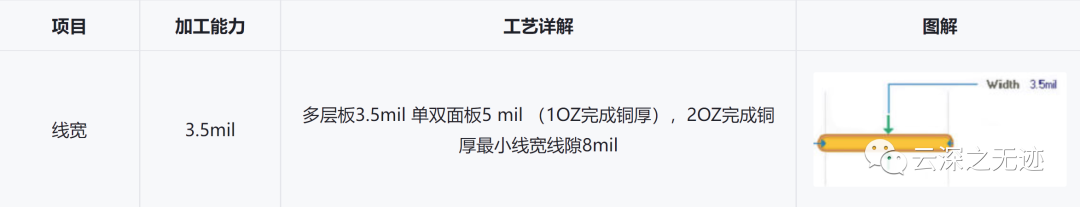

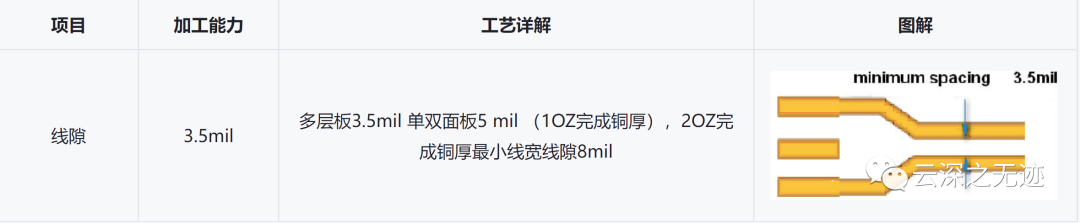

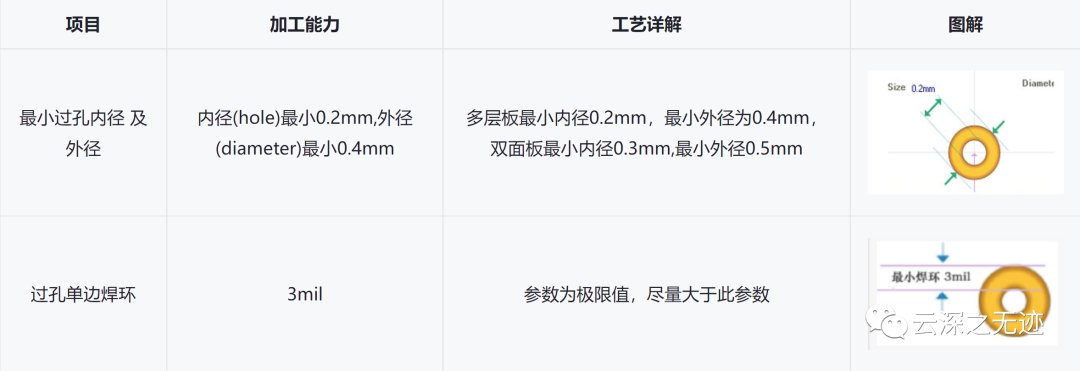

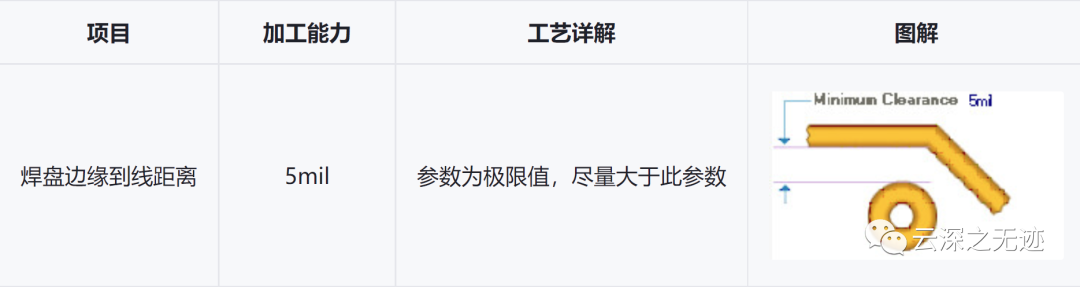

上面是jlc的一些工艺的极限,注意设置

通常,PCB上的引线被油覆盖,以防止短路和损坏设备。所谓的窗口是去除导线上的涂料层,以便导线可以暴露于锡中。

在走线的时候关掉一些无关紧要的东西

在顶层绘制导线的同时,使用切换至底层的快捷键 “B”,可自动添加设置的过孔,走线并自动切换至底层继续布线。在底层则使用快捷键 “T” 切换至顶层继续布线。当你在一个层无法顺利布线连接的时候,需要考虑调整器件布局,添加过孔换层绘制。

可以看到就是从下面走了

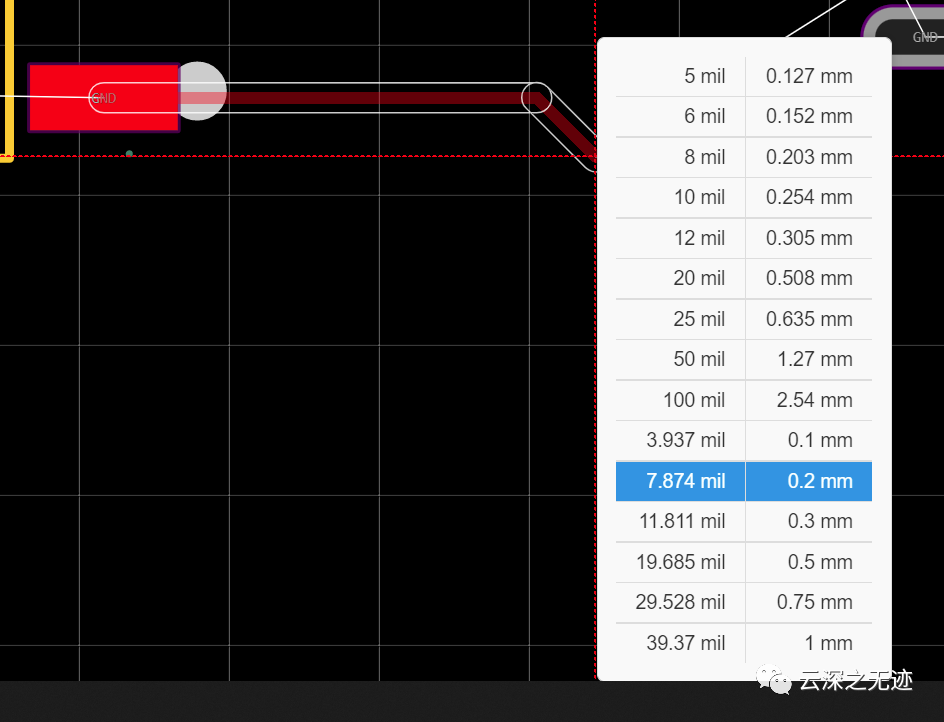

布线时,如果你想布一段线段后,下一段线增大线宽,可以按 “SHIFT+W” 快速切换导线宽度。

调整线

单个线材的旋转

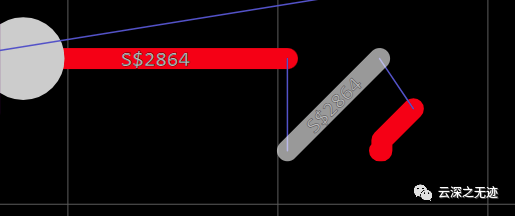

我忘了这个截图是啥了

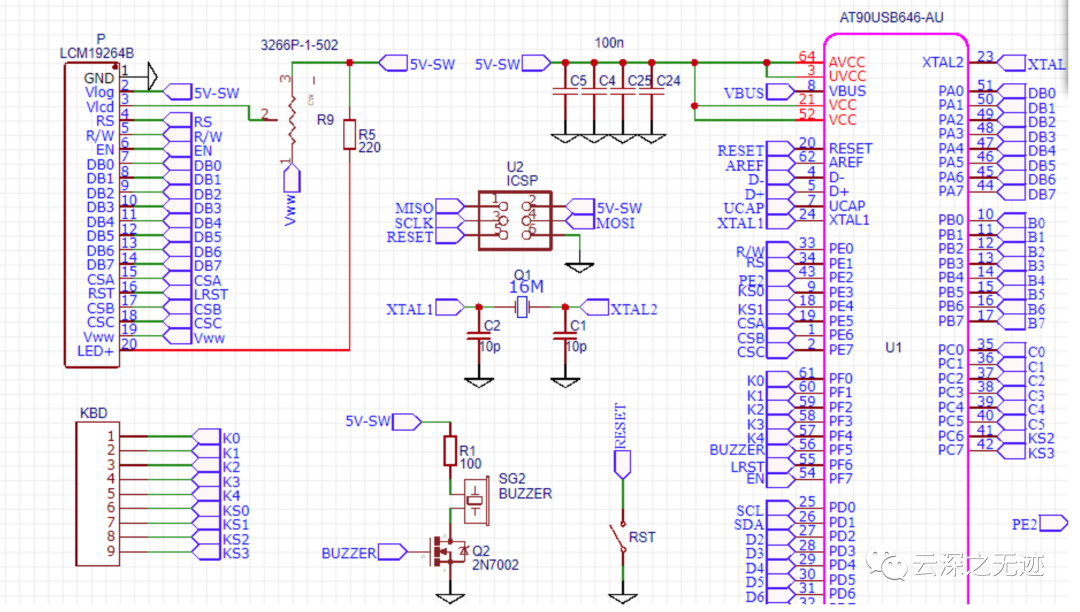

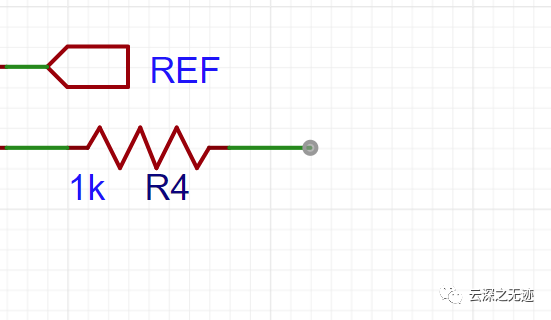

使用网络端口可以使原理图变得清晰简洁,没有过多的导线,只需给每个端口设置一个网络名称。

对,这个功能好,但是专业版的会长一些,不可以混用

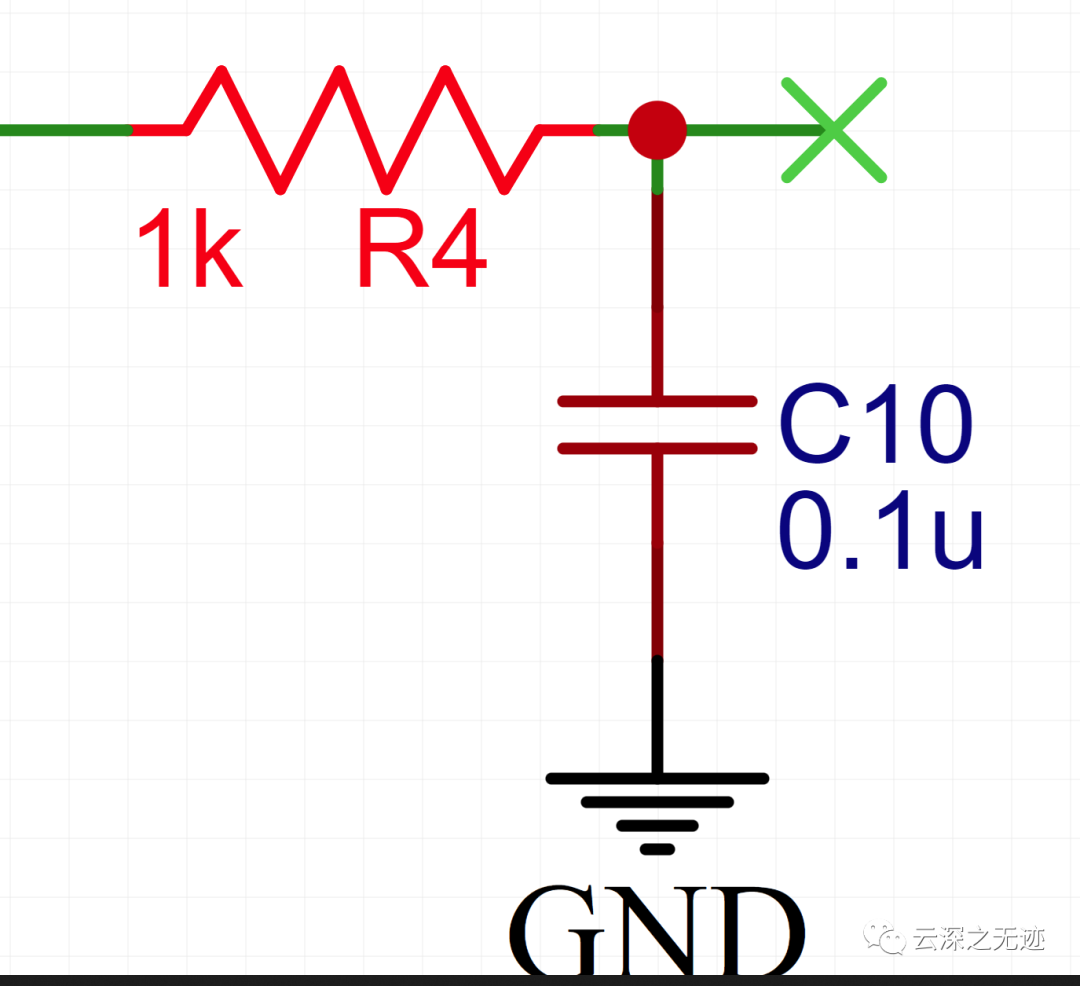

不连接和悬空的时候需要放置这个

提示感叹号图标。这种一般出现在:

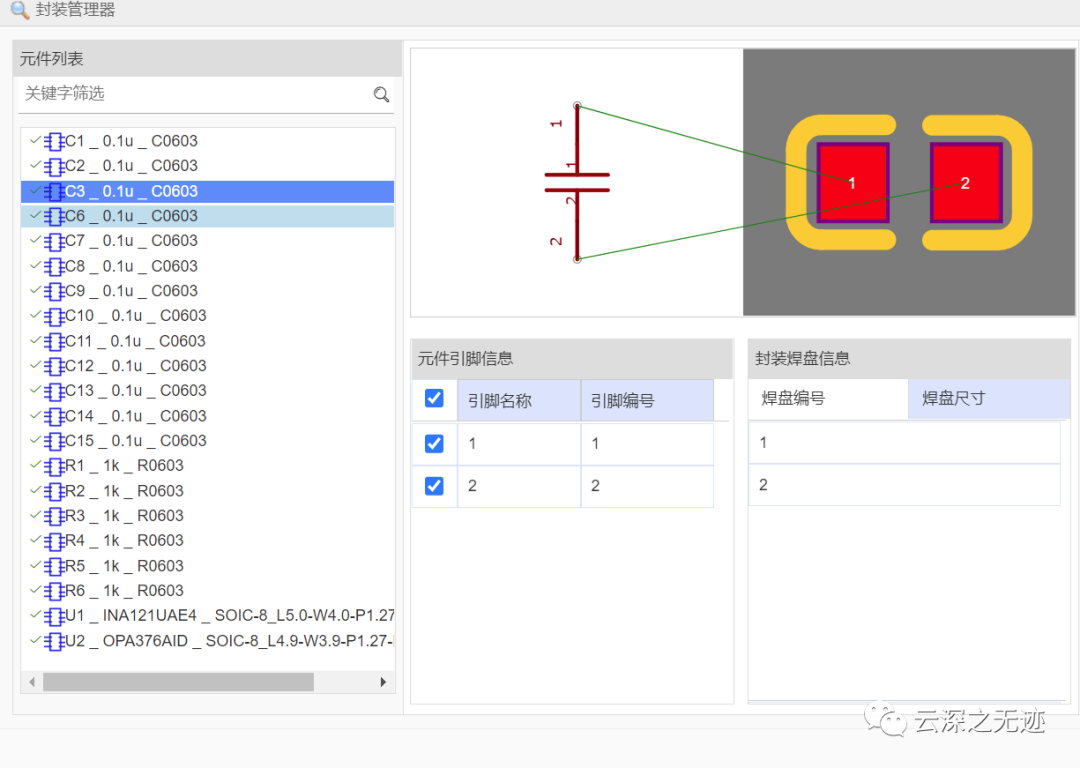

封装管理器,可以一次性看所有的封装

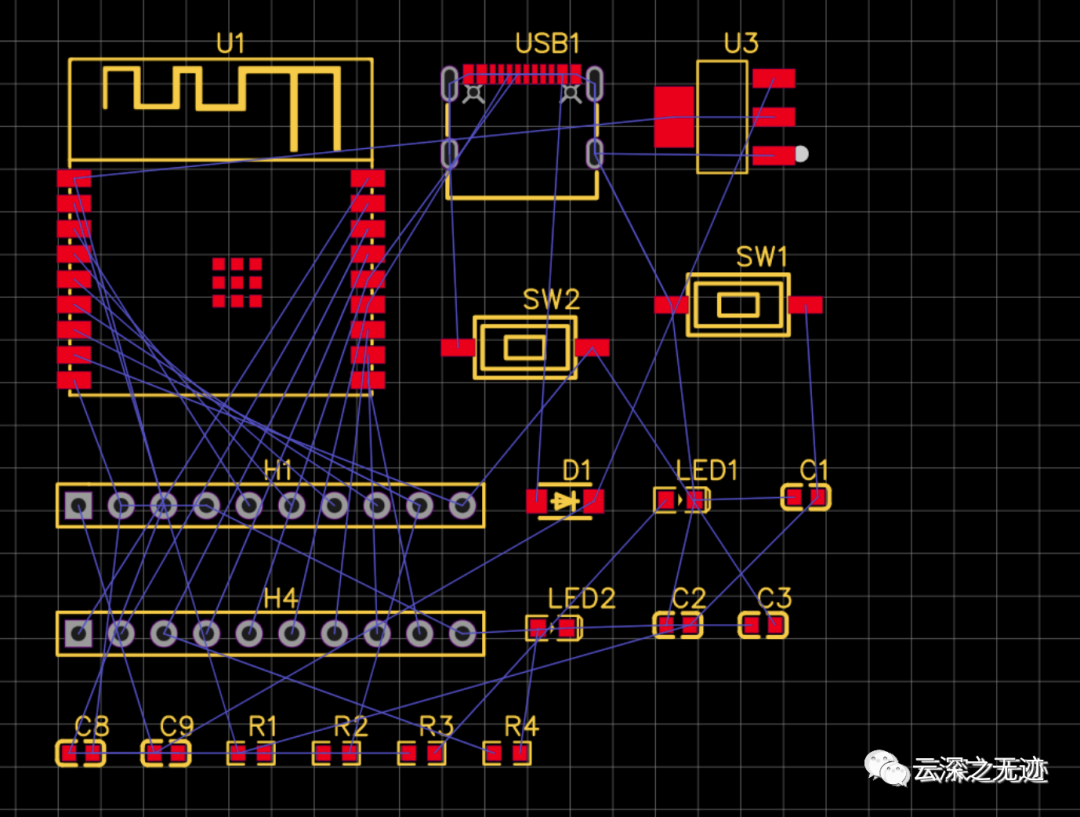

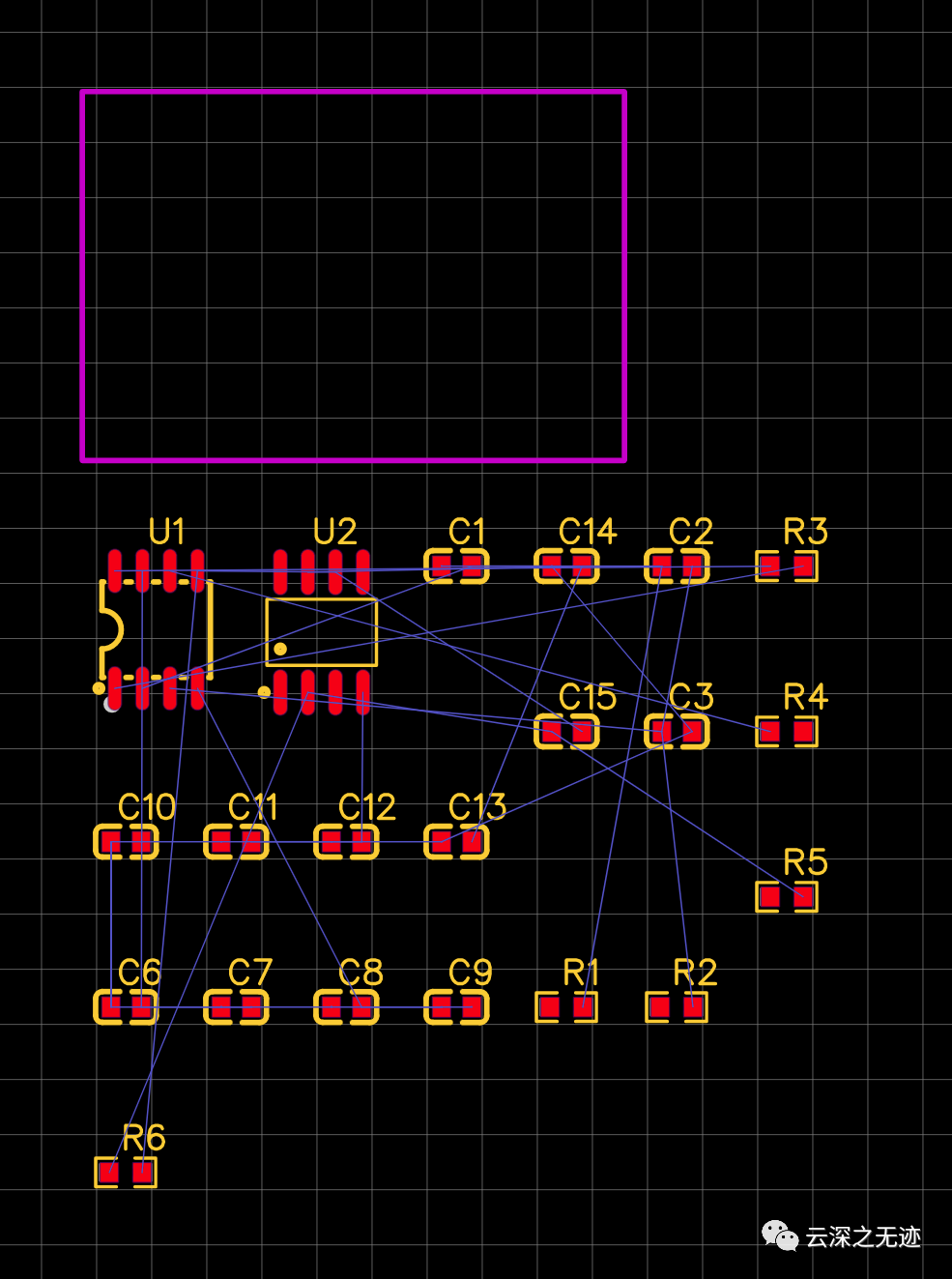

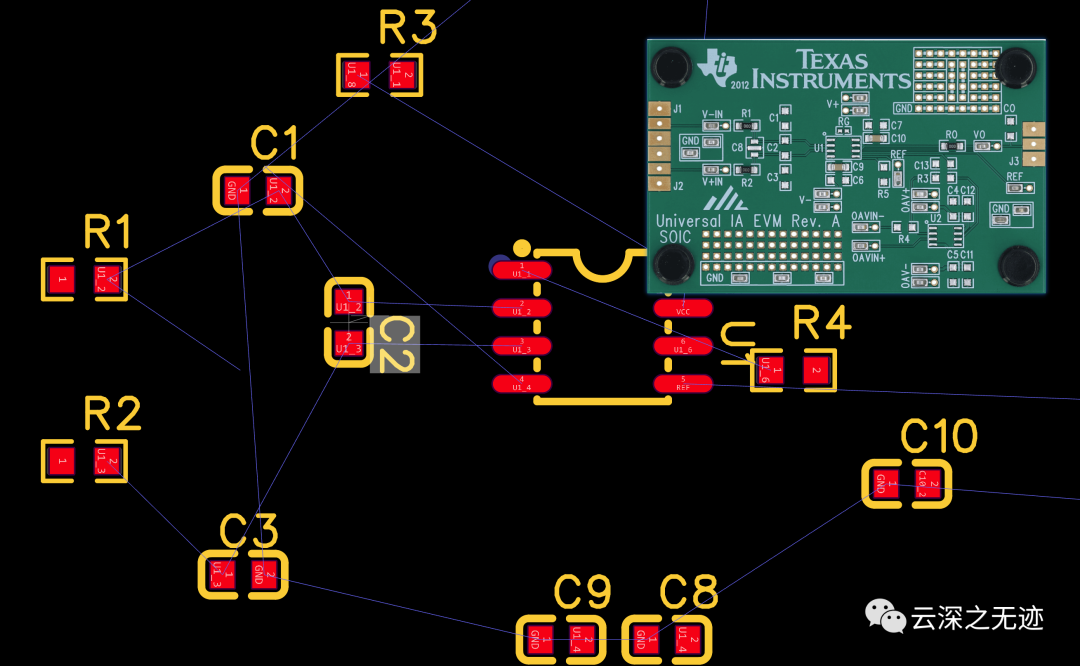

这个也是走线前的一堆

Ctrl+Shift+X

普通和专业的之间是需要在这里导入的

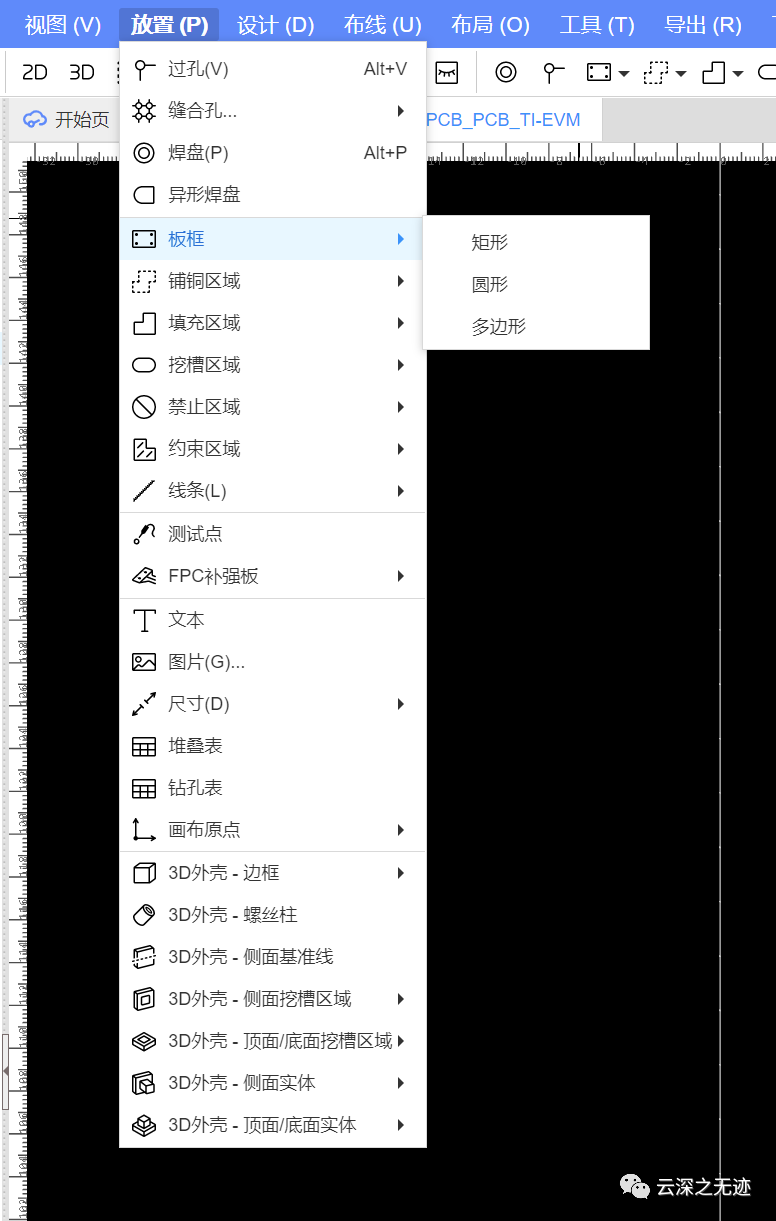

专业版的我找到了板框,但是普通的没有,默认的板块是原件面积的1.5倍

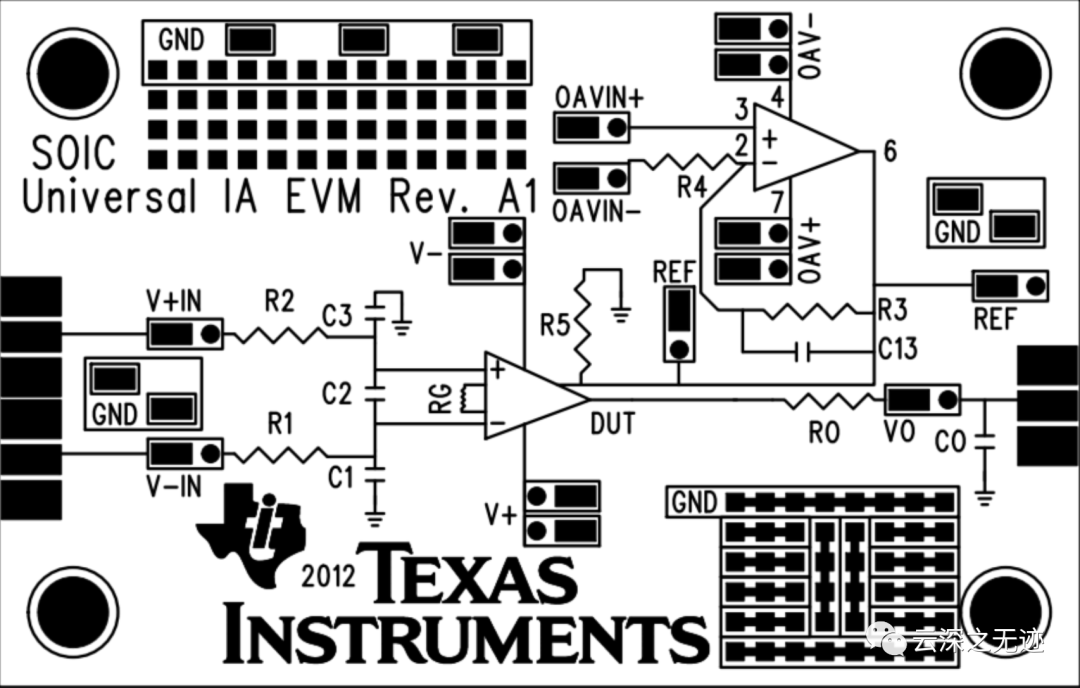

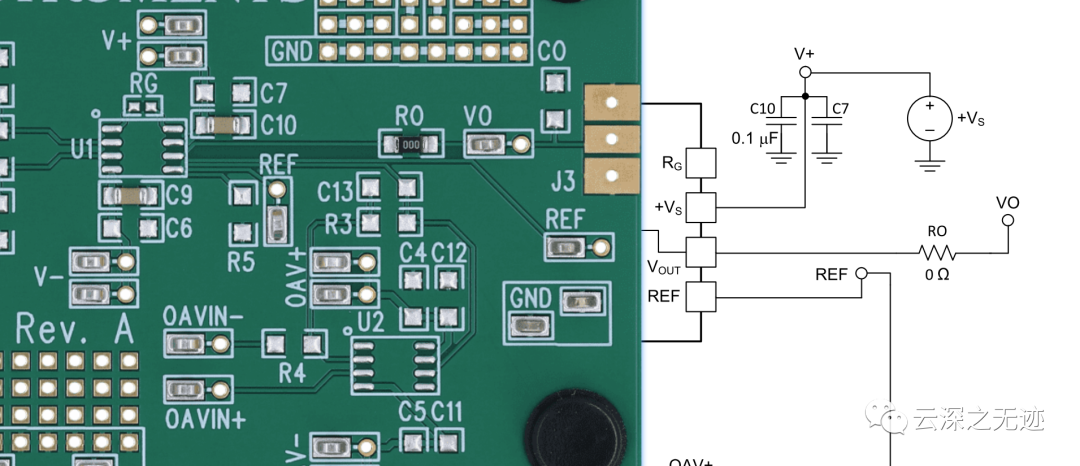

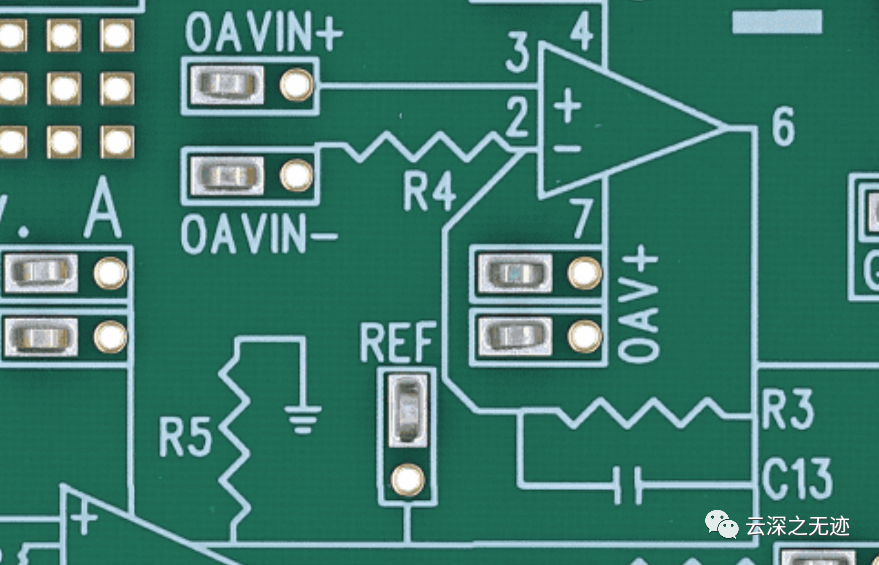

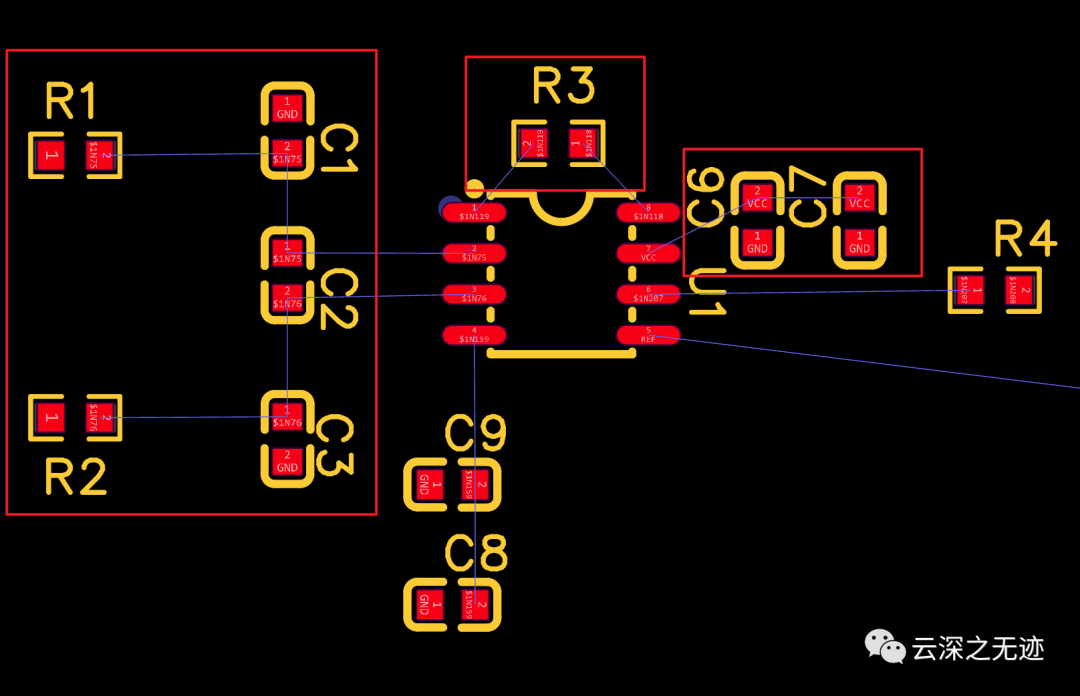

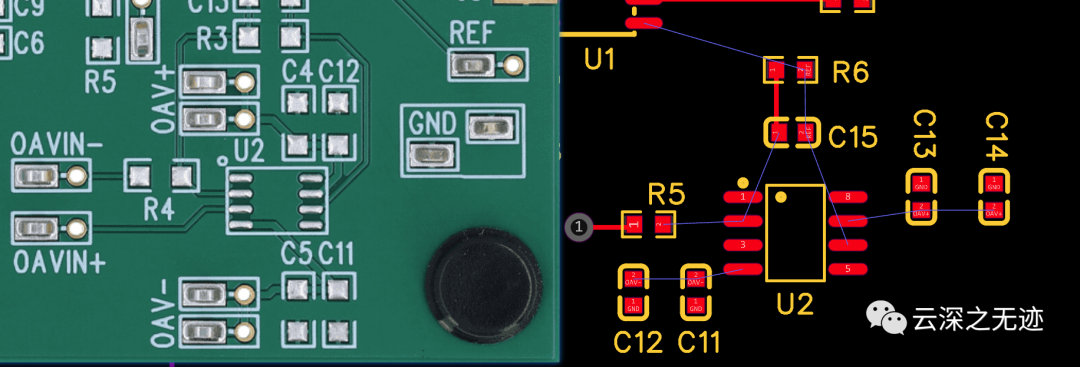

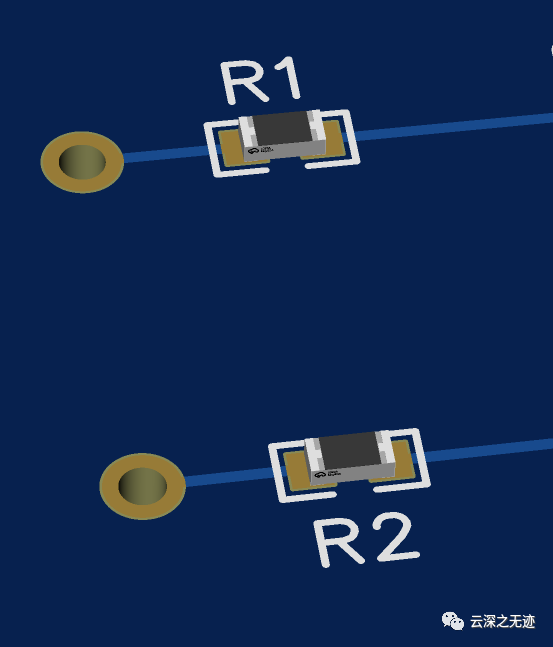

跟着这个板子来走线,这个是表面的丝印

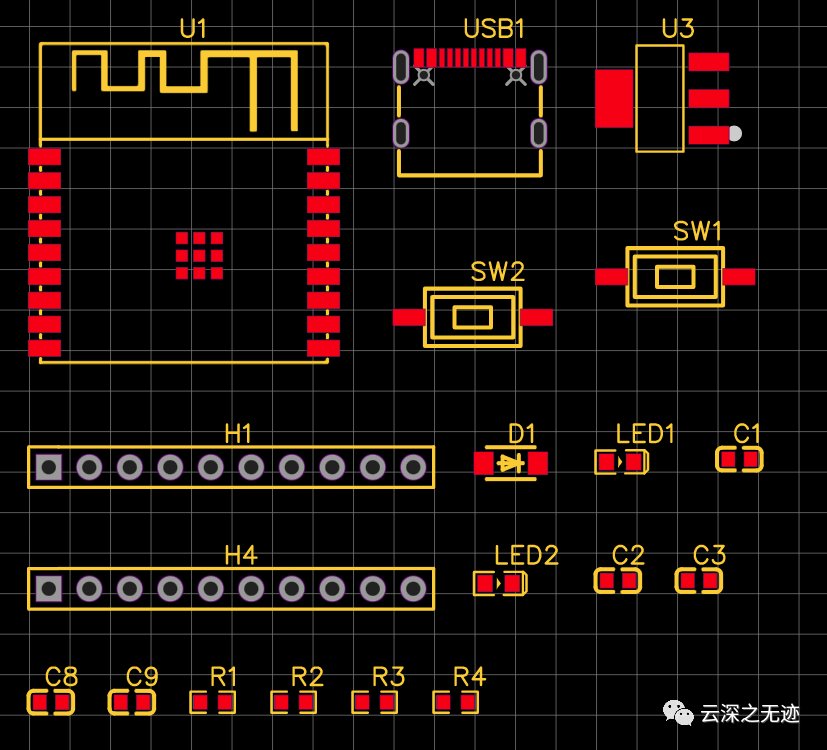

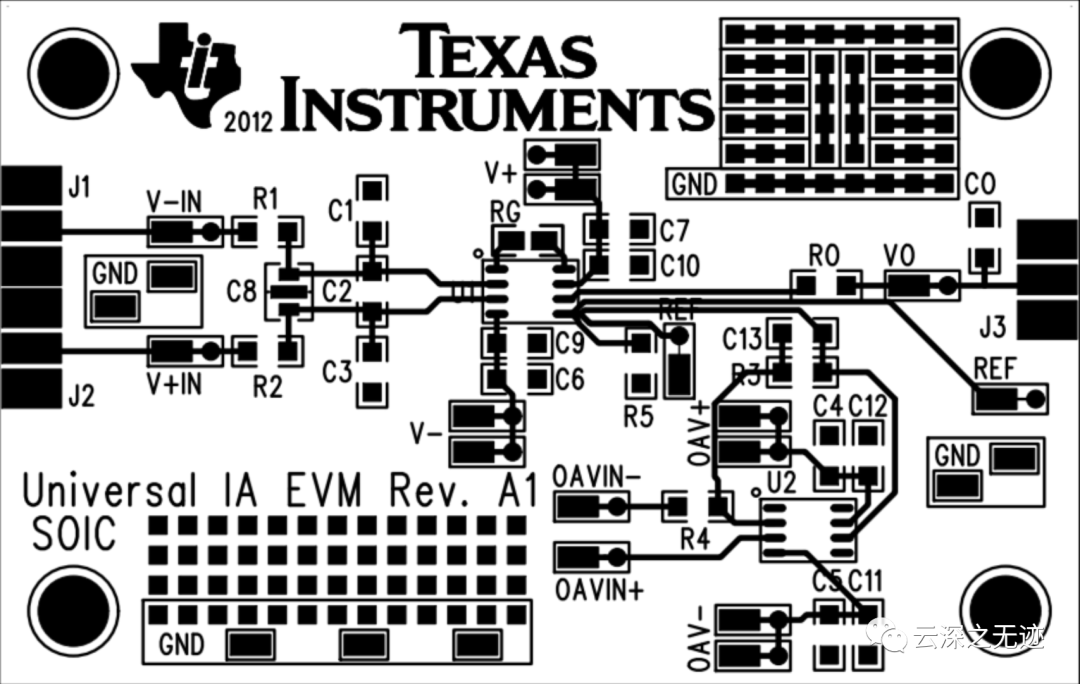

这个是真实的走线

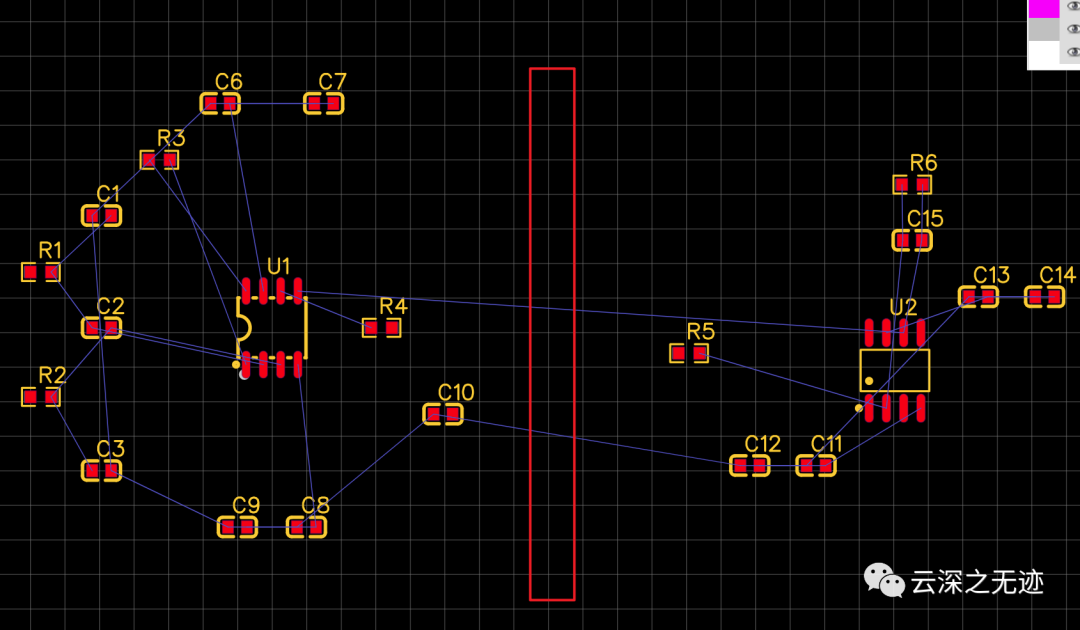

截图以后这样对着走

先把地关掉

对照走线

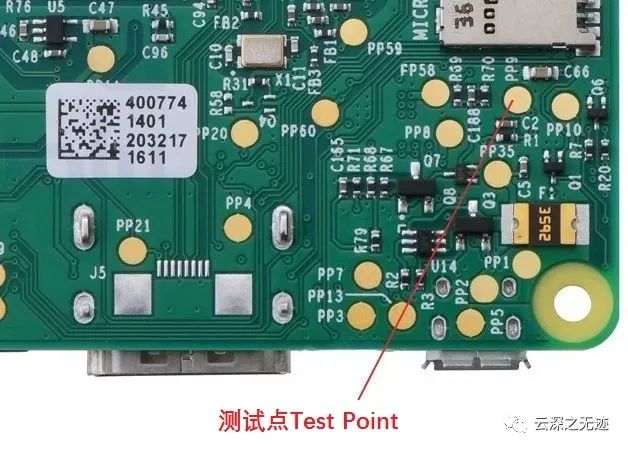

如果有一些这样的裸口,我的建议是打×,PCB的时候放焊盘或者孔

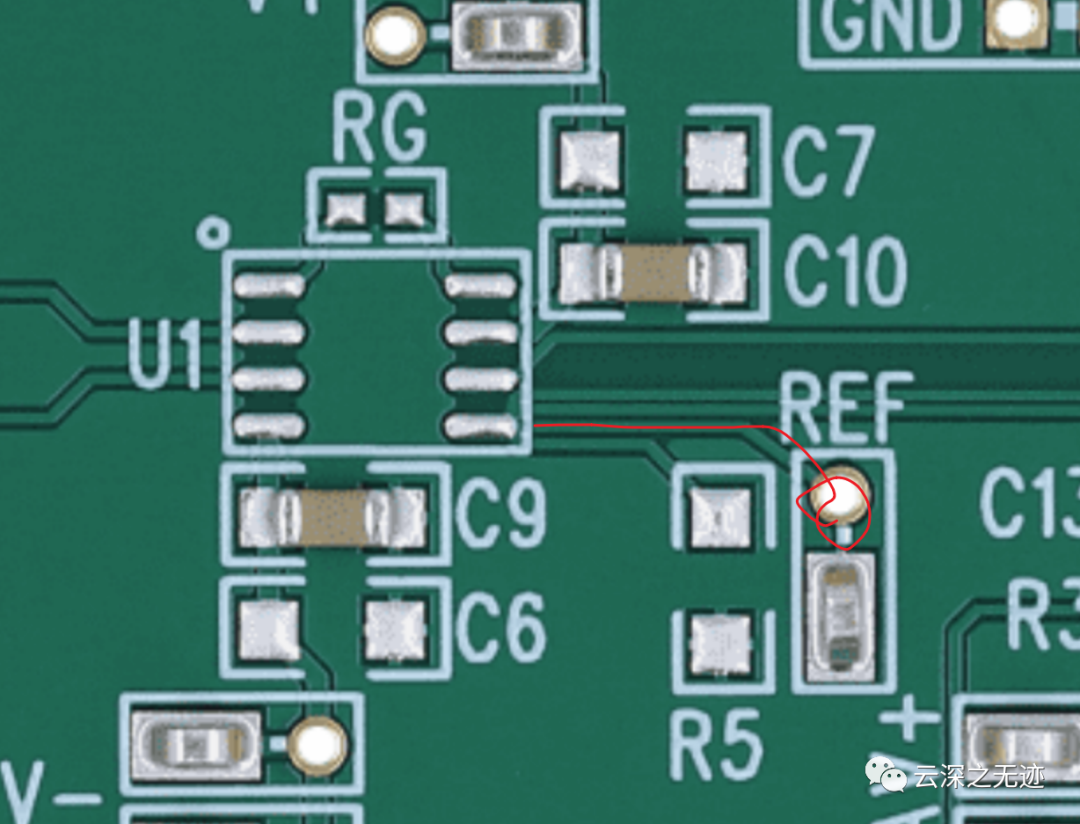

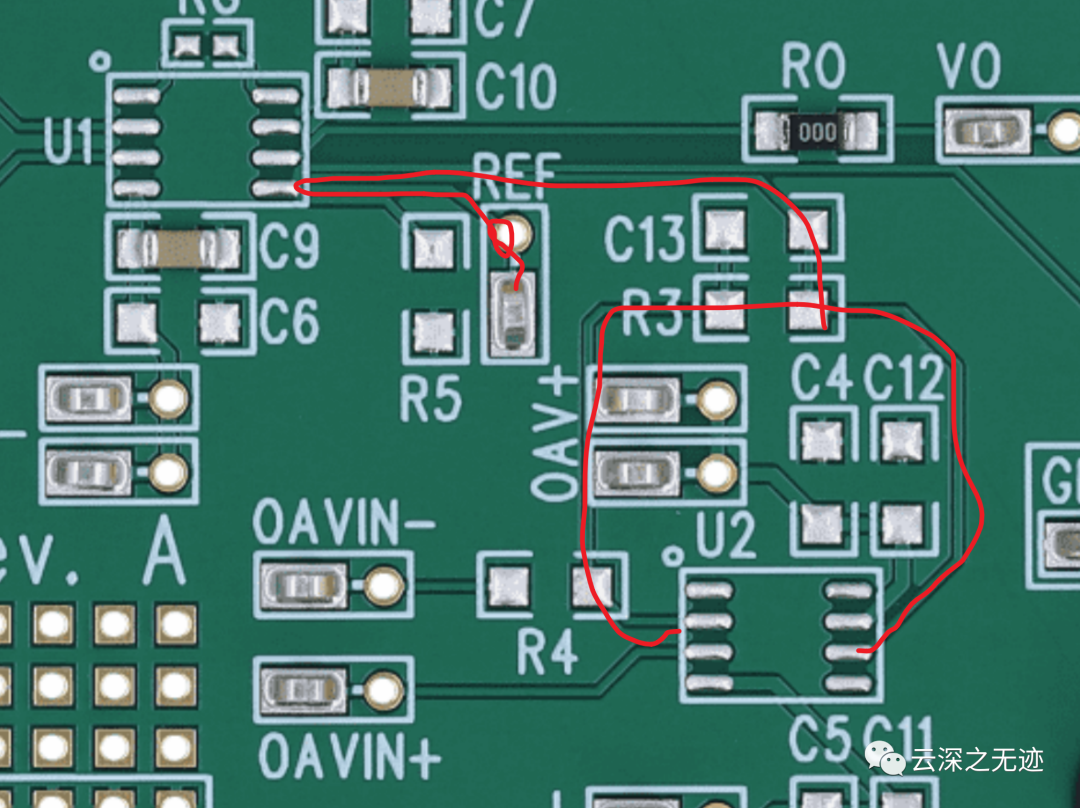

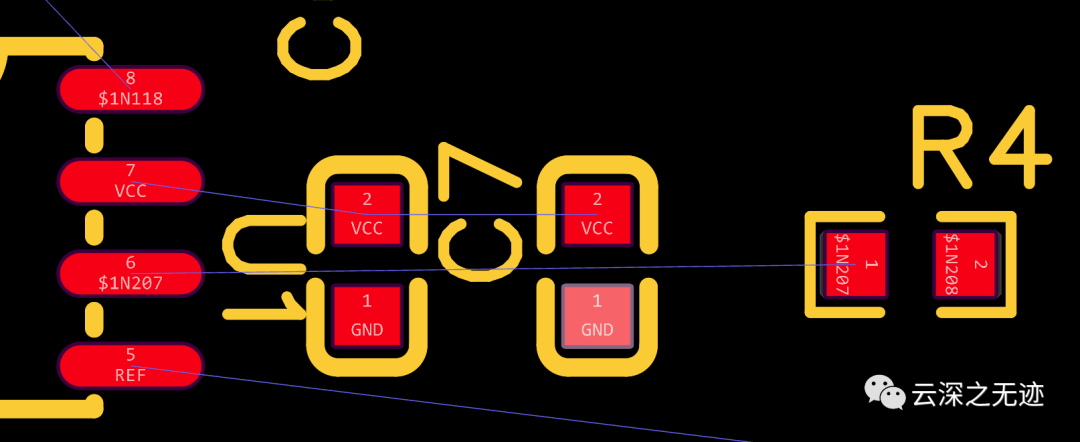

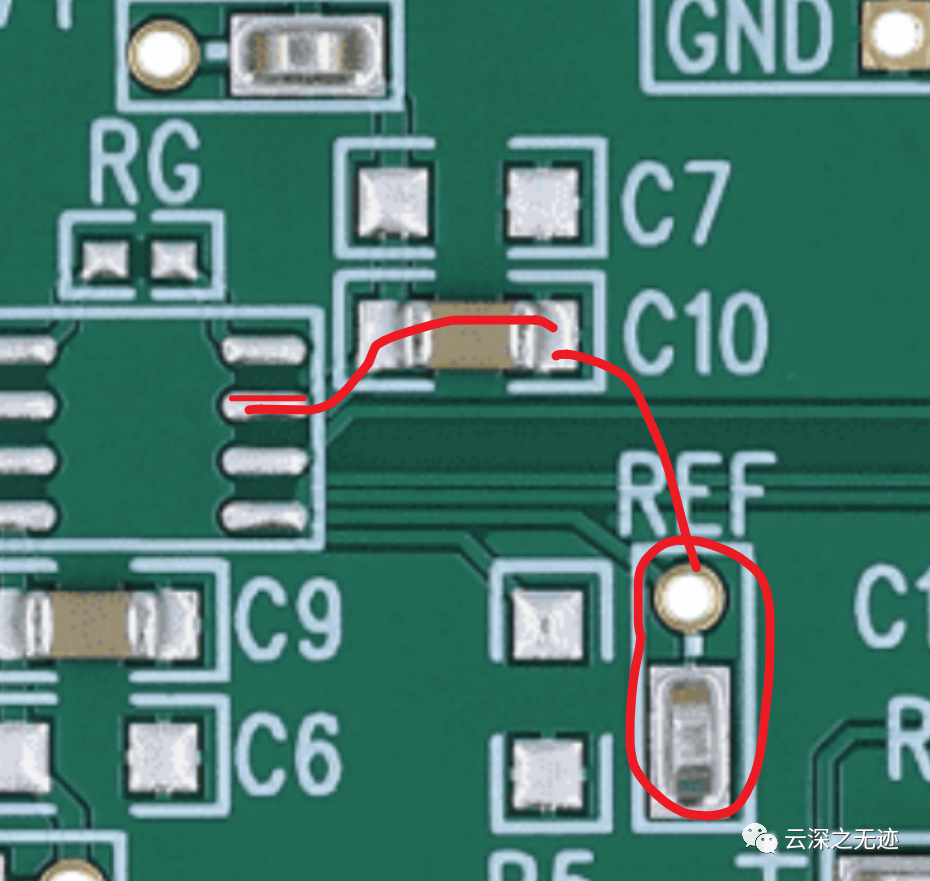

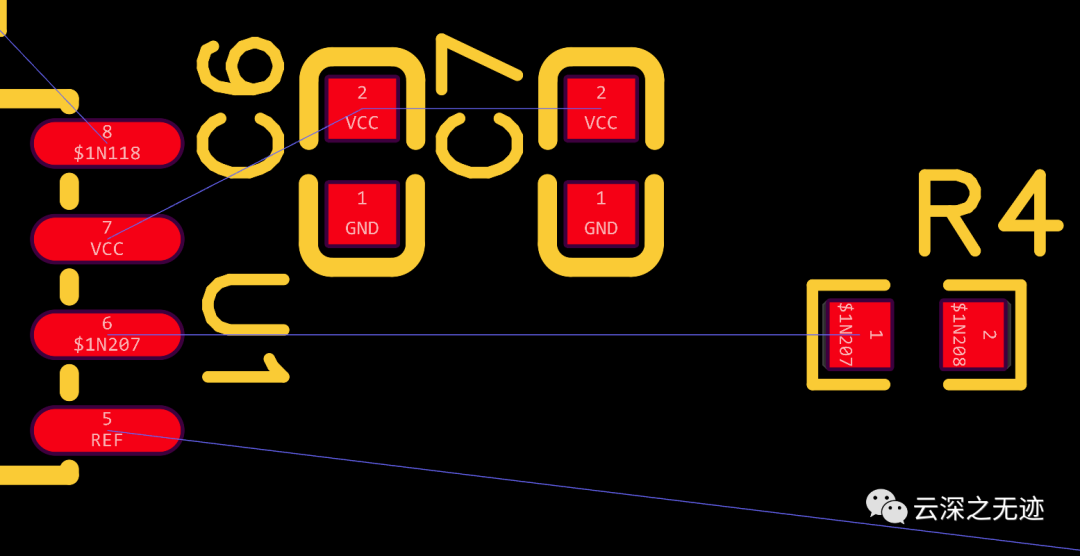

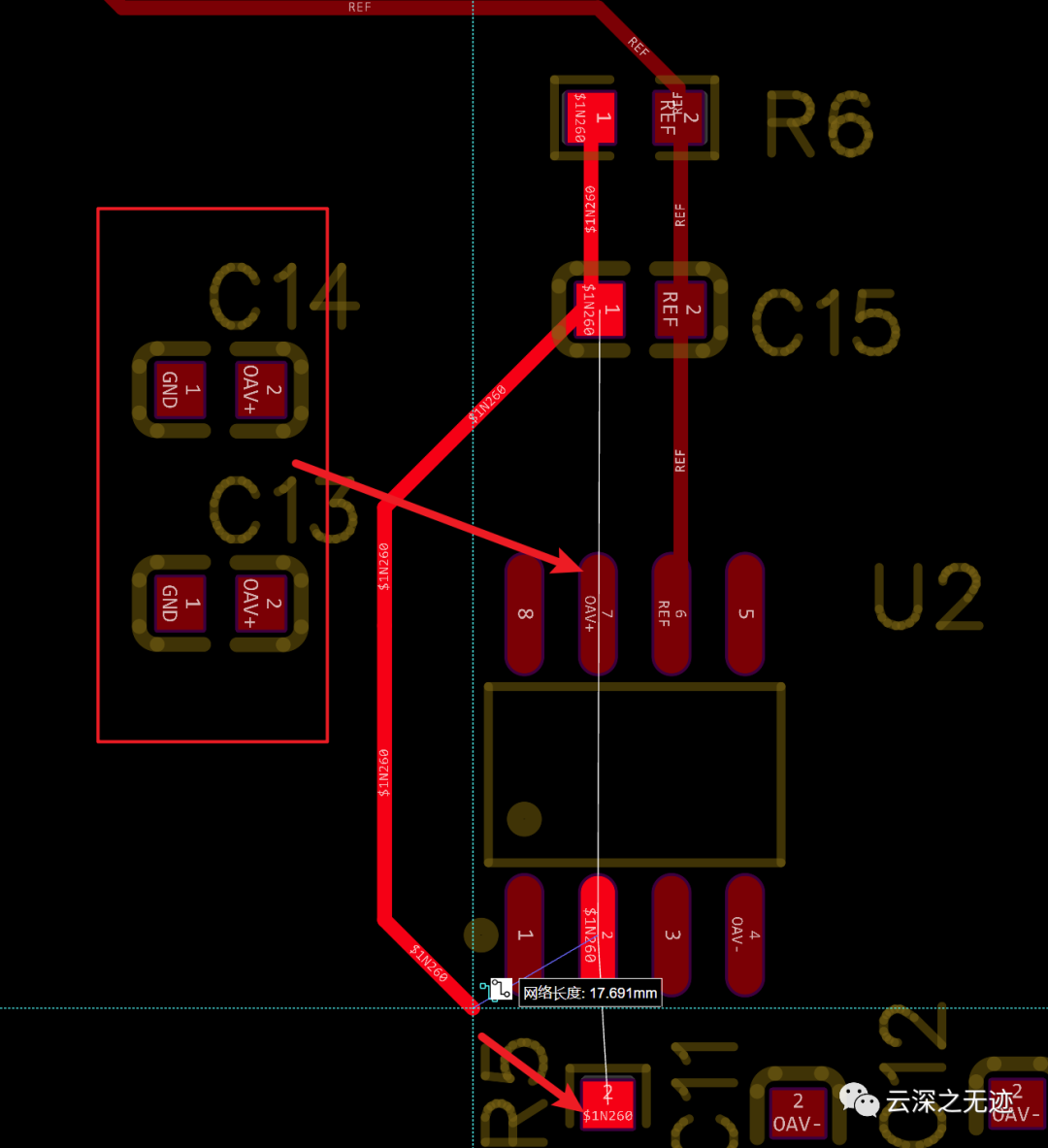

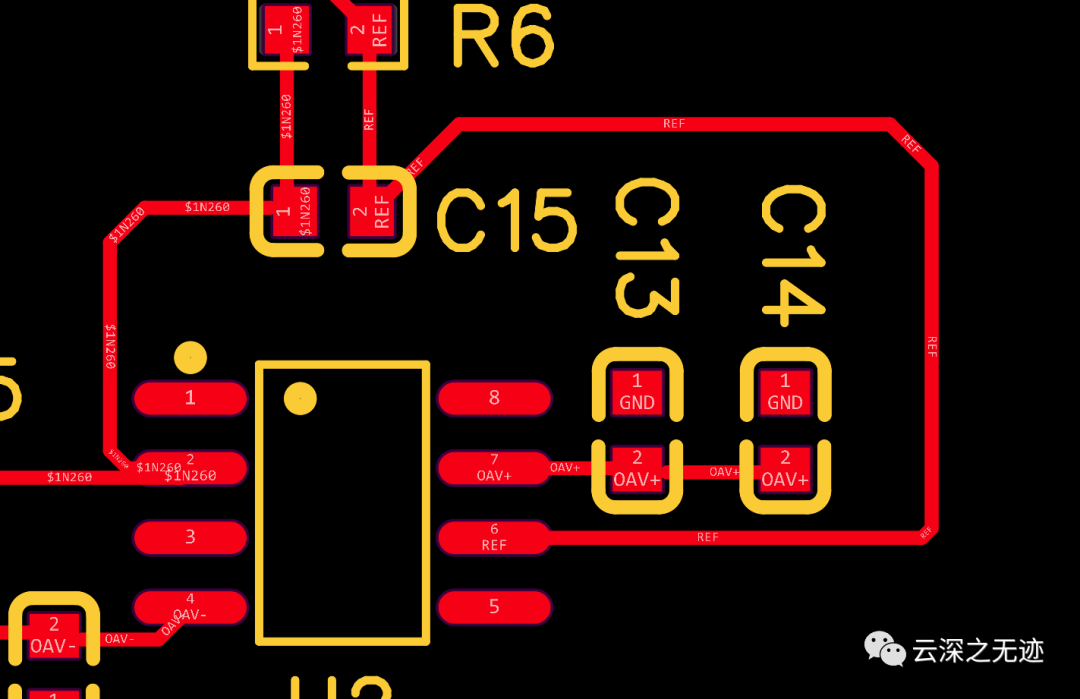

可以看到REF的引脚这里是一次走了三个线出来的

应该是这样走的

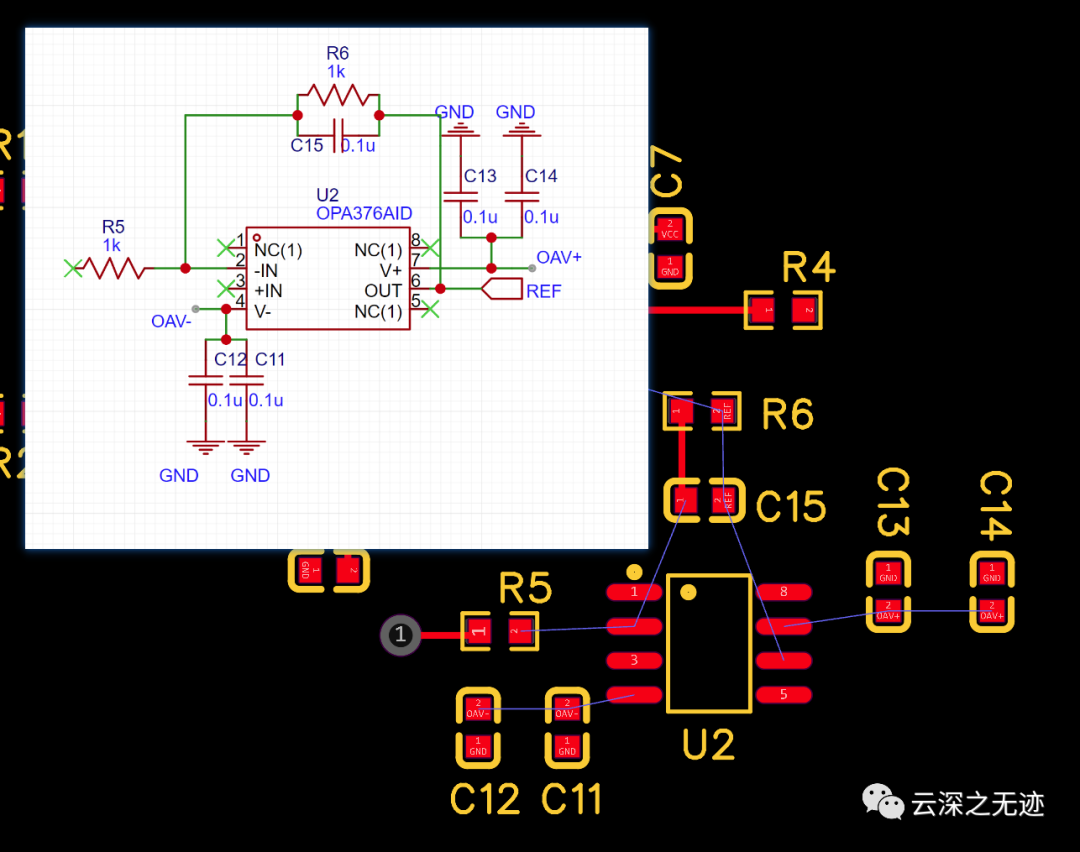

反面是这样,既可以直接接地,也可以是接缓冲器,同时也接了一个调试的接口。

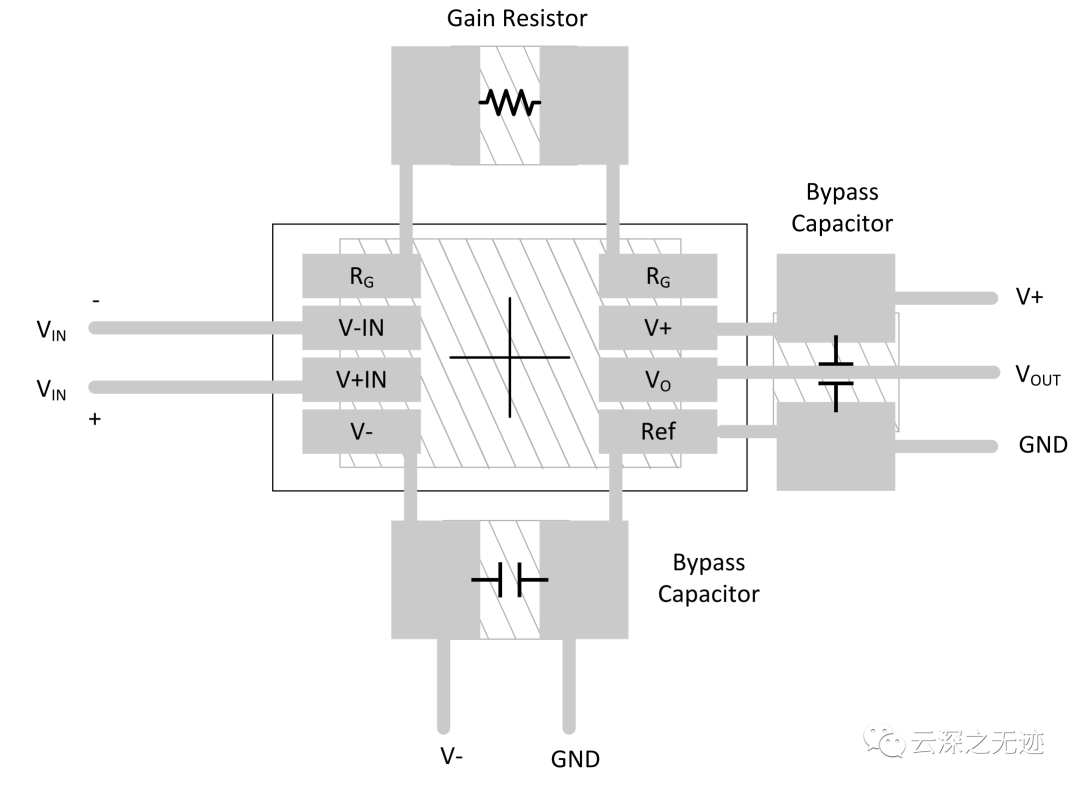

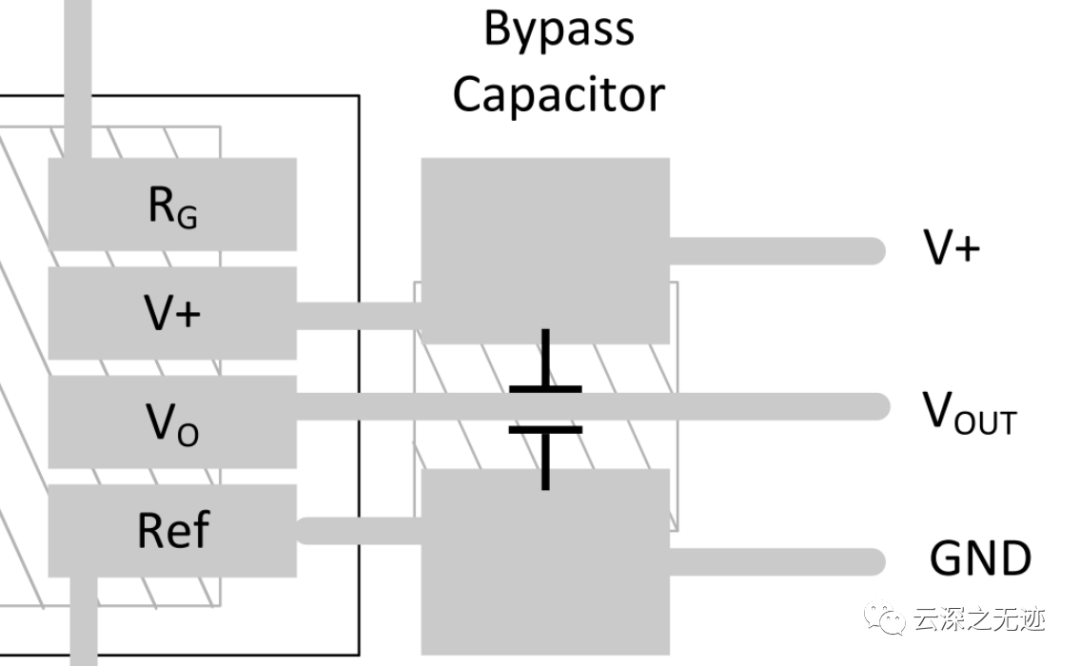

电容的位置都是旁路电容

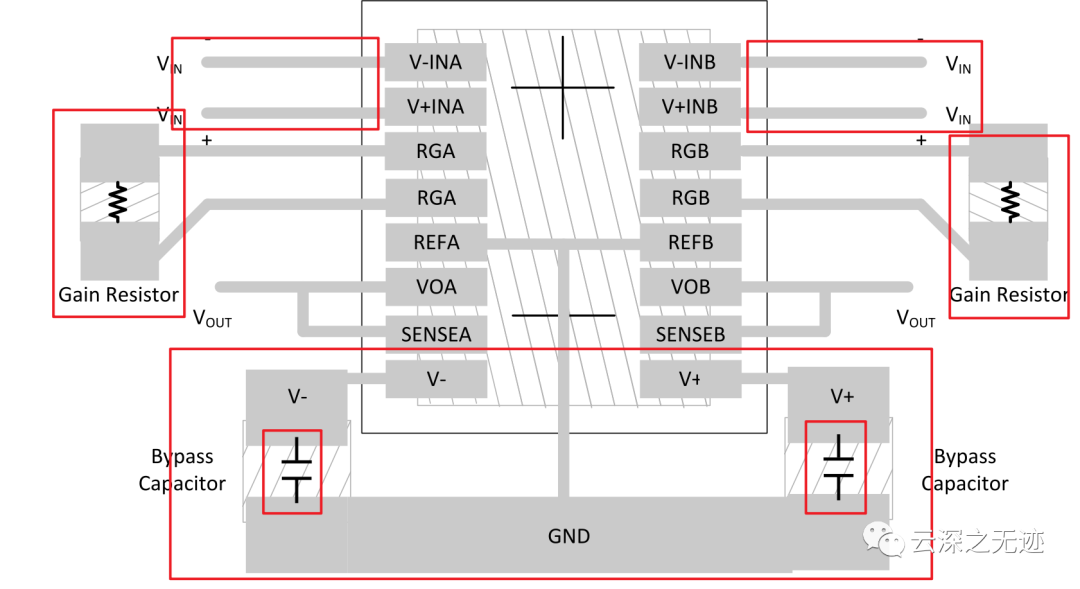

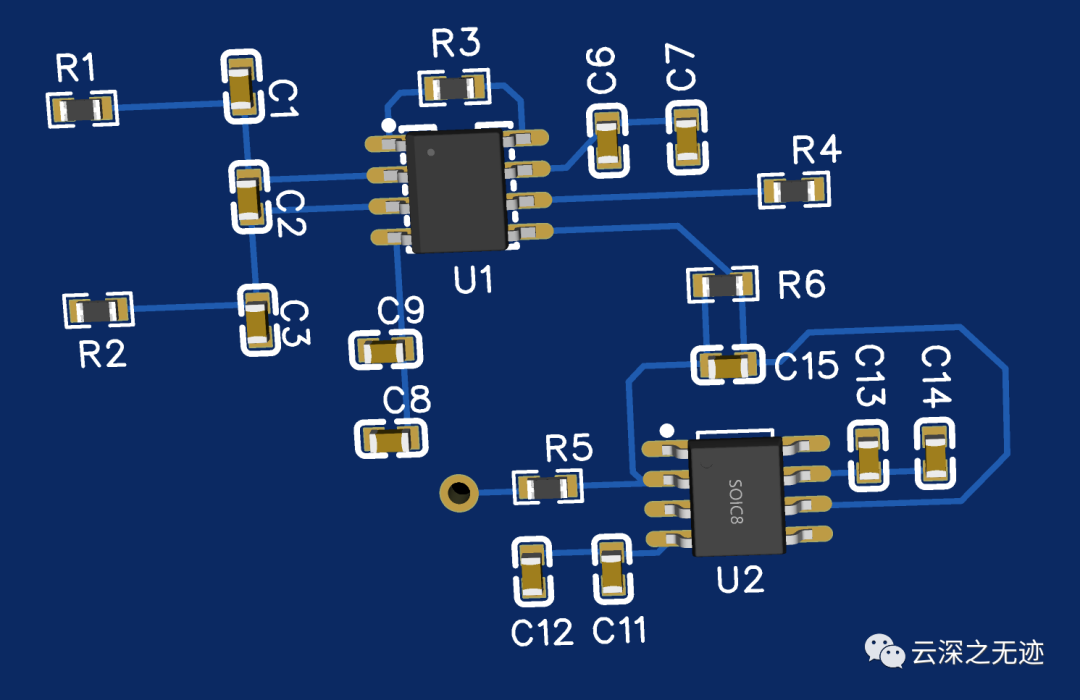

这个是大的封装,里面有两个2个运放单元的

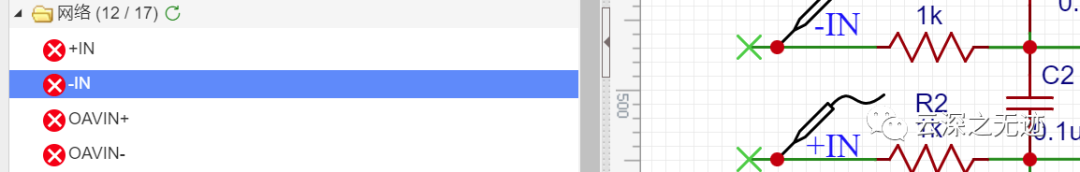

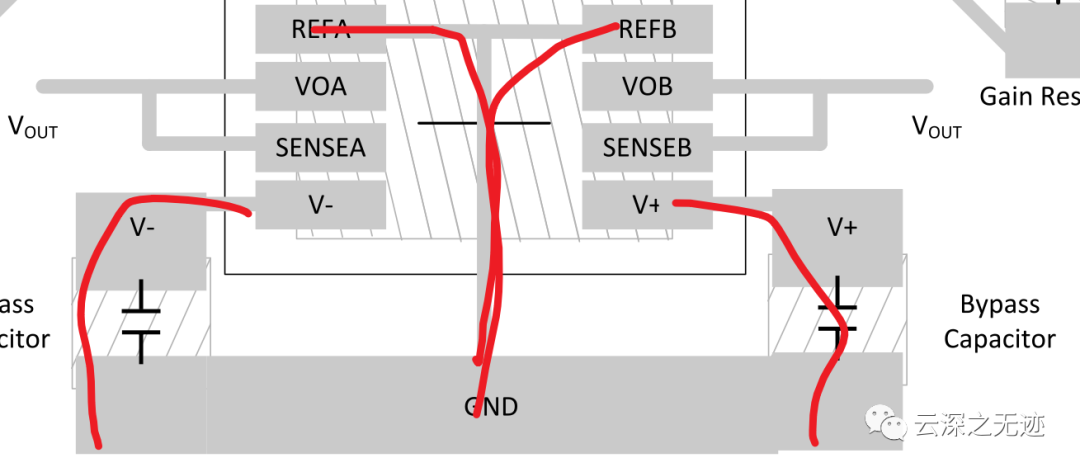

在文档里面说到这里两个输入的地方是需要远离的

但是看这里,V+与参考之间还是有一个电容的,然后是地和参考在一起

这样吗?

看这个不是,应该是铺铜互联的

那就是这样对,不过要是参考接地也可以压住这个输出

其实都互联,不过是越短入地越好

布局原则始终建议注意良好的布局实践。为了使设备具有最佳的操作性能,请使用良好的印刷电路板(PCB)布局实践,包括:确保两个输入路径的源阻抗和电容匹配良好,以避免共模信号转换为差分信号。此外,增益设置管脚的寄生电容也会影响CMRR。

例如,改变RG值的应用中,选择使开关电容尽可能小的组件。

在每个电源引脚和地之间连接低esr, 0.1 uf陶瓷旁路电容器,放置在尽可能靠近器件的地方。

从V+到地的单旁路电容器适用于单电源应用。电路的模拟部分和数字部分分开接地是抑制噪声的最简单和最有效的方法之一。多层pcb上的一个或多个层通常用于接地面。地平面有助于散发热量并减少EMI噪声。

确保物理上分开数字地和模拟地,注意地电流的流动。

为了减少寄生耦合,输入走线应尽可能远离电源或输出走线。

如果这些走线不能保持分离,垂直穿过敏感走线比平行穿过噪声走线要好得多。将外部组件尽可能靠近设备放置。

这个是源文档的说法

保持Ro靠近引脚,以减小寄生电容。留下尽可能短的走线

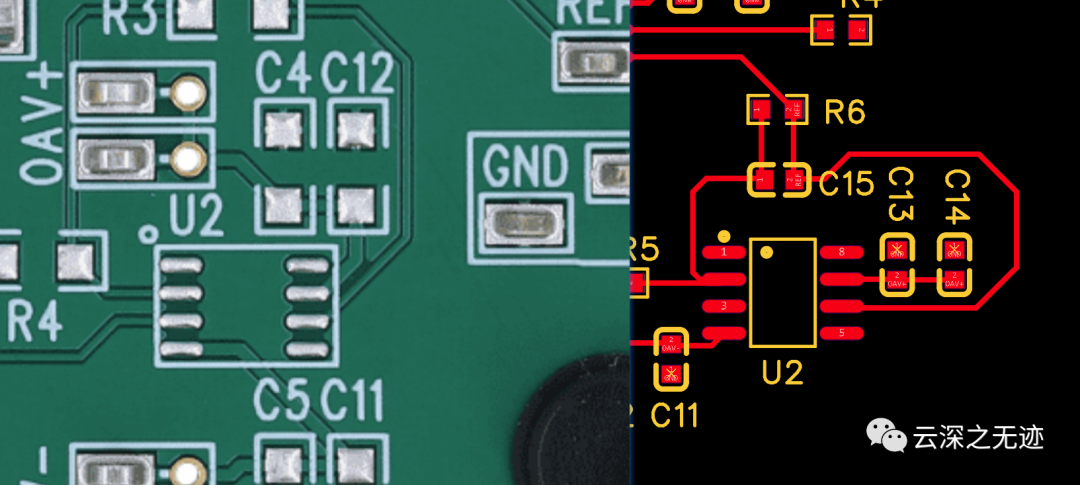

布局大概就是这样

有一种写错了丝印的感觉

看着不对,旋转了

打结了

这次就顺利了

一样

但是这里变成了死区

但是看着原来的布线也一样啊

DRC都是地线

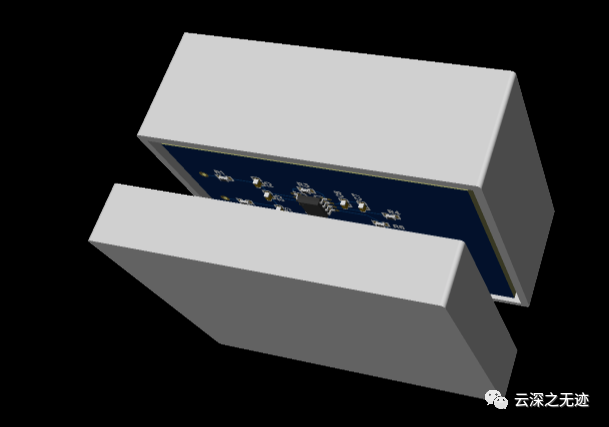

预览一下

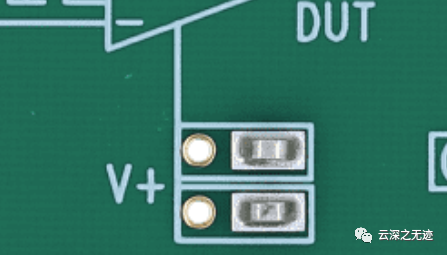

前面的引脚放了孔,可以焊东西

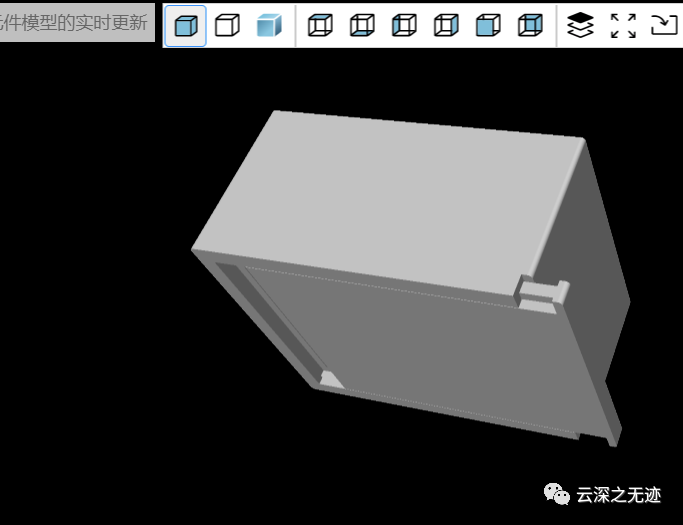

外壳,推拉的

盖板的,我也没有研究

还有就是一个加强的

还有好多知识啊,我不行了。

可爱猫猫

https://www.cnblogs.com/guohaomeng/p/16164618.html