每当用手机流媒体播放4K电影或玩在线视频游戏时,我们都需要高速率的数据传输,使我们的连接设备能够提供引人入胜、互动、身临其境的体验。我们的数字世界,随着智能水平的提高,对底层技术的要求越来越高,这些技术使所有这些活动成为可能,但同时也存在阻碍实时响应的瓶颈。

工程上的聪明才智一直是推动创新的一种方式,而半导体行业无疑处于前沿。随着设计人员将数十亿个晶体管集成到单个芯片上,以满足AI、高性能计算和网络等计算密集型应用的需求,我们已经看到摩尔定律被扩展到一位数纳米。随着规模和系统复杂性的增长,纳米级的物理芯片特征可能不再满足,为埃级的缩放铺平了道路。

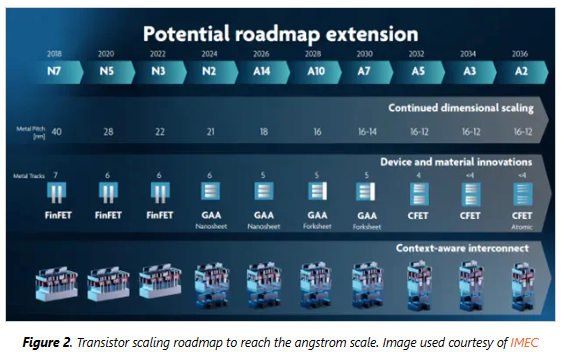

埃是1米的100亿分之一,是一个测量单位,通常用于表示原子和分子的大小,在半导体工业中,还用于表示集成电路部件的尺寸。2021年,英特尔率先制定了引入埃时代的工艺路线图,预计将于2024年投入生产。与此同时,IMEC,纳米和数字技术的独立研究中心,已经概述了晶体管缩放路线图,到2036年将使该行业达到2埃(如下图所示)。

实现埃级设计需要整个半导体生态系统的协作和创造。新的技术和已有技术(从光刻技术的创新到新的晶体管结构,如栅极全能(GAA)和互补场效应晶体管(CFET)以及多晶片系统)引领了芯片设计的下一个时代。

摩尔定律的放缓推动了新的创新

根据摩尔定律,芯片设计师们期望可以大约每两年将芯片的密度提高一倍。通过实现更小的工艺节点,设计团队仍然可以实现功率、性能和面积(PPA)优势,以满足我们更智能、更互联的需求。然而,根据摩尔定律制造连续更小的特征能力(称为特征缩放)正在放缓。

埃级缩放代表了一组新技术,以补偿特征缩放的放缓,同时保持摩尔定律的目标,例如晶体管密度随着每一个连续的工艺生成而增加一倍。通过埃级缩放,设计工程师可以在芯片上安装更多的晶体管,以更低的功耗提供更高的性能。

考虑到埃级芯片将支持的晶体管数量,未来可能带来:

拥有更紧凑的机器人设备的生产线,经过训练可以比今天的工厂自动化设备以更快的速度和更高的精度完成任务;

更快和更准确的建模,以预测气候变化的影响,加快新疫苗的发现,并提供金融投资组合和风险管理见解;

为汽车等行业提供更高效的研发和产品设计流程。

克服制约SoC性能的瓶颈

不用说,性能上的任何滞后都可能导致各种应用程序的结果低于标准。然而,瓶颈确实发生在各个层面。

神经网络用于深度学习算法,可以识别原始数据中的模式和相关性、聚类、分类,并从中学习以持续改进。这些算法得益于大量并行处理器的实现。一块硅片上可以放置的处理器越多,芯片就能更快地运行这些庞大的工作负载。

但是芯片设计人员必须解决多个瓶颈,以实现支持这些类型应用的SoC所需的PPA:

在晶体管层面,将晶体管连接在一起的互连存在瓶颈。

在处理器级别,需要权衡处理器的复杂性和数量,以及连接它们所需的互连量,及在处理元素和系统内存之间快速移动数据的需求。

在内存层面,存在一个差距,因为片上内存的扩展速度不如标准单元和逻辑库。因此,如果内存footprint不能随之缩小,就只能从越来越小的逻辑中提取大量内容。

在某种程度上,拥有更大的处理器似乎更容易编程,也可以做更多的事情。然而,这带来了高效设计和制造这些大型设备的复杂性,同时减少了并行度,并增加了简单任务的功耗。

从核心工艺定义到芯片设计构建模块,再到实现芯片设计的一套自动化工具和流程,埃级工艺的设计通过大规模的研究和开发活动,涵盖了整个设计链上的大量技术。这些是通过以下方式实现的:

用新的晶体管结构增强传统光刻技术的尺寸缩放;

构建候选晶体管结构的数字孪生的技术,以及评估和选择最有前途的工艺定义;

新的逻辑库和内存架构是芯片设计的构建模块;

EDA工具中的新算法使设计人员能够实现和验证使用这些构建块设计的晶体管数量呈指数级增长的芯片。

先进光刻

先进的光刻工具,如High-NA(高数值孔径)EUV(极紫外)光刻技术,目前正在开发中,预计将于2025年交付给晶圆厂,这种光刻技术能够打印更小的结构。

背面电源分配

在埃级结构中,将配电从晶体管上移动到晶体管下称为背面电源分配。背面电源分配将使GAA结构实现其全部密度潜力,使设计人员能够缩小逻辑单元的高度,因为单元不再需要顶部和底部的电源轨道来承载功率。它还在单元上方的布线层上释放了大量的布线资源,防止互连成为瓶颈。

GAA和CFET

同时,GAA晶体管结构允许多个通道相互叠加以增加芯片密度。GAA还可以实现FinFET结构无法实现的内存缩放,同时减少泄漏电流并增加驱动电流,以获得更好的整体芯片性能。

CFET是GAA的一个更复杂的版本,由垂直堆叠的晶体管组成,具有显著的面积和性能优势,特别是对于存储器。由于CFET的设计目标是在2.5nm及以上,因此预计CFET将在埃时代发挥不可或缺的作用。

Chiplets

另一个可以与埃级芯片齐头并进的创新是多die系统,通常被称为chiplet,chiplet之间通过堆叠或与中间层连接,集成在一个封装中。这种相互依赖的架构可以通过分解来创建,将一个大的die划分成更小的die,以获得更好的系统成品率和成本,或者通过组装来自不同工艺节点的die来获得最佳的系统功能和性能。

与大型单片SoC相比,multi-die系统可以加速系统功能的扩展,同时具有降低风险和上市时间、降低系统功耗以及快速创建新产品等优点。埃级芯片可以在multi-die系统中发挥核心作用,支持带宽密集型应用所需的处理能力,而老节点上的芯片可以实现其他普通芯片功能。

半导体工业新的发展方向

如今,芯片上封装的大量组件使其设计和验证过程变得更加复杂。考虑到数以十亿计的埃级晶体管,AI和ML被集成到驱动EDA流的算法中是何等幸运。通过在重复的大规模任务中寻找模式或效率,AI和ML可以发现十亿分之一的错误,如果使用传统的EDA解决方案是不可能实现的。

类似地,ML允许实现周期前端的应用程序(如综合)尽早了解flow中稍后可能发生的情况,因此工程师可以做出先发制人的决策,以在更快的周转时间内将flow引导到最佳解决方案。

除了AI驱动的设计和验证流程外,经过硅验证的IP还可以降低集成风险,同时加快先进半导体设备的上市时间。具有片上监控功能的硅生命周期管理等解决方案可以帮助跟踪芯片整个生命周期的健康状况和性能,触发调制电源电压等方法以延长芯片的使用寿命,并在故障发生之前请求更换。

由于从芯片中挤出更大的PPA变得越来越具有挑战性,工程师们继续寻找改进半导体设计的方法。埃级缩放技术可以为新一代智能互联电子产品提供芯片,这些产品正在影响我们的世界。

原文链接:

https://www.allaboutcircuits.com/industry-articles/how-will-angstrom-scale-chips-advance-the-electronics-industry/

高端微信群介绍 | |

创业投资群 | AI、IOT、芯片创始人、投资人、分析师、券商 |

闪存群 | 覆盖5000多位全球华人闪存、存储芯片精英 |

云计算群 | 全闪存、软件定义存储SDS、超融合等公有云和私有云讨论 |

AI芯片群 | 讨论AI芯片和GPU、FPGA、CPU异构计算 |

5G群 | 物联网、5G芯片讨论 |

第三代半导体群 | 氮化镓、碳化硅等化合物半导体讨论 |

存储芯片群 | DRAM、NAND、3D XPoint等各类存储介质和主控讨论 |

汽车电子群 | MCU、电源、传感器等汽车电子讨论 |

光电器件群 | 光通信、激光器、ToF、AR、VCSEL等光电器件讨论 |

渠道群 | 存储和芯片产品报价、行情、渠道、供应链 |

< 长按识别二维码添加好友 >

加入上述群聊

带你走进万物存储、万物智能、

万物互联信息革命新时代