点击“意法半导体PDSA",关注我们!

摘要

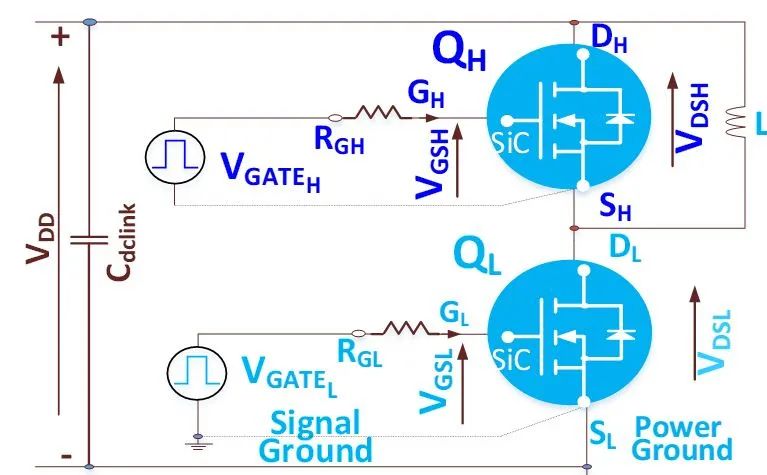

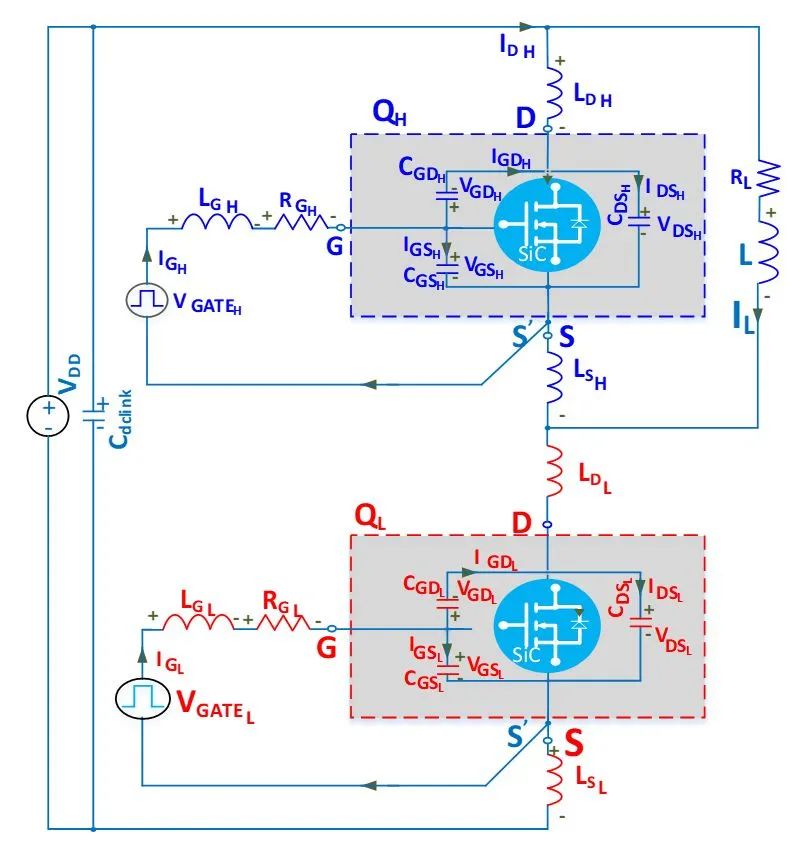

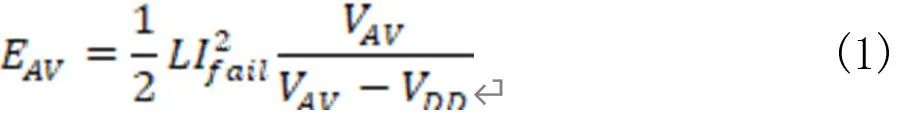

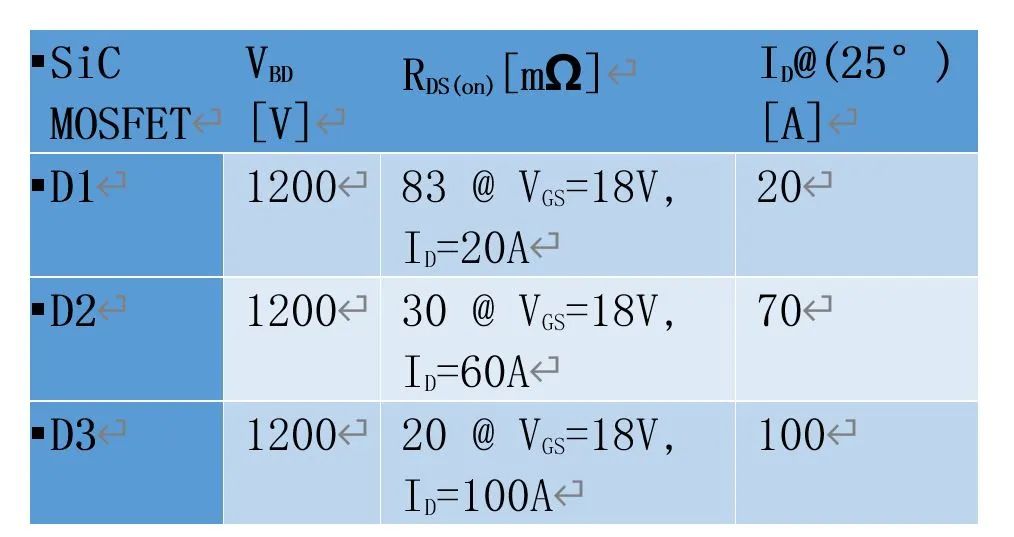

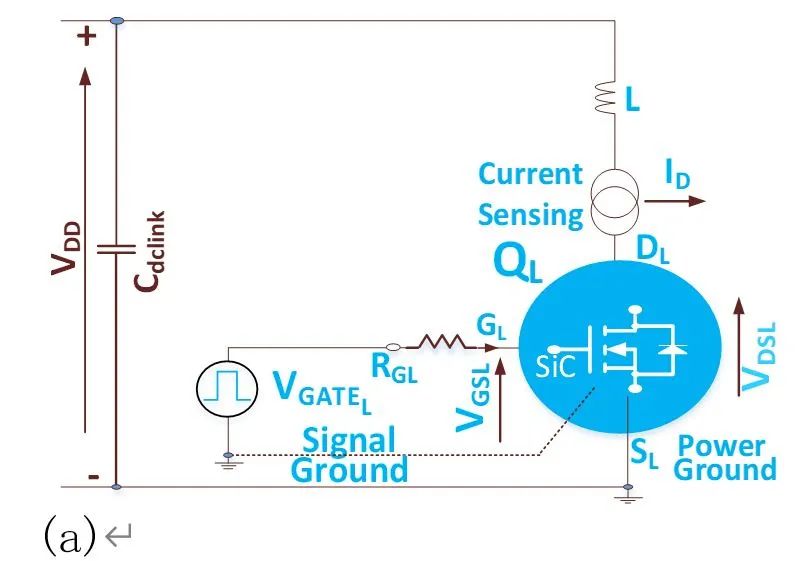

本文将探讨如何在雪崩工作条件下评估SiC MOSFET的鲁棒性。MOSFET功率变换器,特别是电动汽车驱动电机功率变换器,需要能够耐受一定的工作条件。如果器件在续流导通期间出现失效或栅极驱动命令信号错误,就会致使变换器功率开关管在雪崩条件下工作。因此,本文通过模拟雪崩事件,进行非钳位感性负载开关测试,并使用不同的SiC MOSFET器件,按照不同的测试条件,评估技术的失效能量和鲁棒性。

引语

雪崩事件

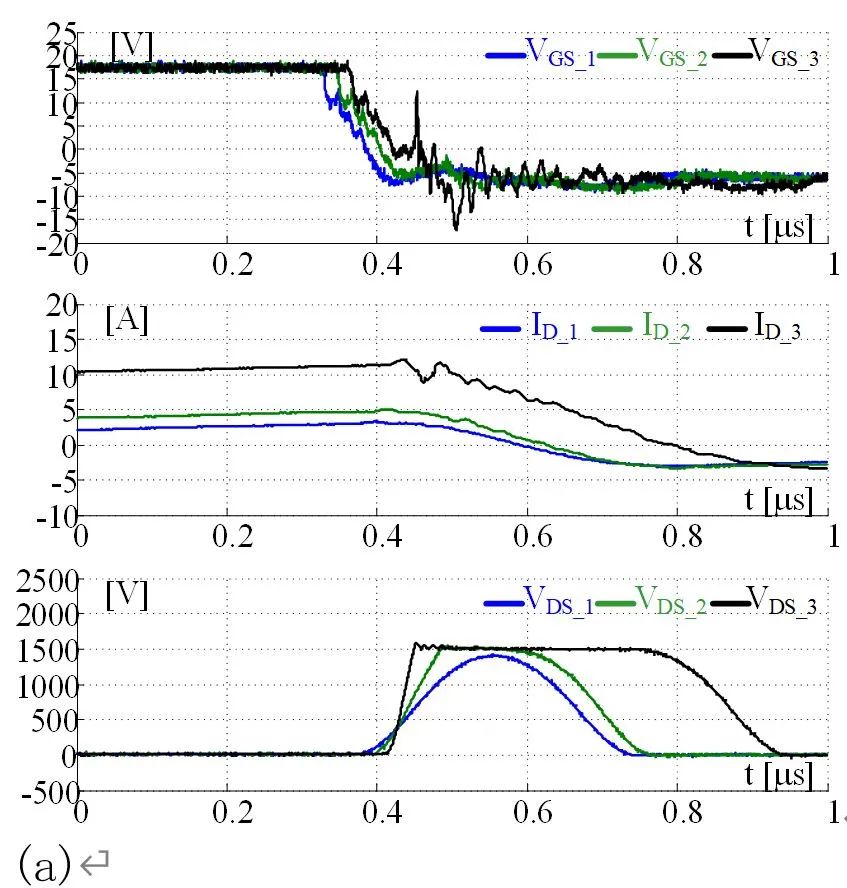

(a)

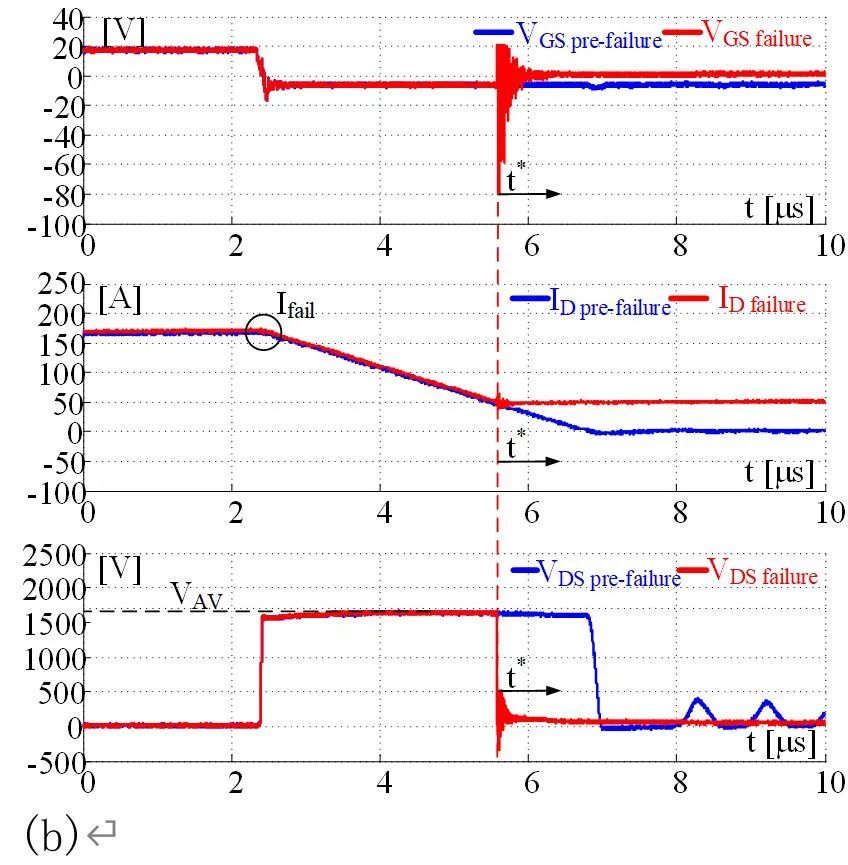

(b)

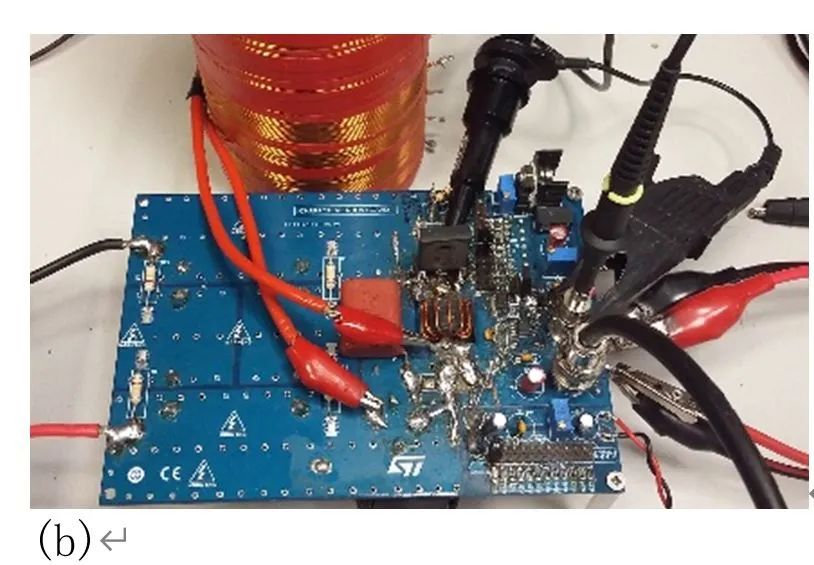

鲁棒性评估和雪崩测试

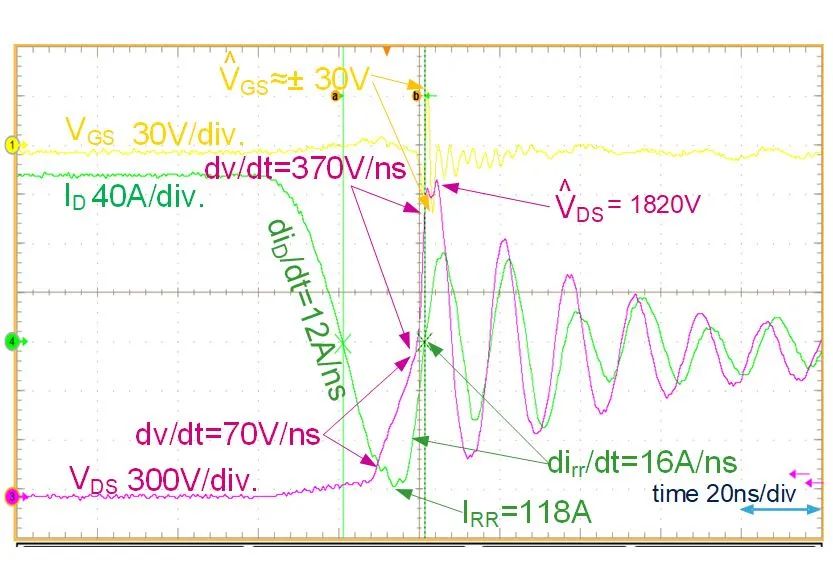

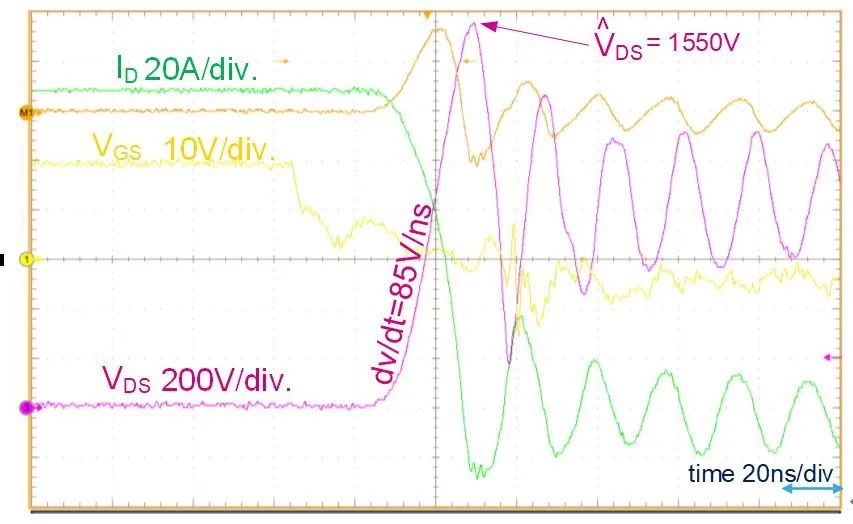

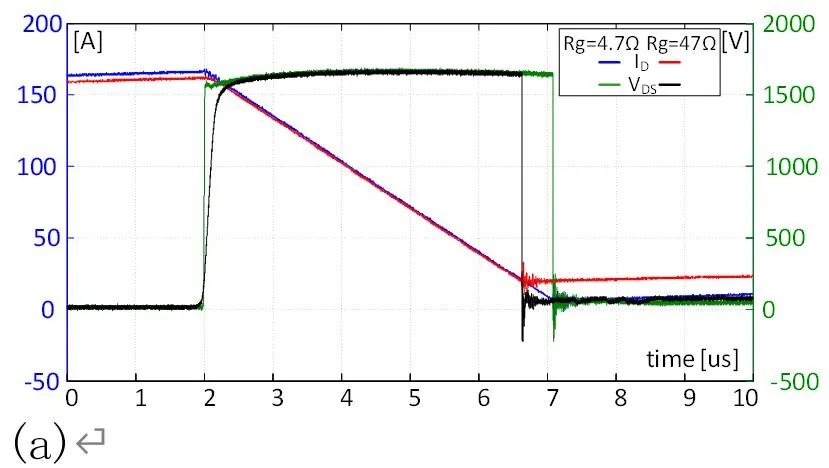

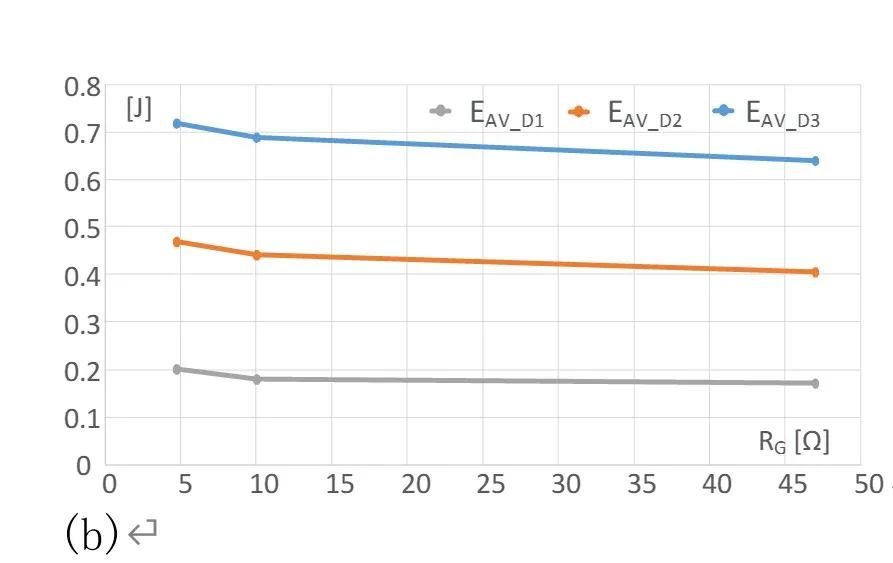

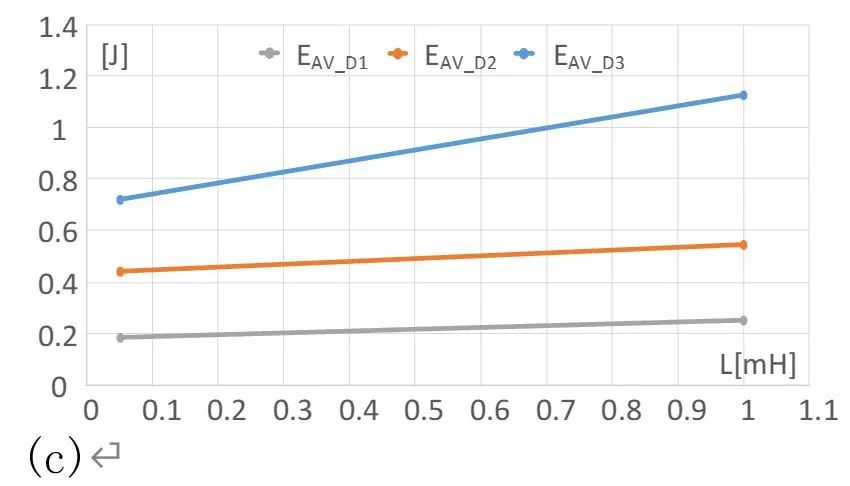

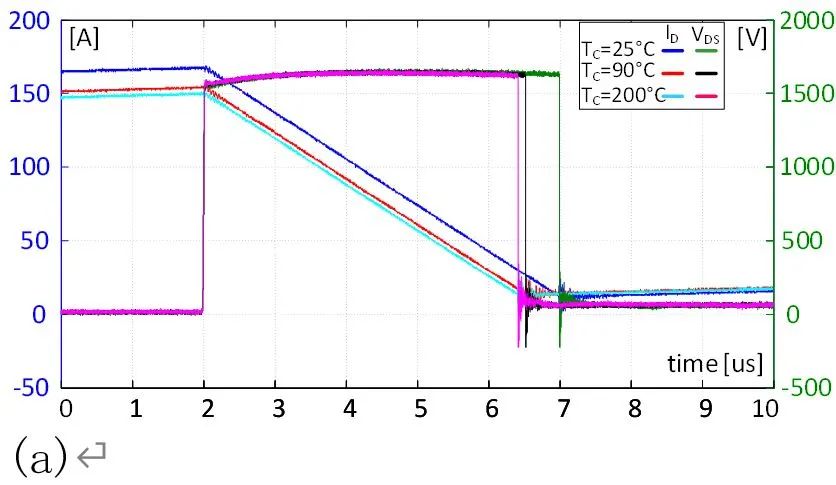

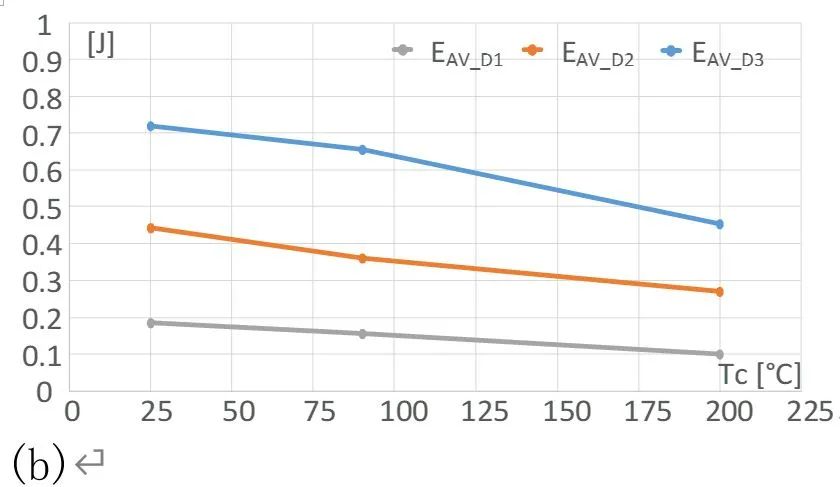

为了清楚起见,只给出了RG =4.7Ω和47Ω两种情况的波形。我们观察到,失效电流不受RGL的影响。图6(b)显示了D1,D2和D3三组的平均EAV。

注意到EAV失效能量略有降低,可忽略不计,因此,可以得出结论,在UIS测试条件下,这些SiC MOSFET的鲁棒性与RG无关。

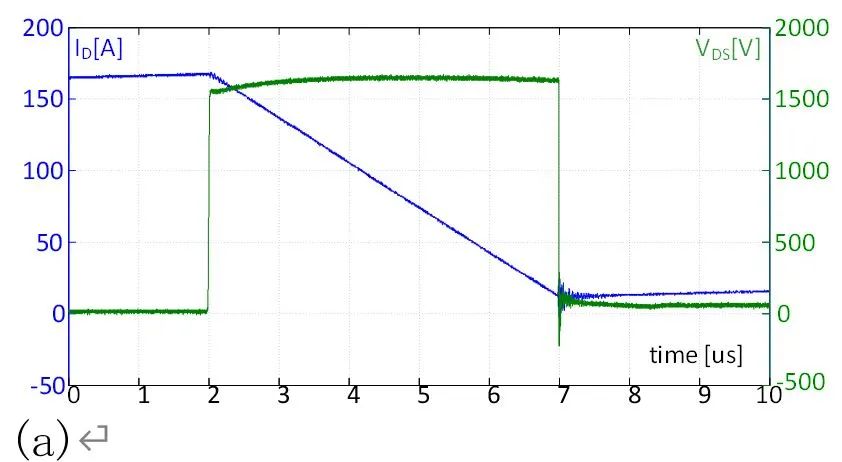

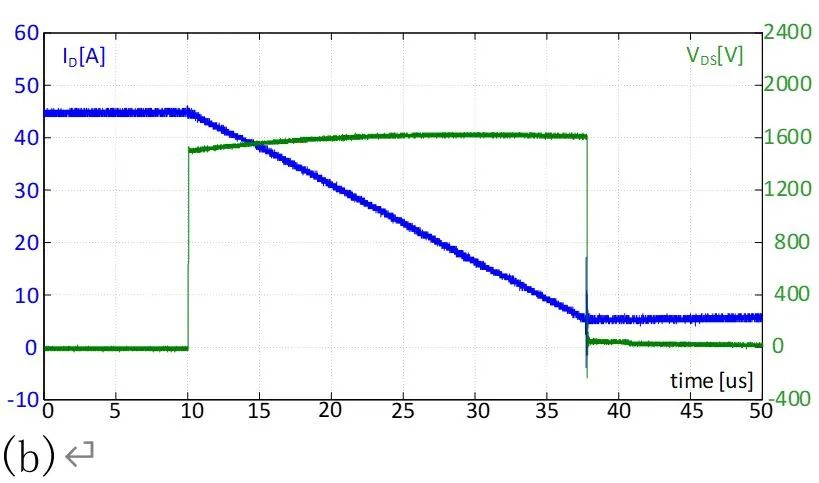

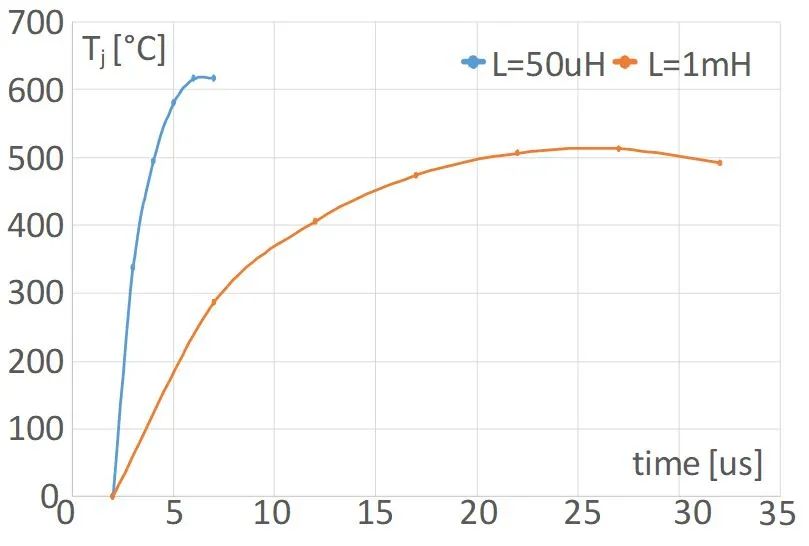

图7(a)和(b)所示是按照测试条件B,在L=50H和1mH时,各做一次UIS测试的失效波形,为简单起见,只从SiC MOSFET D3中抽取一个典型样品做实验。

在提高负载电感后,电感器储存的能量增加,因此,失效电流减小。

【图7:UIS对L最终测试结果 (a) 在L=50H时, D3样品的VDS 和 ID 典型值 (b)在L=1mH时, D3样品的VDS 和 ID 典型值 (c) 平均失效能量EAV.】

结论

本文探讨了在SiC MOSFET应用中需要考虑的可能致使功率器件处于雪崩状态的工作条件。为了评估SiC MOSFET的鲁棒性,本文通过实验测试评估了雪崩能量,最后还用三款特性不同的SiC MOSFET做对比测试,定义导致器件失效的最大雪崩能量。雪崩能量与芯片面积成正比,并且是栅极电阻、负载电感和外壳温度的函数。

这种在分立器件上进行的雪崩耐量分析,引起使用电源模块开发应用的设计人员的高度关注,因为电源模块是由许多并联芯片组成,这些芯片的鲁棒性需要高度一致,必须进行专门的测试分析。此外,对于特定的应用,例如,汽车应用,评估雪崩条件下的鲁棒性,可以考虑使用单脉冲雪崩测试和重复雪崩测试方法。这是一个重点课题,将是近期评估活动的目标。

[4] A. Hanif, Y. Yu, D. DeVoto and F.Khan “A Comprehensive Review Toward the State-of-the-Art in Failure and Lifetime Predictions of Power Electronic Devices,” IEEE Trans. On Pow. Elect.vol.34, no.5, pp. 4729- 4746 May2019.

[5] B. Mirafzal “Survey of Fault-Tolerance Techniques for Three-Phase Voltage Source Inverters,” IEEE Trans. on Ind. Elec. Vol.61, no.10,pp. 5192-5202, Oct.2014.

[6] F.Richardeau, P. Baudesson, T. A. Meynard “Failures-Tolerance and Remedial Strategies of a PWM Multicell Inverter,” IEEE Trans. Power Elec., vol. 17, no.6, pp 905-912, Nov.2002.

[7] A. Fayyaz, G. Romano, J. Urresti, M.Riccio, A. Castellazzi, A. Irace, and N. Wright, “A Comprehensive Study on the Avalanche Breakdown Robustness of Silicon Carbide Power MOSFETs”, Energies,vol. 10, no. 4, pp. 452-466, 2017.

[8] M.D. Kelley, B. N. Pushpakaran and Stephen B. Bayne “Single-Pulse Avalanche Mode Robustness of Commercial 1200 V/80 mΩ SiC MOSFETs,” IEEE Trans. On Pow. Elec.Vol. 32, no.8, pp. 6405-6415, Aug. 2017.

[9] I. Dchar, M.Zolkos, C. Buttay, H. Morel “Robustness of SiC MOSFET under Avalanche Conditions”, 2017 IEEE Applied Power Electronics Conference and Exposition (APEC)

[10]N. Ren, H. Hu, K. L. Wang, Z. Zuo, R. Li, K. Sheng“Investigation on Single Pulse Avalanche Failure of 900V SiC MOSFETs” Int. Symp. On Power Semic. Dev.& ICs, May 13-17, 2018.

[11]J. Wei, S. Liu, S. Li, J. Fang, T. Li, and W. Sun“Comprehensive Investigations on Degradations of Dynamic Characteristics for SiC Power MOSFETs under Repetitive Avalanche Shocks,” IEEE Trans. on Power Elec. Vol.: 34, no: 3, pp. 2748– 2757, March 2019

[12]J. Hu, O. Alatise, J. Angel Ortiz Gonzalez, R.Bonyadi, P. Alexakis, L. Ran and P. Mawby “Robustness and Balancing of Parallel-Connected Power Devices: SiC Versus Cool MOS,” IEEE Trans. On Ind. Elec.Vol. 63, no.4, pp.2092-2102 April 2016.

[13]M. Nawaz“Evaluation of SiC MOSFET power modules under unclamped inductive switching test environment”, Journal of Microelec. Reliability, vol. 63, pp. 97-103,2016.

[14]H. Chen, D. Divan “High Speed Switching Issues of HighPower Rated Silicon-Carbide Devices and the Mitigation Methods” 2015 ECCE,pp.2254-2260.

[15]M.Pulvirenti, L. Salvo, G. Scelba, A.G. Sciacca, M. Nania, G. Scarcella, M.Cacciato, “Characterization and Modeling of SiC MOSFETs Turn On in a Half Bridge Converter”2019 IEEE En. Conv. Cong. and Expo. (ECCE2019).

[16]M. Pulvirenti, G. Monotoro, M.Nania, R. Scollo, G. Scelba, M. Cacciato, G. Scarcella, L. Salvo “Analysis of Transient Gate-Source Over Voltages in Silicon Carbide MOSFET Power Devices” 2018IEEE En. Conv. Cong. and Expo. (ECCE2018).

[17]J. Mari, F. Carastro, M.-J. Kell, P.Losee, T. Zoels “Diode snappiness from a user’s perspective” 2015, 17th European Conference on Power Electronicsand Applications (EPE'15 ECCE-Europe).

[18]R. Wu, F. Blaabjerg, H. Wang, M.Liserre, “Overview of catastrophic failures of freewheeling diodes in power electronic circuits”, Microelectronics Reliability, vol. 53, no.9-11, 2013,pp.:1788-1792.

“阅读原文”,了解更多。