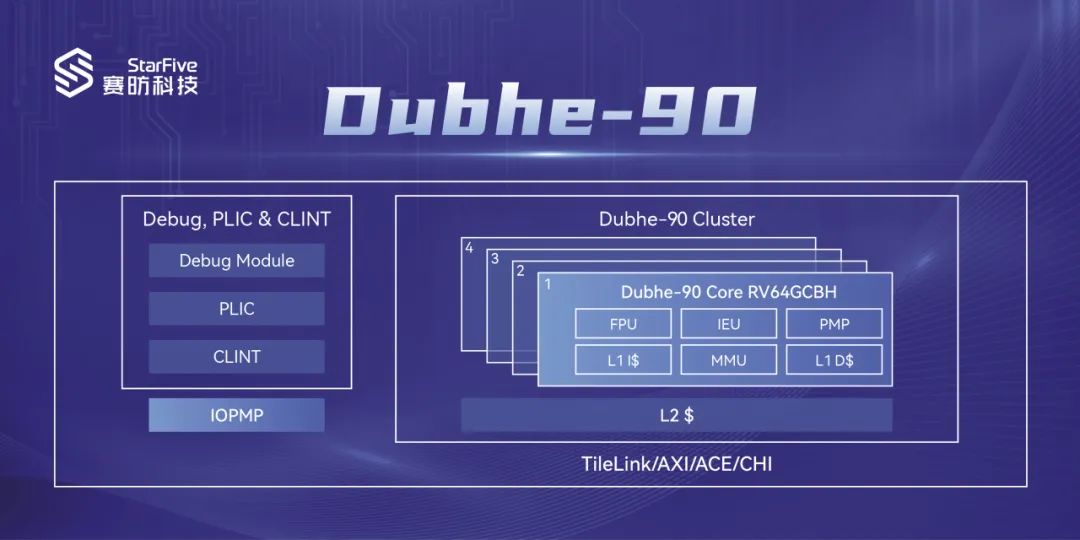

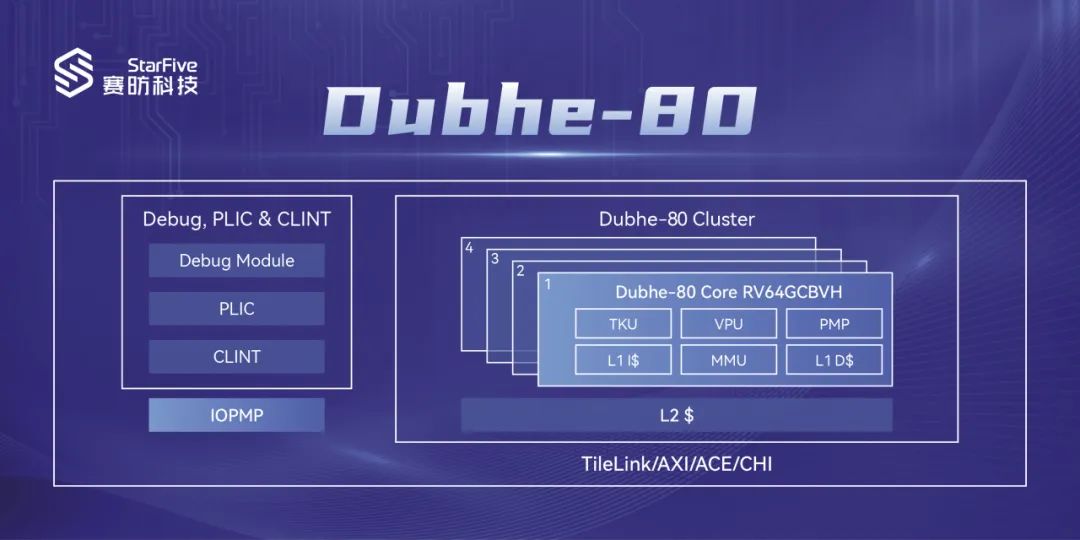

赛昉科技正式发布两款自主研发的高性能RISC-V处理器内核新产品:昉·天枢-90(Dubhe-90)与昉·天枢-80(Dubhe-80)。Dubhe-90主打极致性能,是Dubhe Max Performance系列旗舰产品;Dubhe-80主打高能效比,是Dubhe Efficiency Performance系列首款产品。

《46份智能网卡和DPU合集》

375+份重磅ChatGPT专业报告

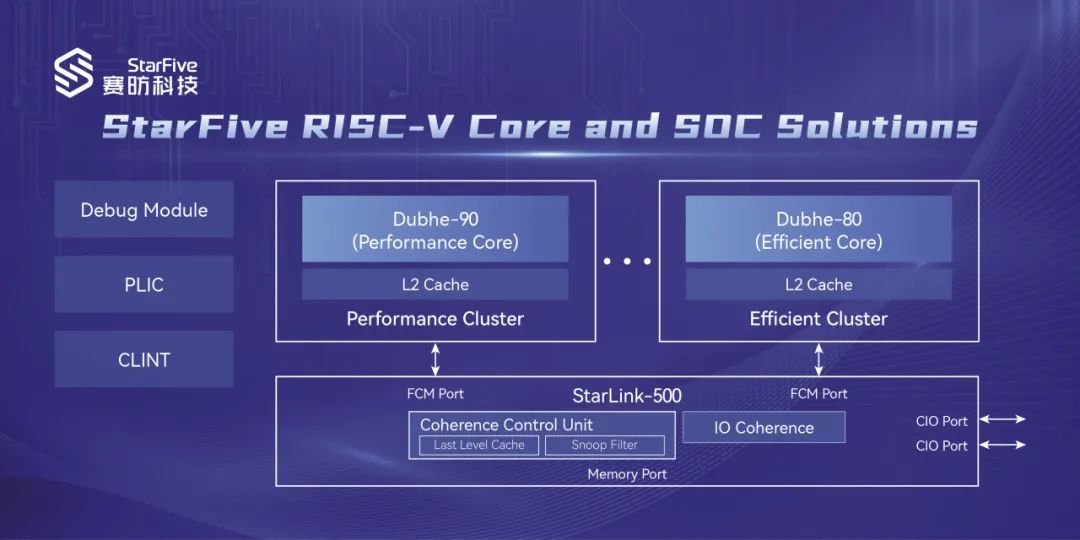

1、基于Python的“RISC-V+通用AI”SoC框架PyYard.pdf 2、DMR:一款兼容RISC-V架构的乱序超标量通用处理器核.pdf3、NutShell-本科生设计的可运行Linux的 RISC-V芯片.pdf 4、RISC-V Vector 及定制指令实践.pdf 6、RISC-V 向量扩展在Clang_LLVM中的支持.pdf 7、RISC-V生态发展态势及国内厂商的多维布局.pdf1、内核架构意义凸显,RISC-V 现新机.pdf 3、基于RISC-V指令集的 Egret处理器设计.pdf 5、基于图形化EDA设计的RISC-V教学实践.pdf 7、开源开放的RISC-V嵌入式软件平台探索.pdf与此同时,基于Dubhe-90、Dubhe-80以及赛昉科技自主研发的片上一致性互联IP——昉·星链-500(StarLink-500),赛昉科技重磅发布首个国产高性能RISC-V多核子系统IP平台,这也是全球首款RISC-V大小核处理器子系统解决方案,填补了RISC-V领域相应市场的空白。2022年,赛昉科技向客户交付了当时业界性能最高RISC-V CPU Core IP——昉·天枢(Dubhe)。一年后,赛昉科技再次发布性能更高的CPU Core IP——Dubhe-90,性能比肩ARM Cortex-A76,SPECint2006 9.4/GHz,继续保持国产可交付性能最高的商业级RISC-V CPU IP产品的领先位置。Dubhe-90的客户主要来自于PC、高性能网络通讯、机器学习、数据中心等高端应用领域。相较于Dubhe-90,Dubhe-80专为高能效场景而生,在性能差仅为20%的前提下,能效比提升50%,满足移动、桌面、工控、人工智能、汽车等场景的应用需求。随着Dubhe-80的正式推出,赛昉科技首次展现了高性能与高能效双轨迭代的RISC-V CPU Core IP产品路线图。

作为一款基于RISC-V指令集架构的64位商用处理器内核,Dubhe-80采用9+级流水线、三发射、乱序执行的设计,SPECint2006 8.0/GHz,性能超过ARM Cortex-A75。Dubhe-80支持至今最完整的RISC-V指令集,包括RV64GC、位操作扩展B(Bitmanip 1.0)、向量扩展V(Vector 1.0)及虚拟化扩展H(Hypervisor 1.0)等。经过预集成及验证,基于Dubhe-80,赛昉科技可为客户提供内存一致性的Cluster内单核、双核或四核的配置选择,极大简化SoC开发工作。在配套软件方面,赛昉科技能为客户提供裸机SDK、Linux SDK、基于Eclipse的IDE等。“从高性能到高能效,赛昉科技在RISC-V领域持续探索,不断扩充自研RISC-V CPU IP矩阵。”赛昉科技董事长兼CEO徐滔表示:“Dubhe-90与Dubhe-80的推出将进一步扩展RISC-V处理器的应用边界,协同促进RISC-V在端、边、云场景的应用落地。”在SoC设计中,高性能内核与高能效内核的搭配使用,能使芯片在工作中达到最佳的能耗比。基于Dubhe-90、Dubhe-80与StarLink-500,赛昉科技发布首个国产高性能RISC-V多核子系统IP平台解决方案,支持8个核心的一致性协同工作,可被广泛应用于PC、笔记本电脑、移动设备、瘦客户机、NAS、工控机及各类行业终端的主控芯片设计。值得一提的是,赛昉科技高性能RISC-V处理器——昉·惊鸿-8100(JH-8100)便采用了该设计方案。赛昉科技能RISC-V计算平台为客户提供成熟的高性能、高带宽、低延迟的RISC-V芯片系统解决方案,方案包括高性能内核、高能效内核、高速的一致性NoC、RISC-V Trace/Debug调试接口、RISC-V中断控制器(PLIC,CLINT)、功耗管理、安全管理、虚拟化、IO一致性(IO Coherency)和内存子系统等,填补了全球范围内多项RISC-V技术、产品及解决方案空白。1、芯来科技:基于RISC-V的MCU软硬件解决方案2、芯来科技:高可靠高安全性RISC-V处理器设计与实现1、基于Python的“RISC-V+通用AI”SoC框架PyYard.pdf 2、DMR:一款兼容RISC-V架构的乱序超标量通用处理器核.pdf3、NutShell-本科生设计的可运行Linux的 RISC-V芯片.pdf 4、RISC-V Vector 及定制指令实践.pdf 6、RISC-V 向量扩展在Clang_LLVM中的支持.pdf 7、RISC-V生态发展态势及国内厂商的多维布局.pdf1、内核架构意义凸显,RISC-V 现新机.pdf 3、基于RISC-V指令集的 Egret处理器设计.pdf 5、基于图形化EDA设计的RISC-V教学实践.pdf 7、开源开放的RISC-V嵌入式软件平台探索.pdf本号资料全部上传至知识星球,更多内容请登录智能计算芯知识(知识星球)星球下载全部资料。免责申明:本号聚焦相关技术分享,内容观点不代表本号立场,可追溯内容均注明来源,发布文章若存在版权等问题,请留言联系删除,谢谢。请搜索“AI_Architect”或“扫码”关注公众号实时掌握深度技术分享,点击“阅读原文”获取更多原创技术干货。