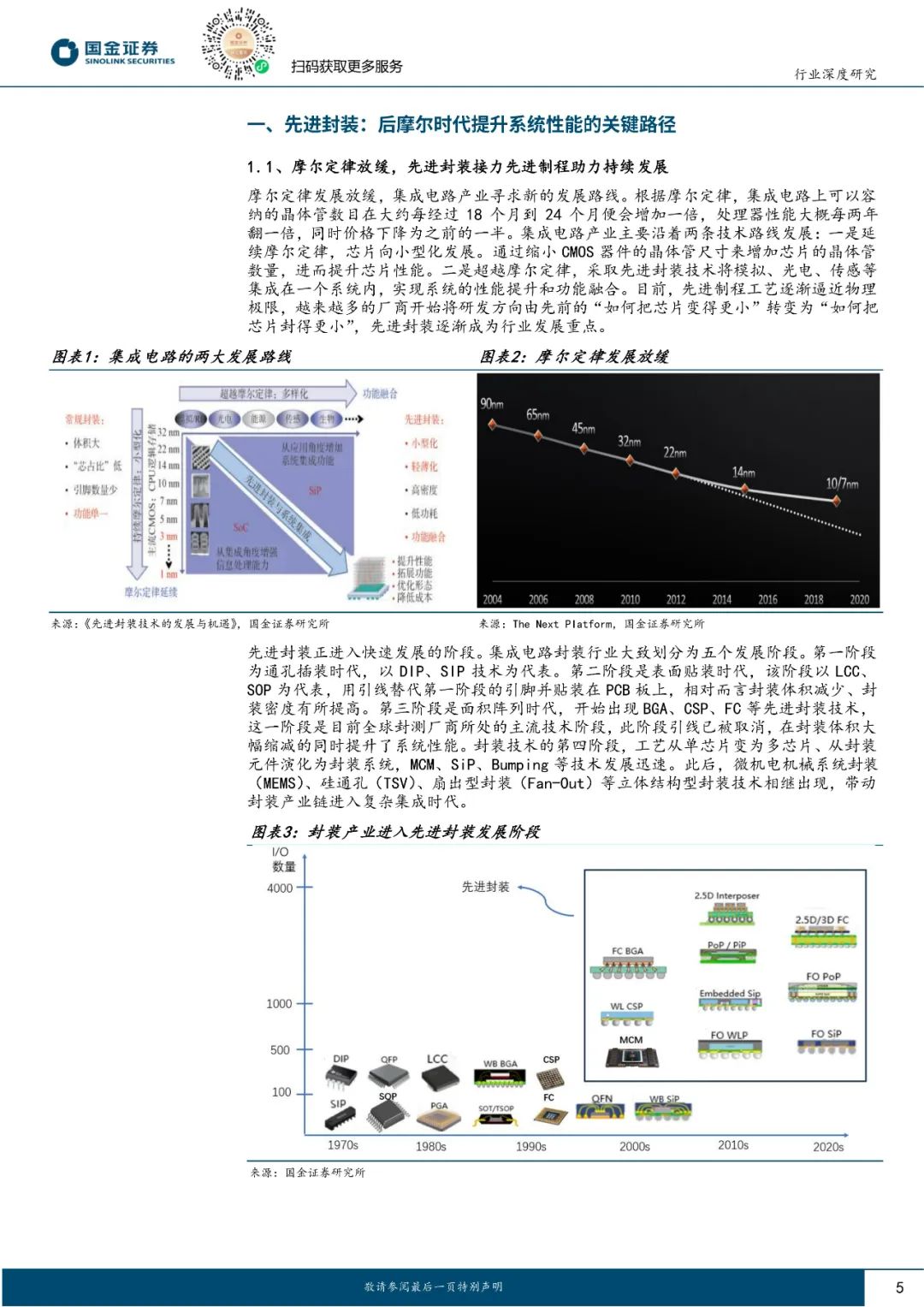

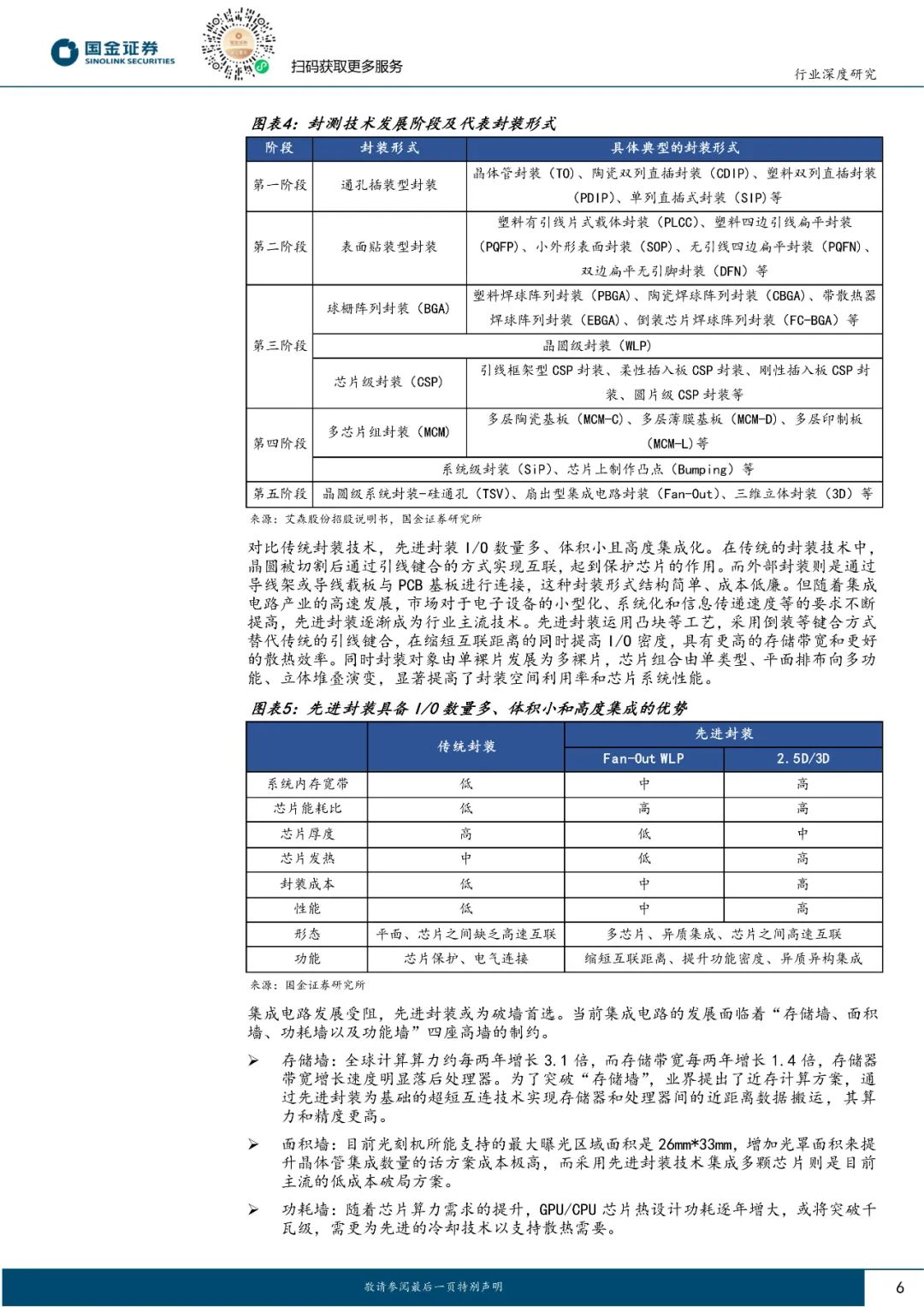

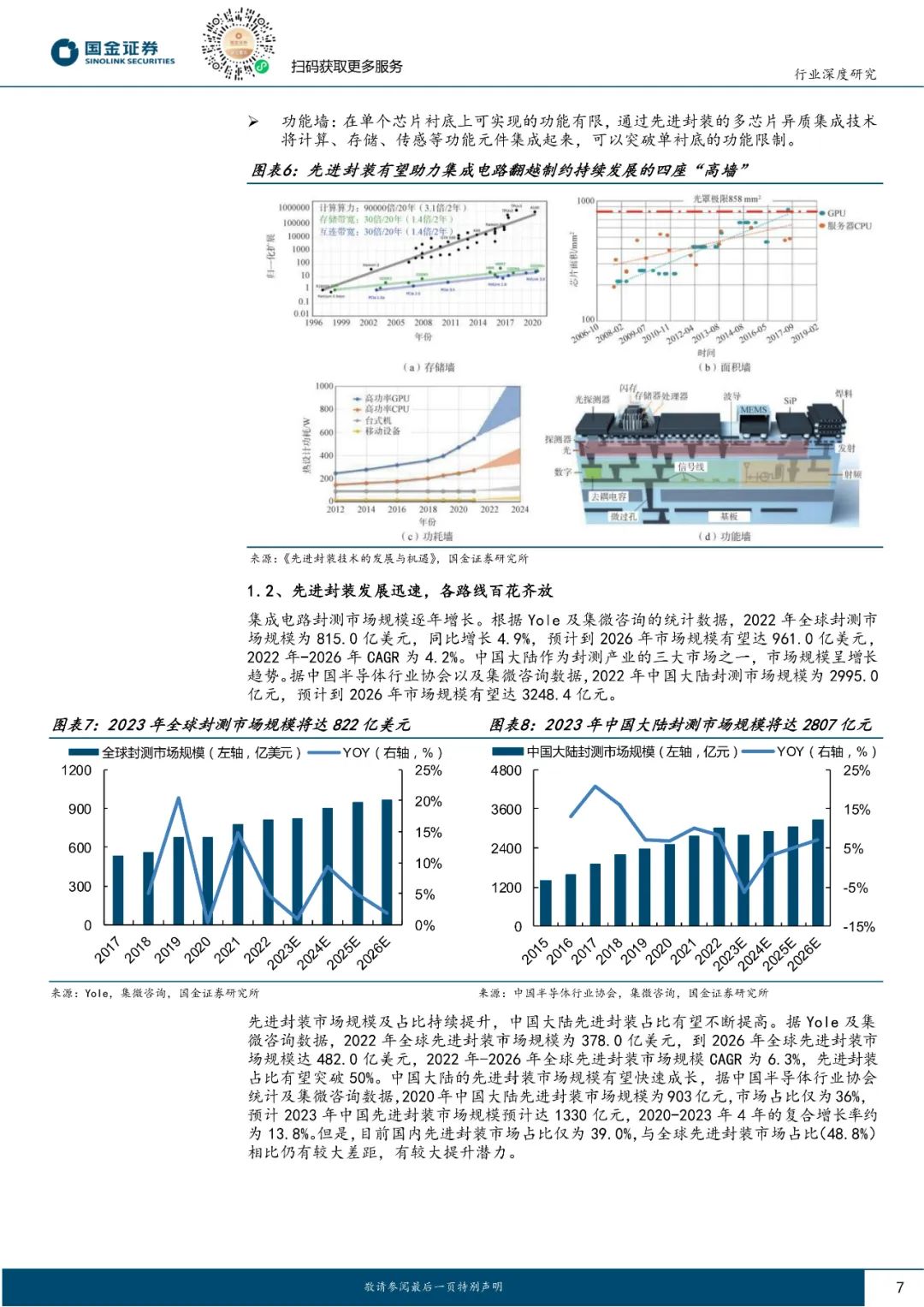

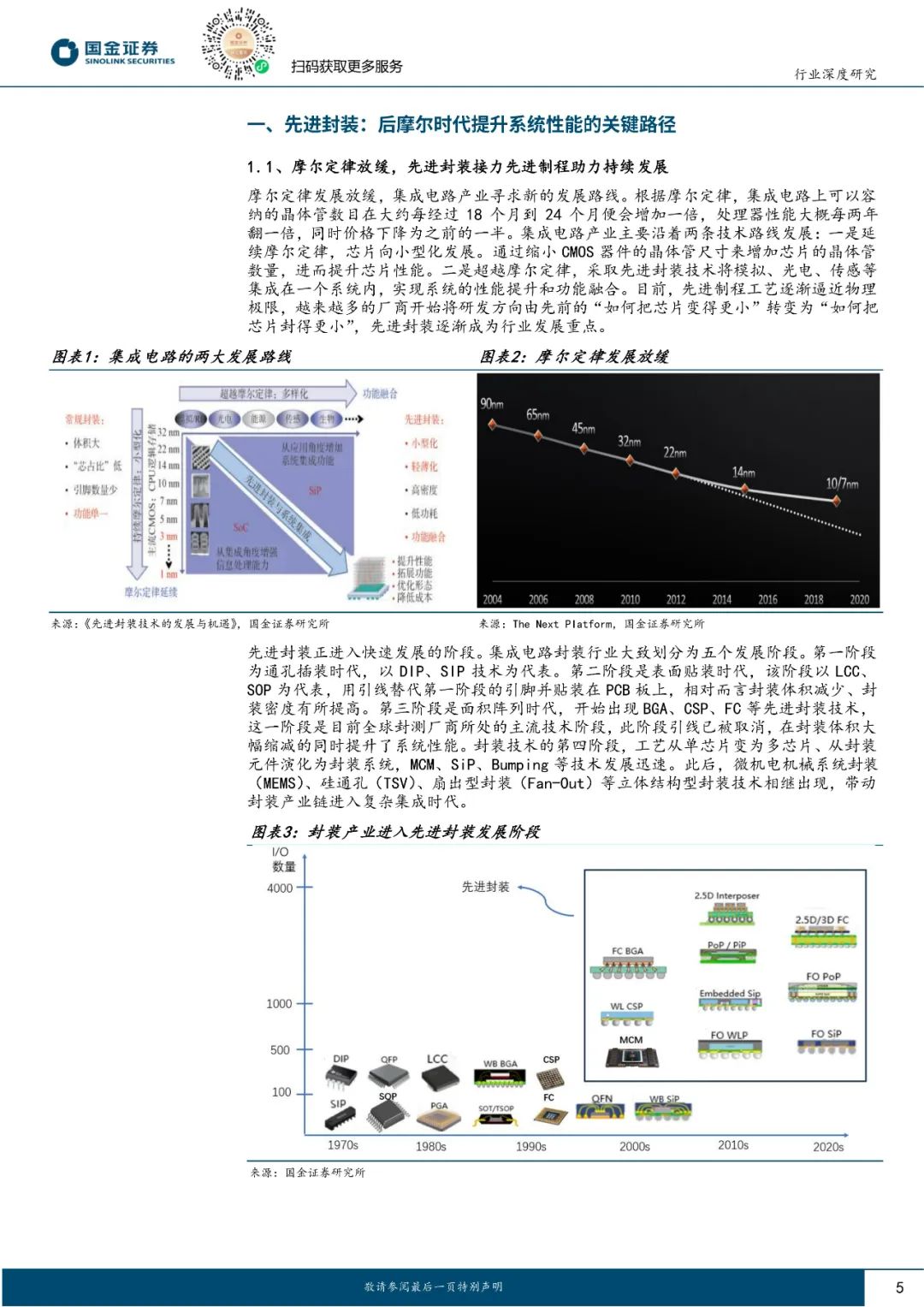

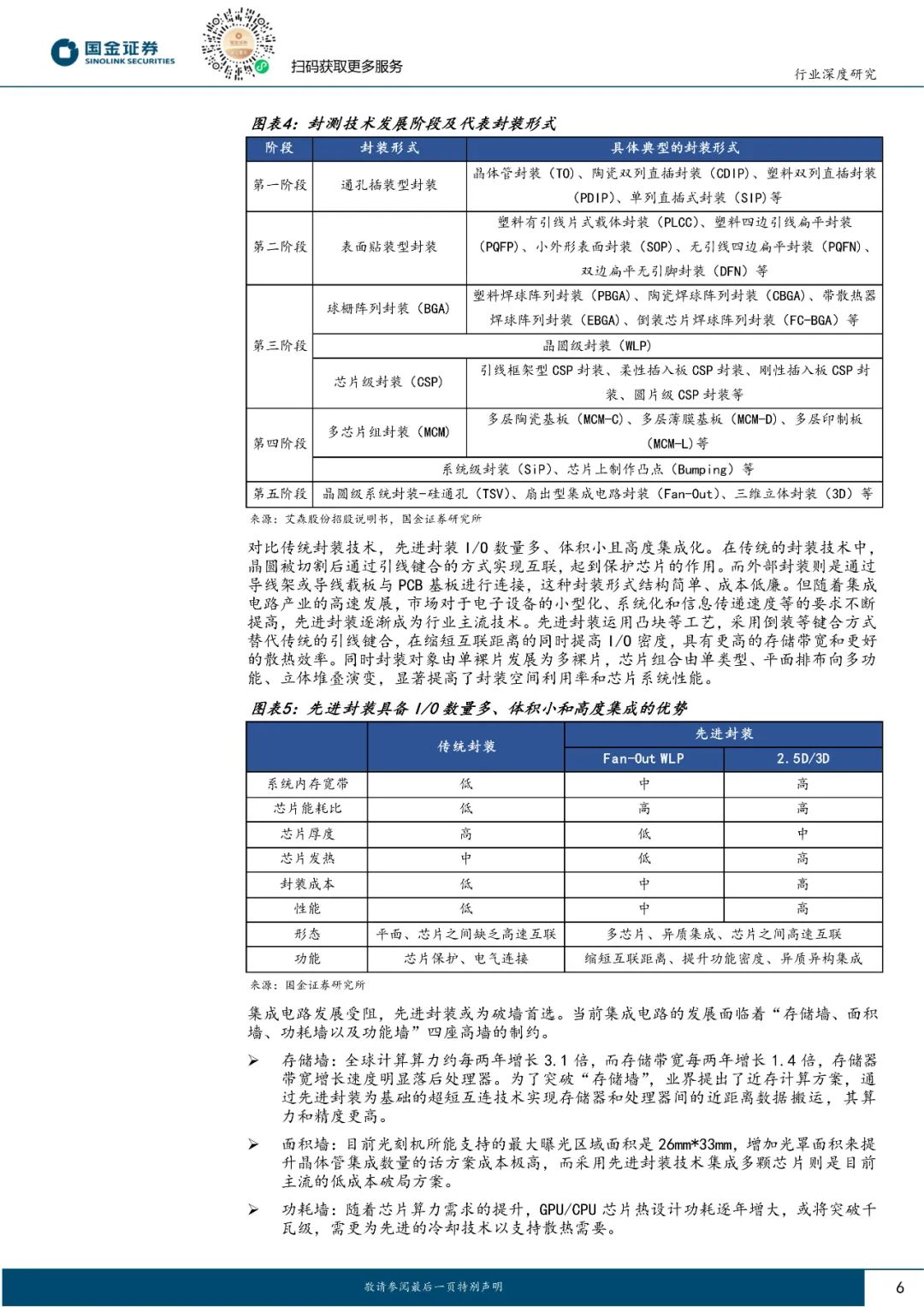

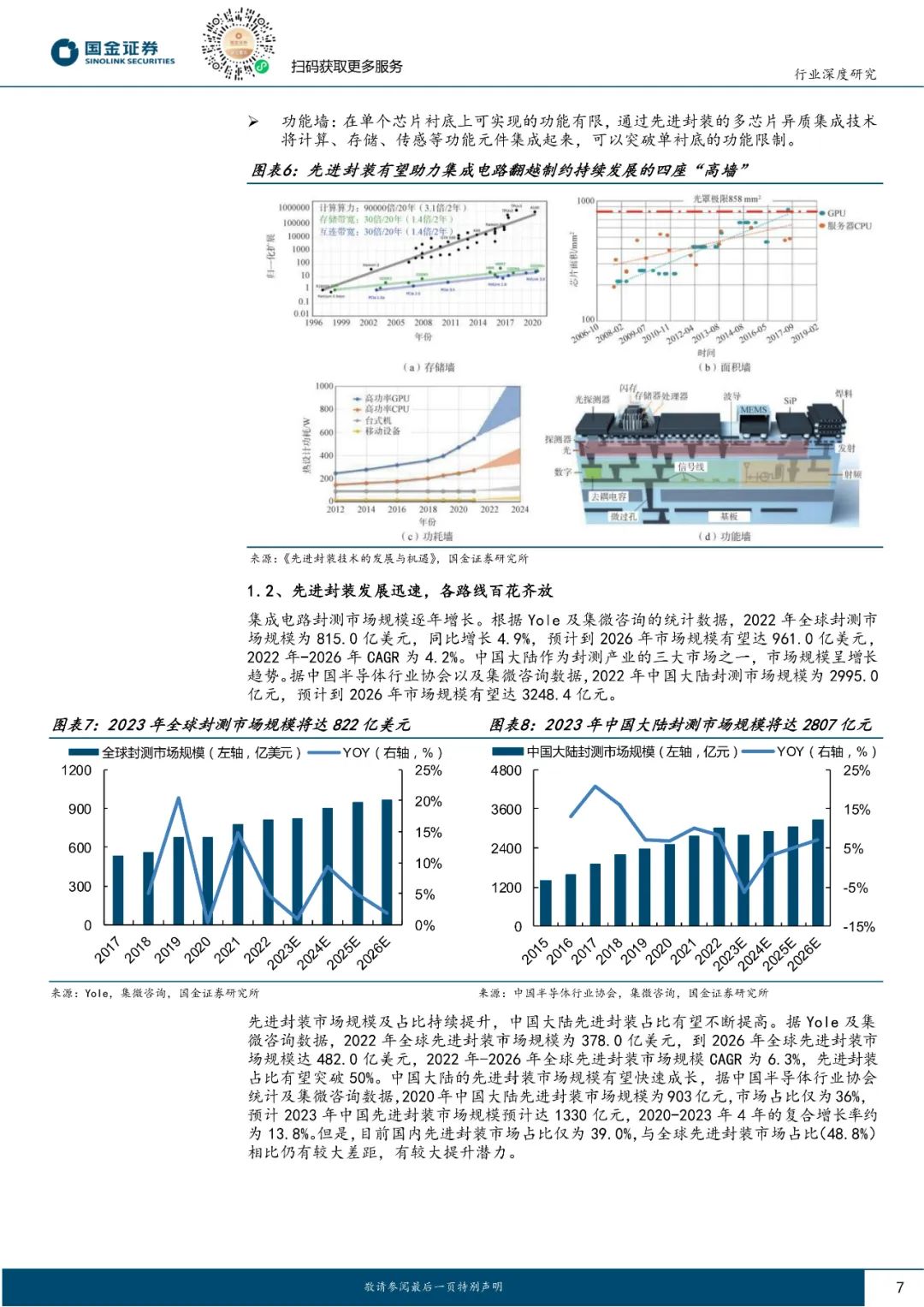

摩尔定律发展放缓,先进制程工艺逐渐逼近物理极限,进一步缩小特征尺寸变得特别困难,众多厂商开始将研发方向由先前的“如何把芯片变得更小”转变为“如何把芯片封得更小”。先进封装因其具备高经济效能、高封装密度以及高度集成的优势,目前正进入快速发展的阶段。晶圆厂在刻蚀等前道步骤的硅通孔技术上积累丰富,因而在 2.5D/3D 封装技术方面较为领先;而以日月光为代表的后道封装厂商则更熟悉异质异构集成,在系统级封装的发展方面更有优势。

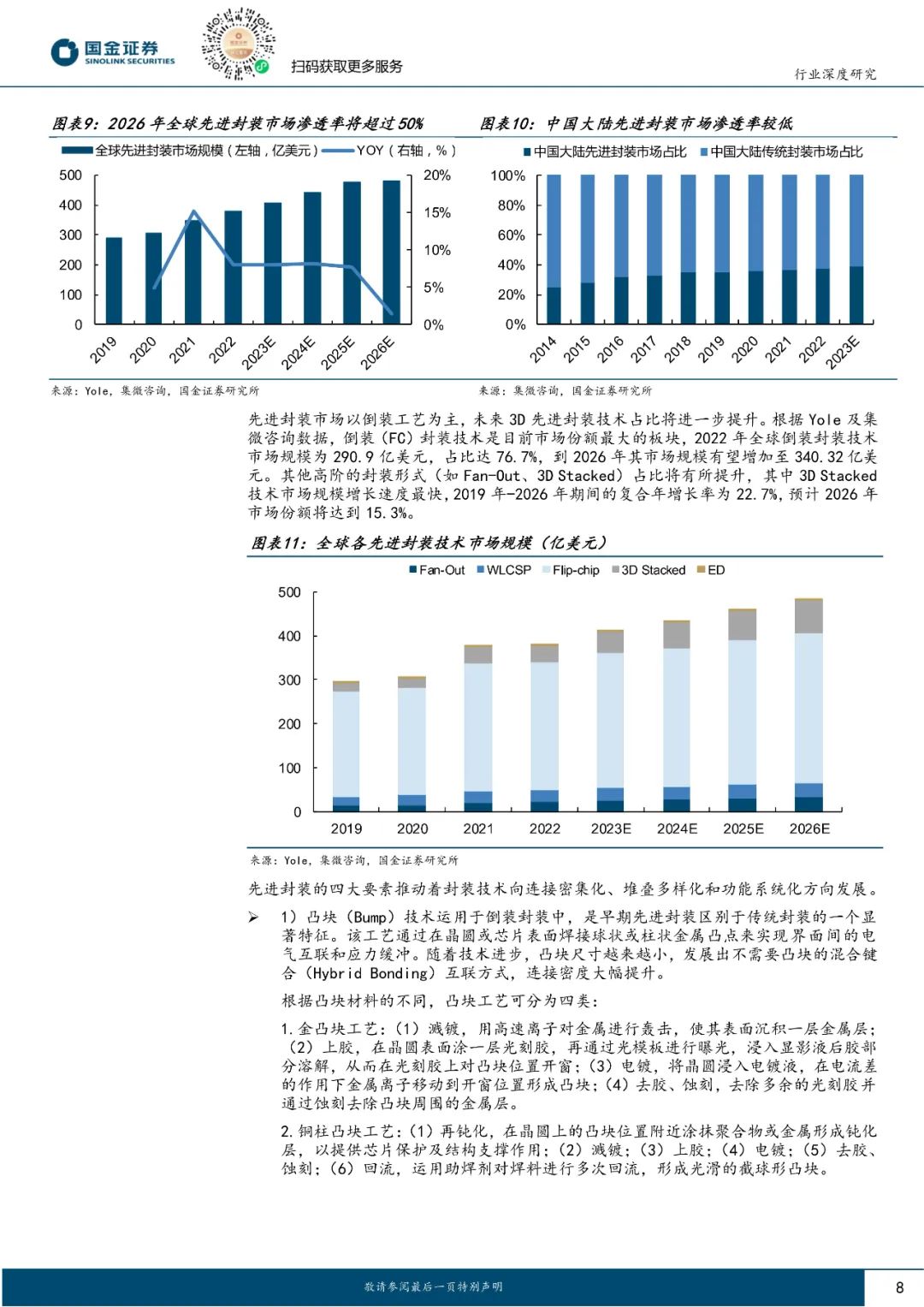

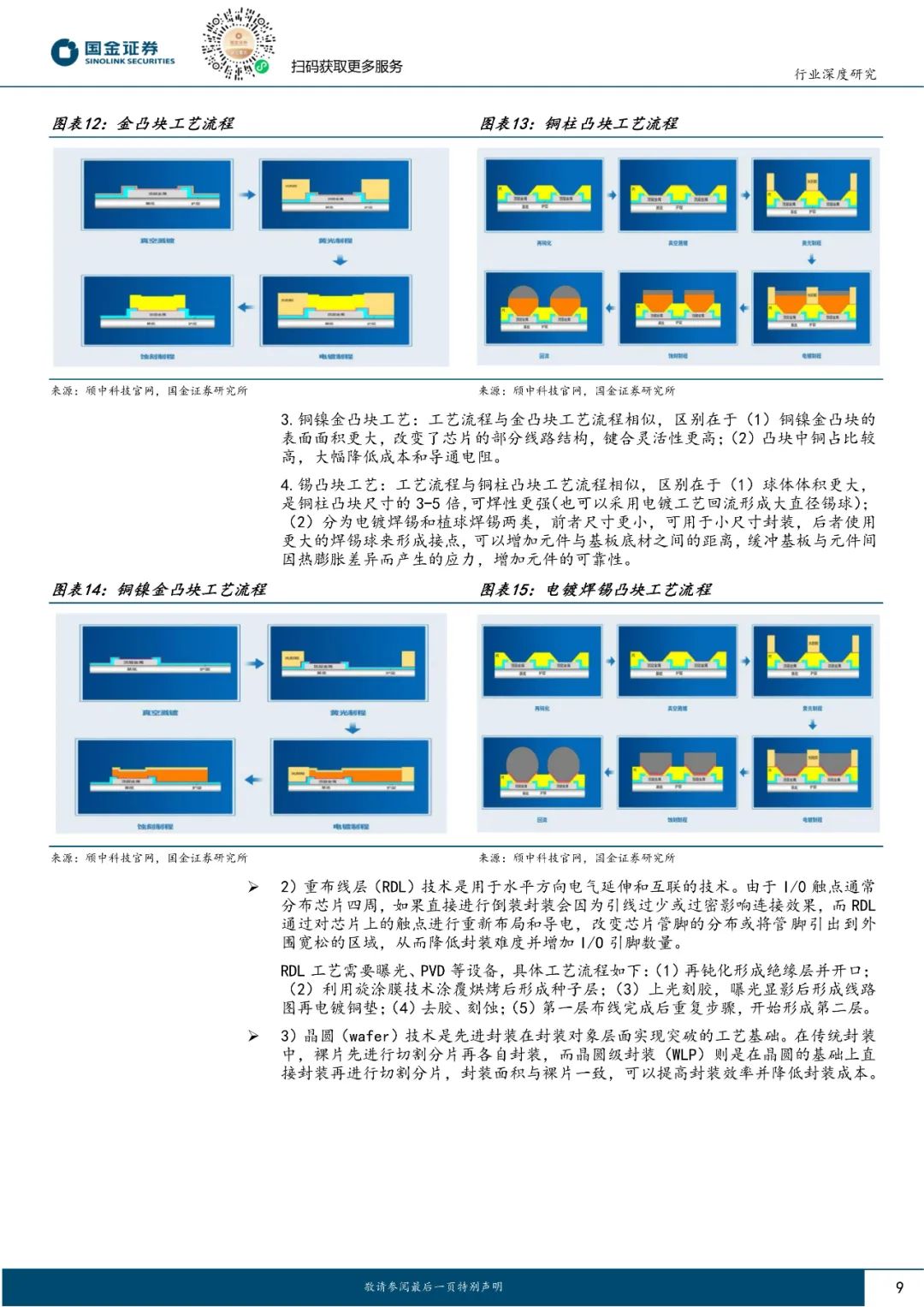

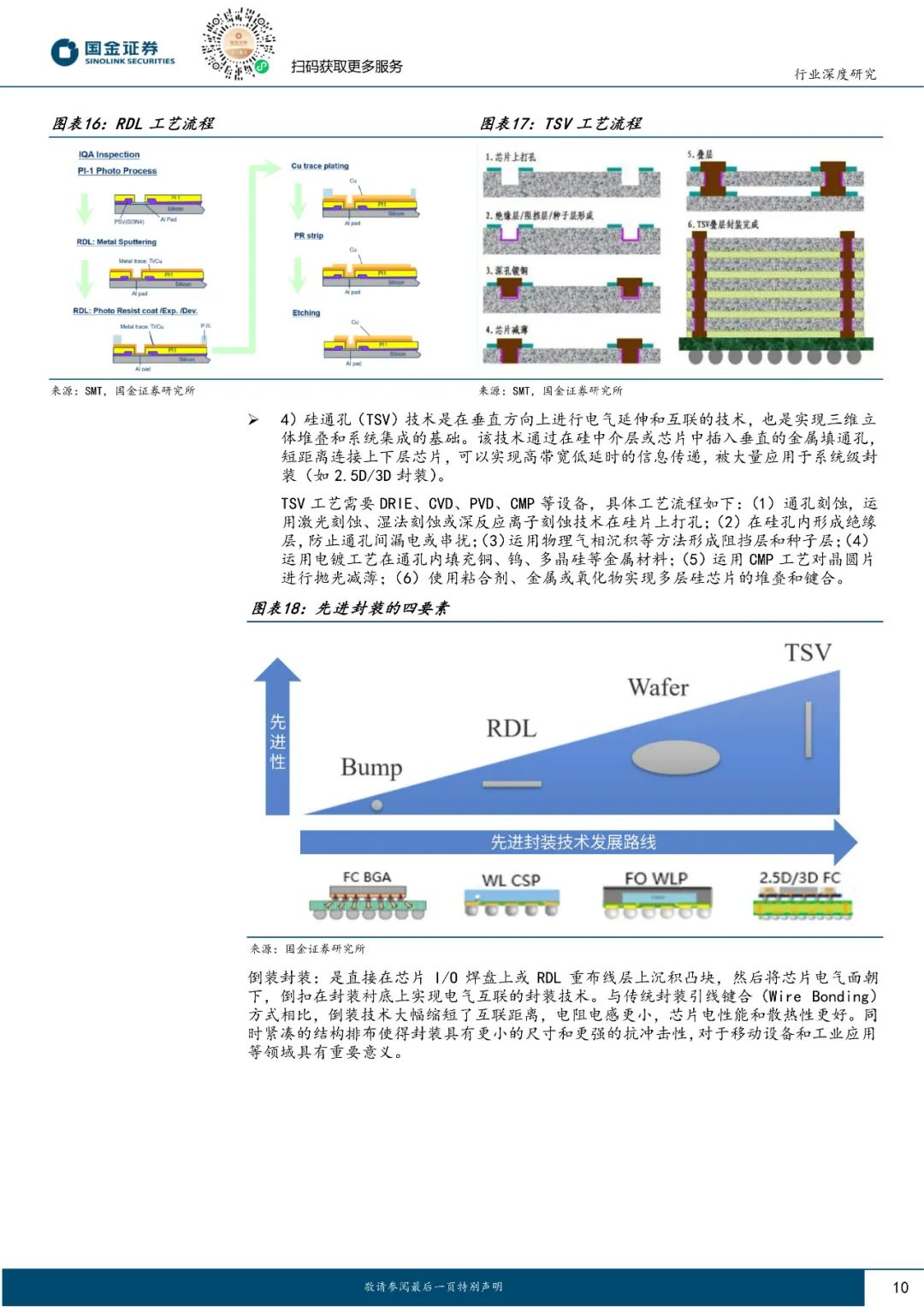

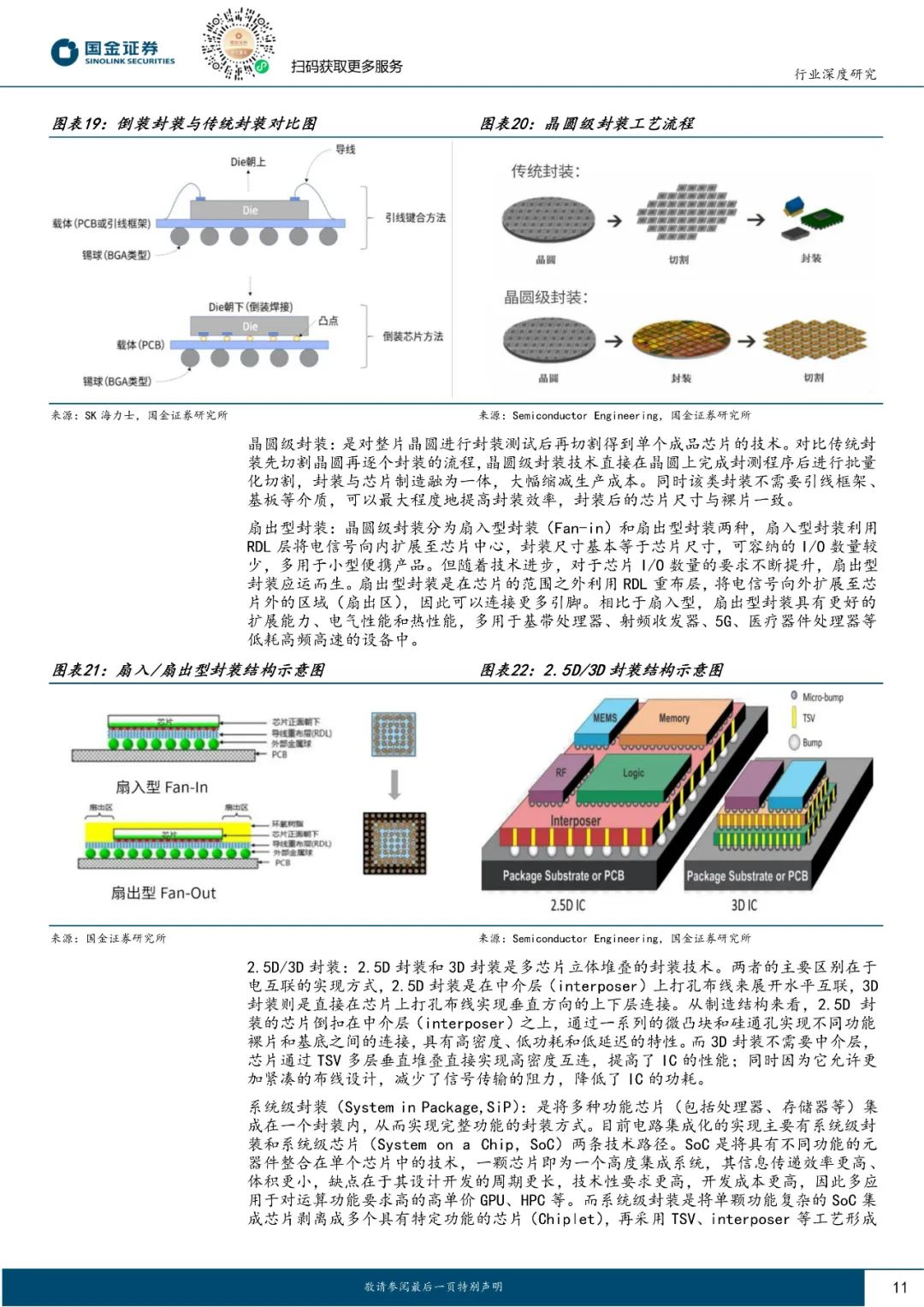

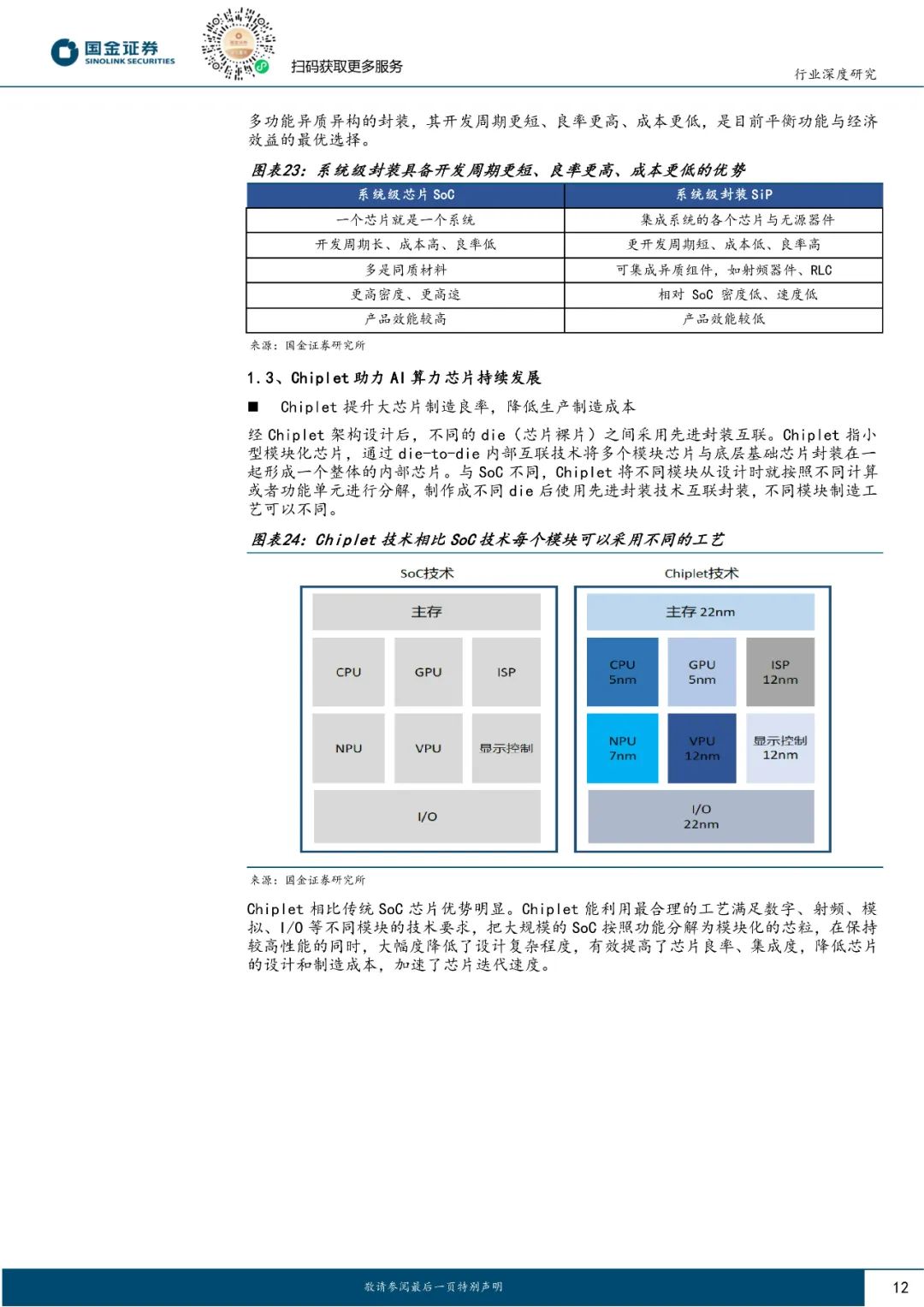

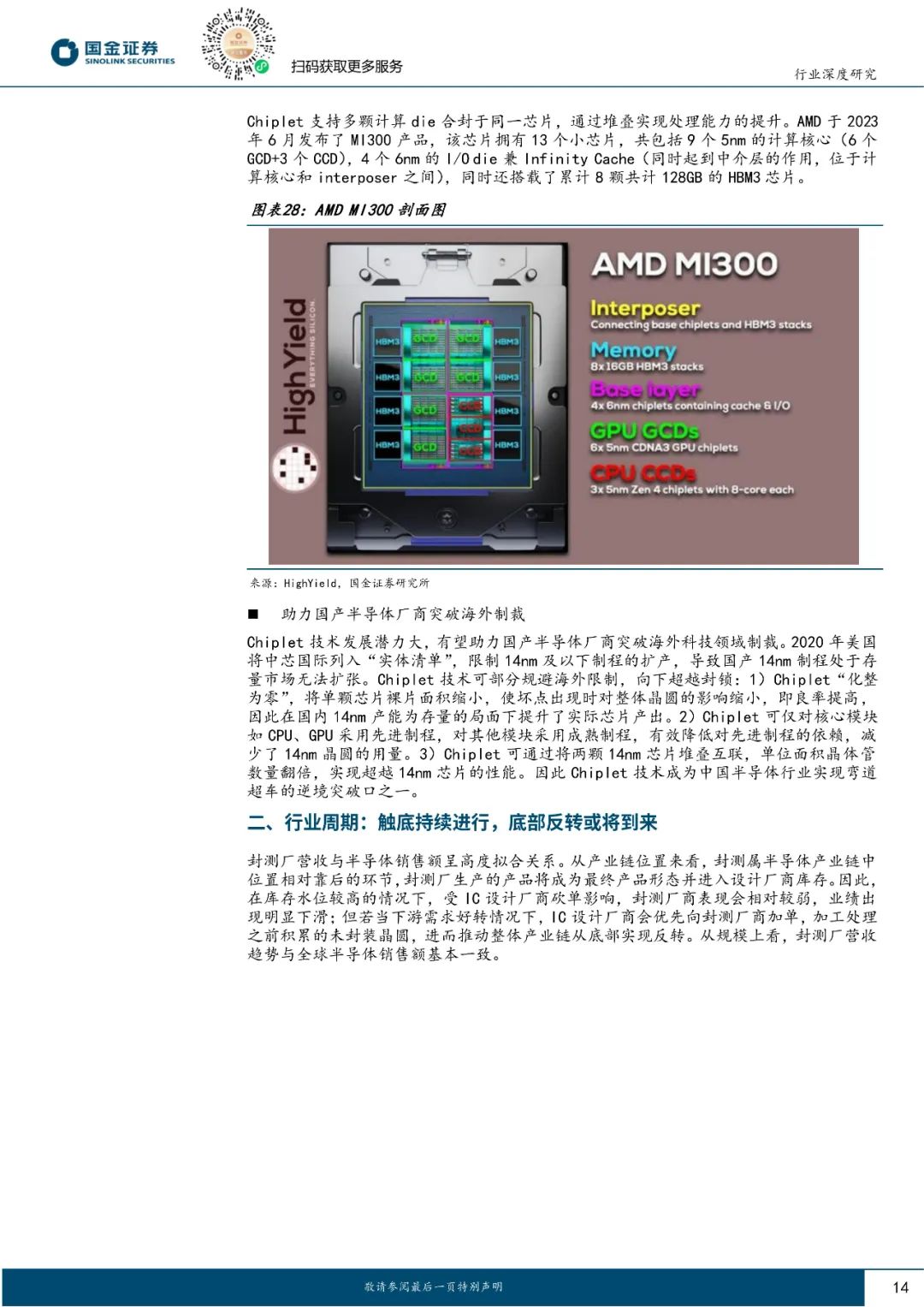

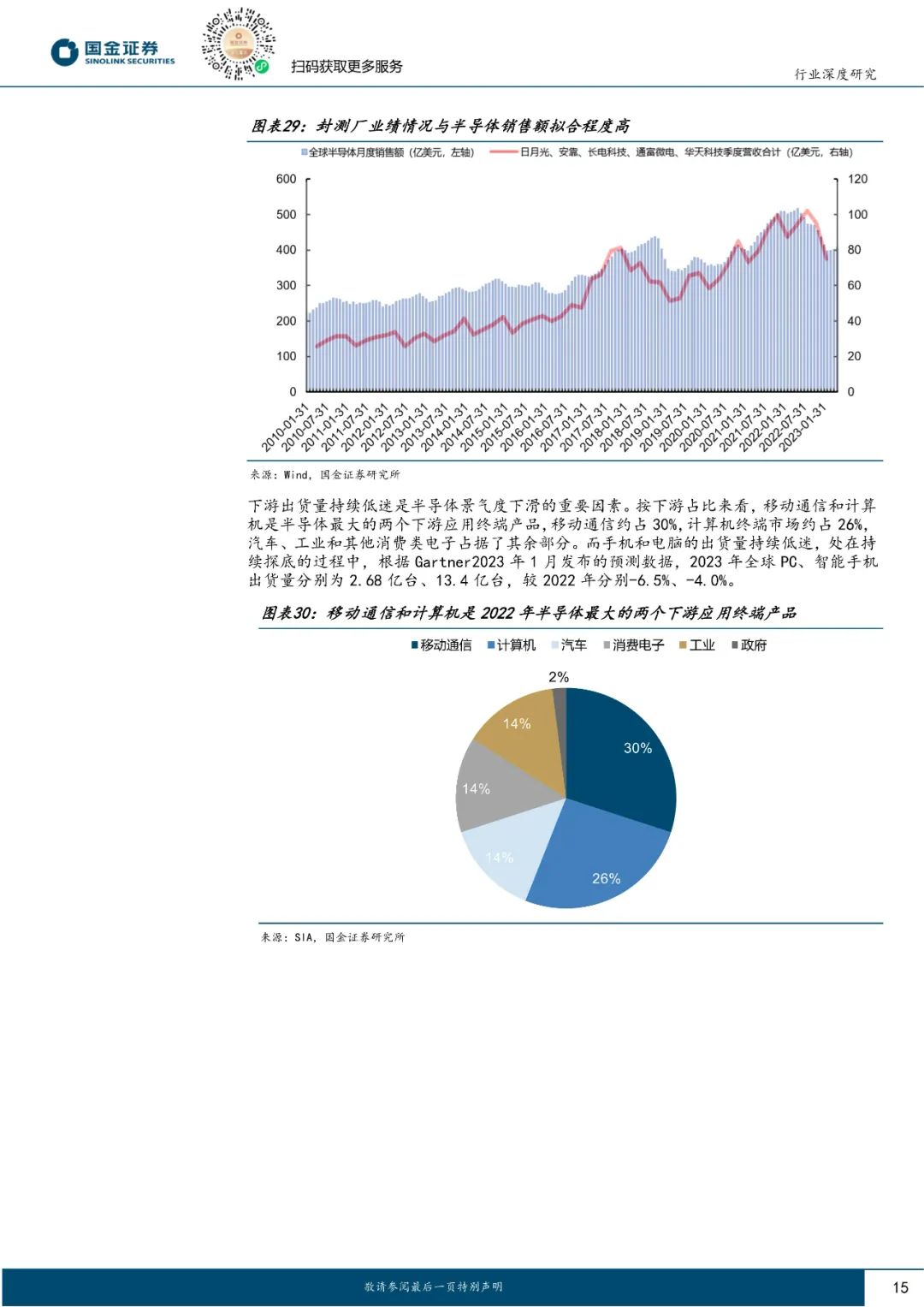

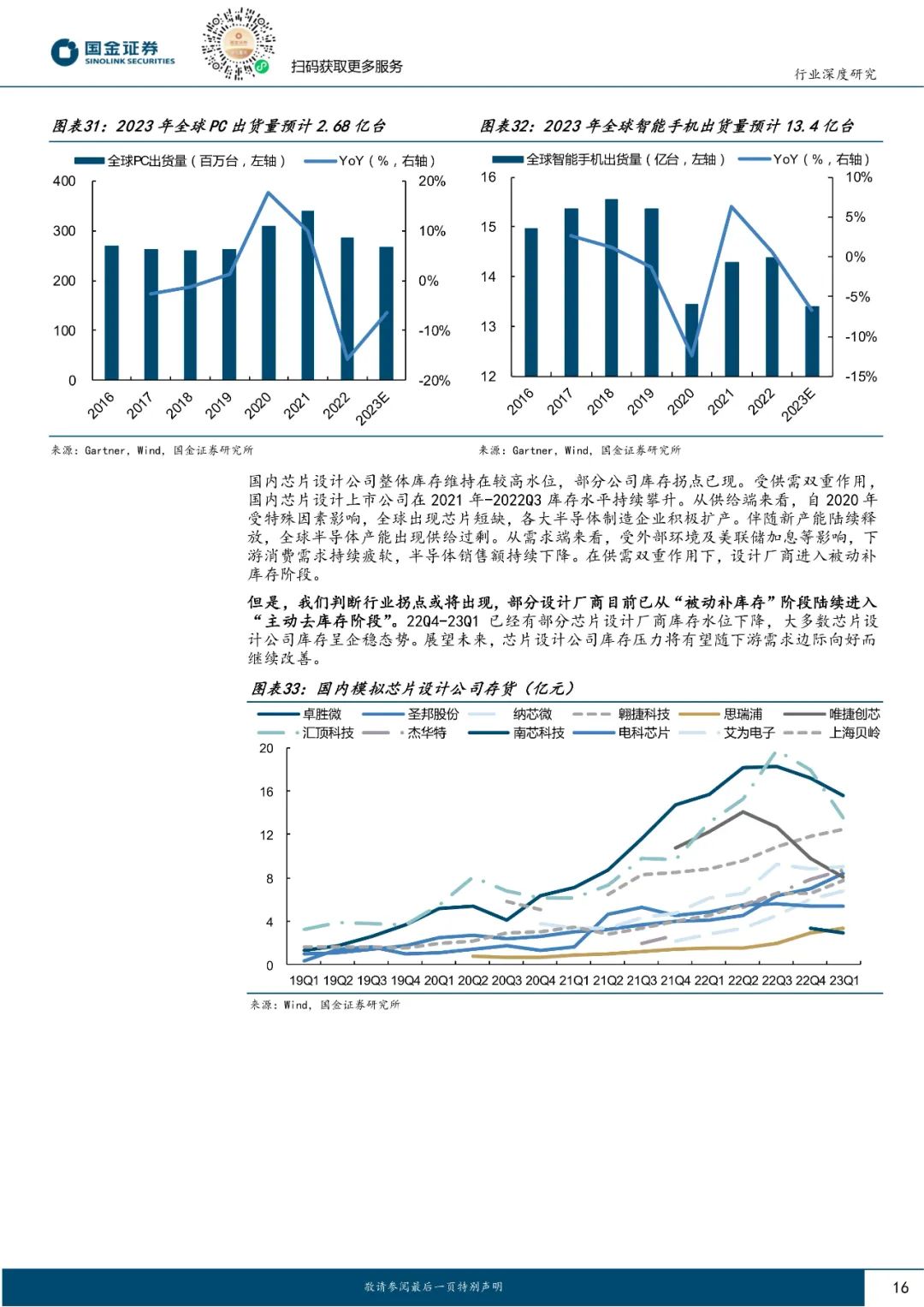

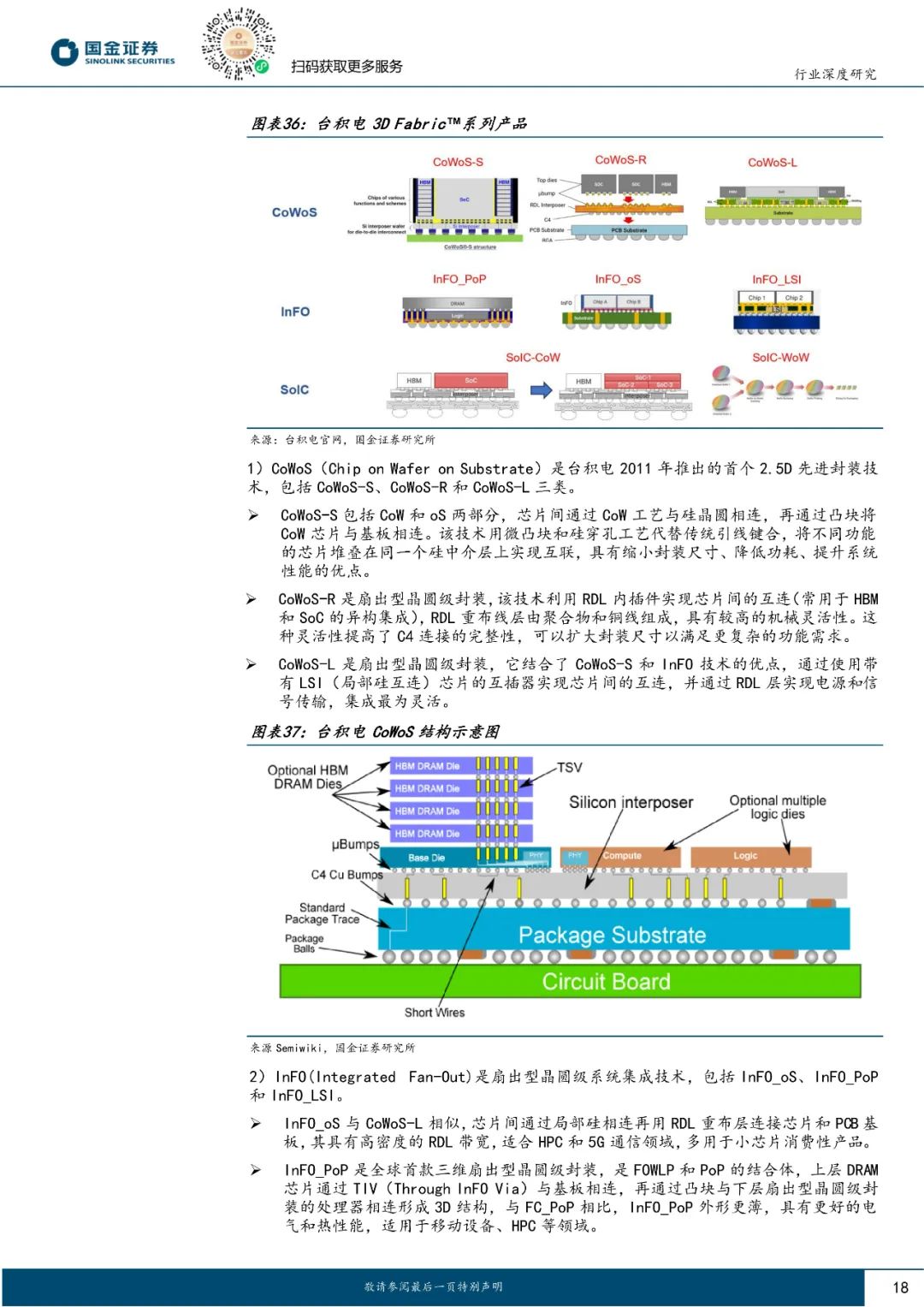

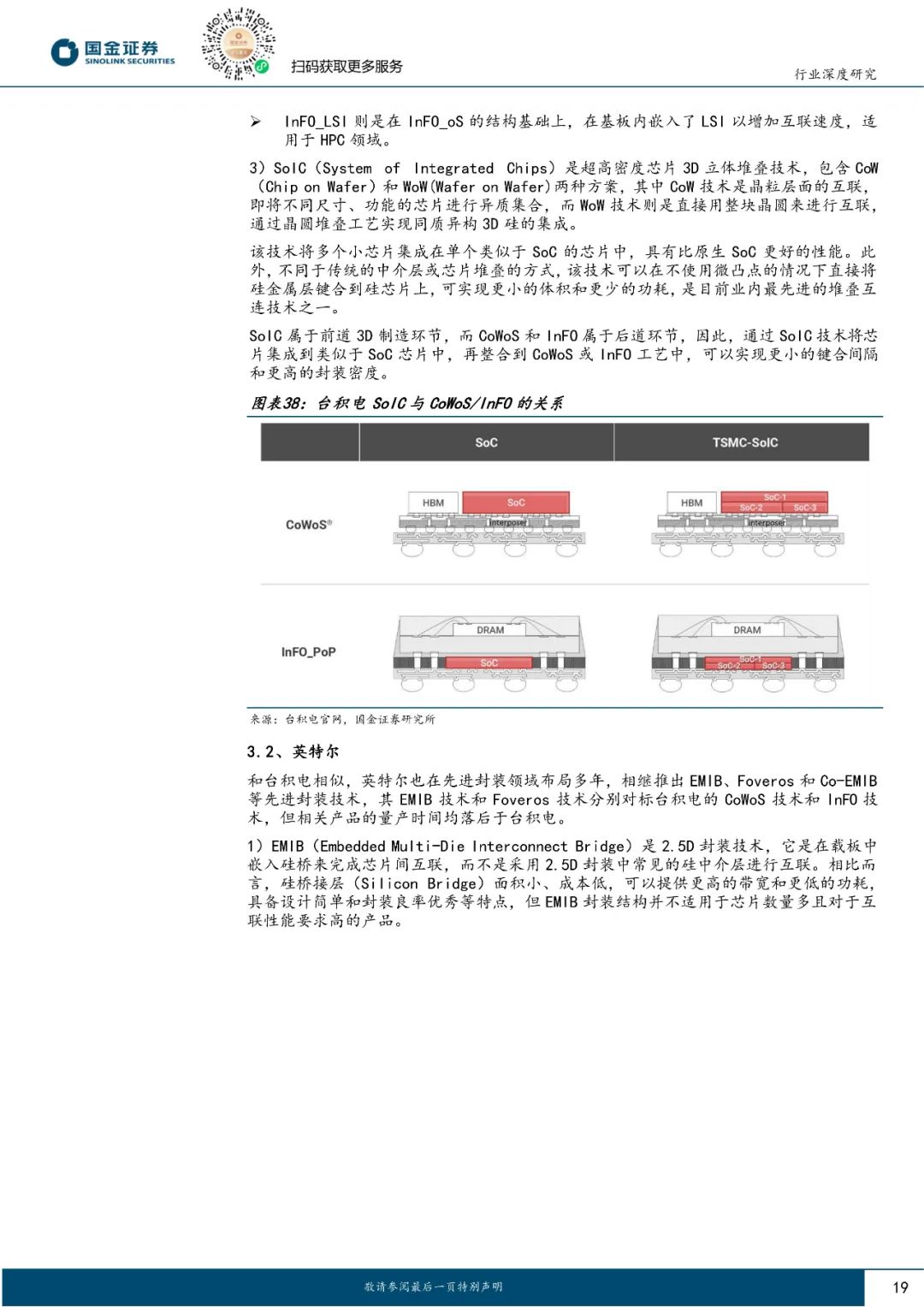

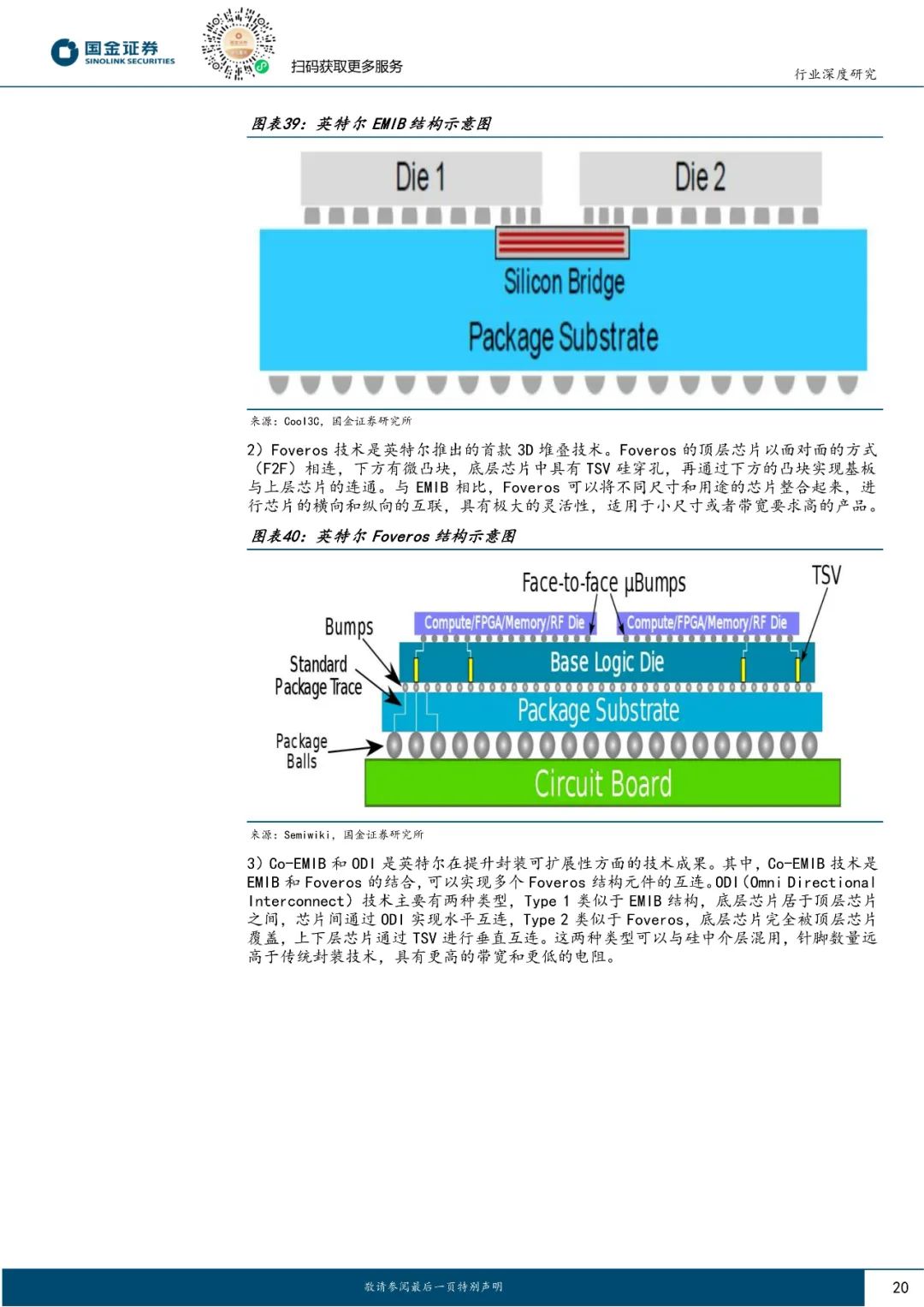

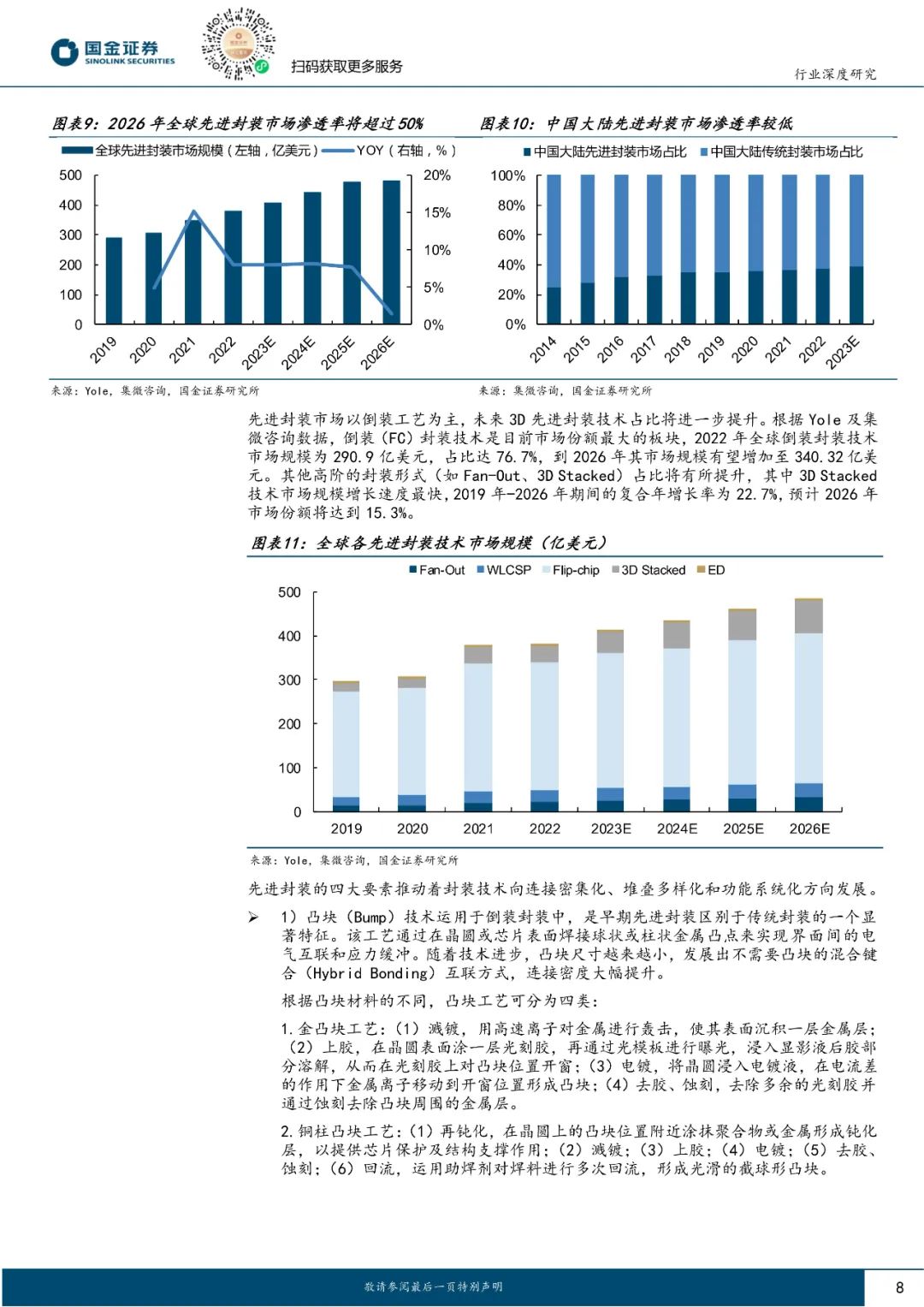

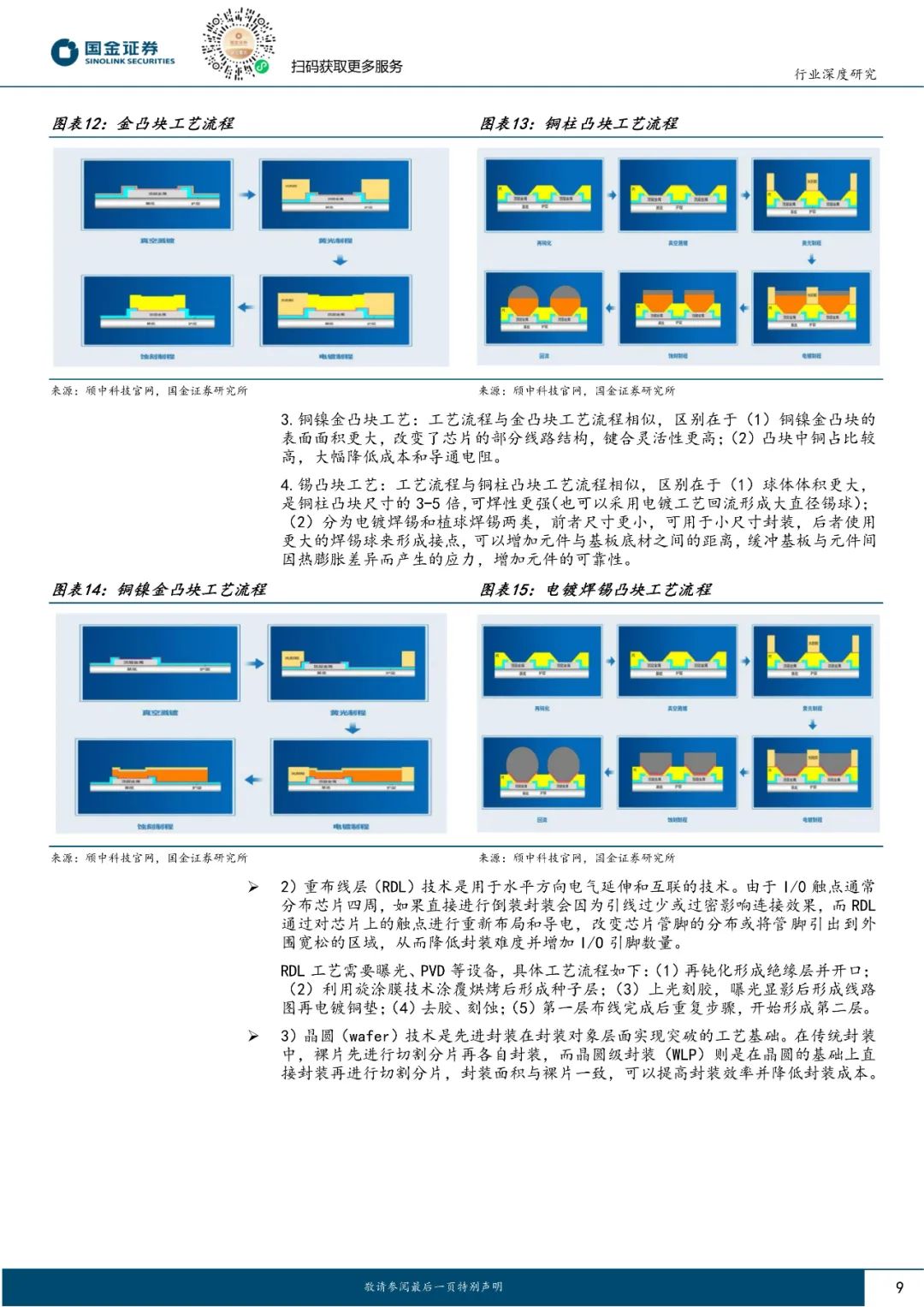

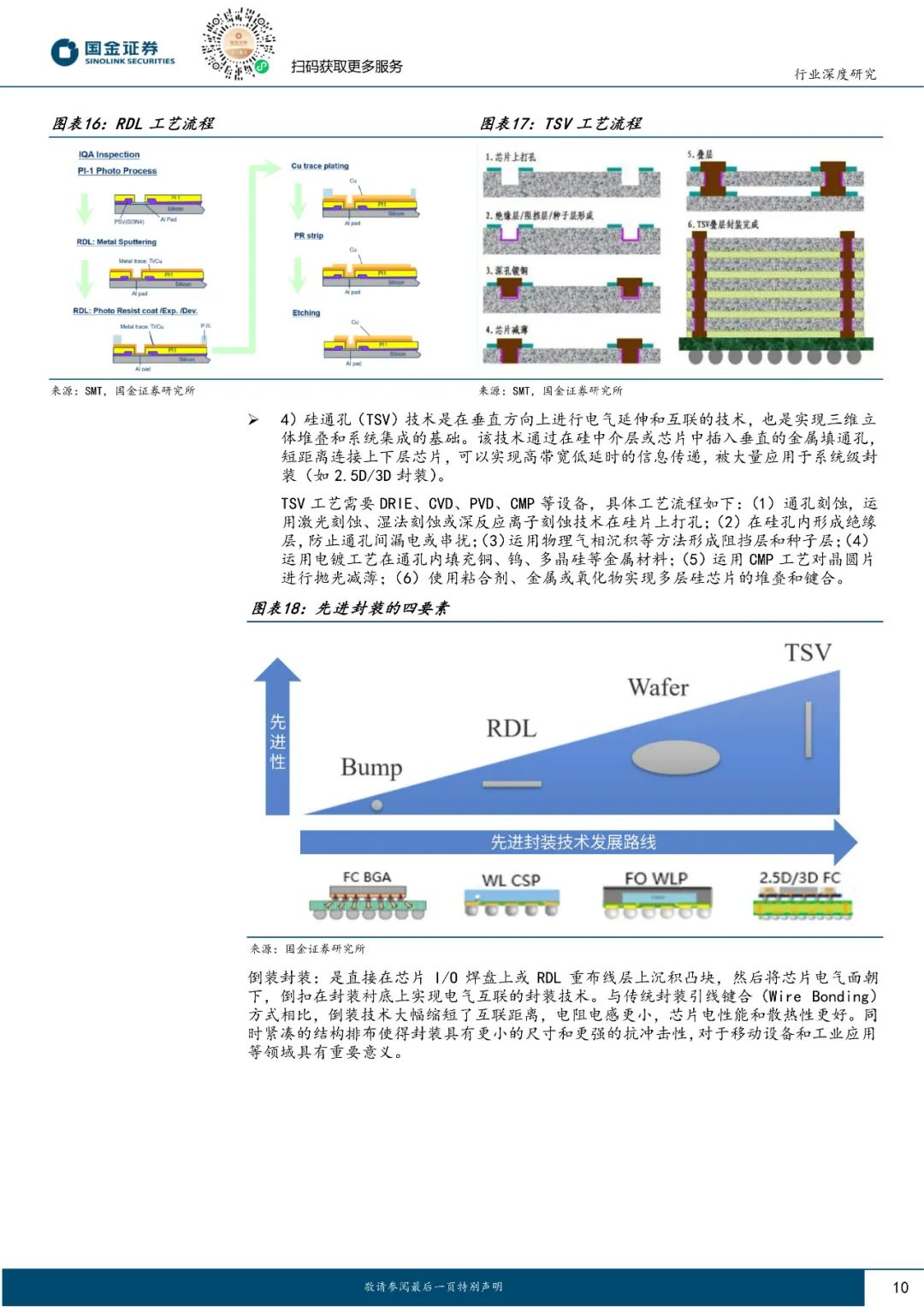

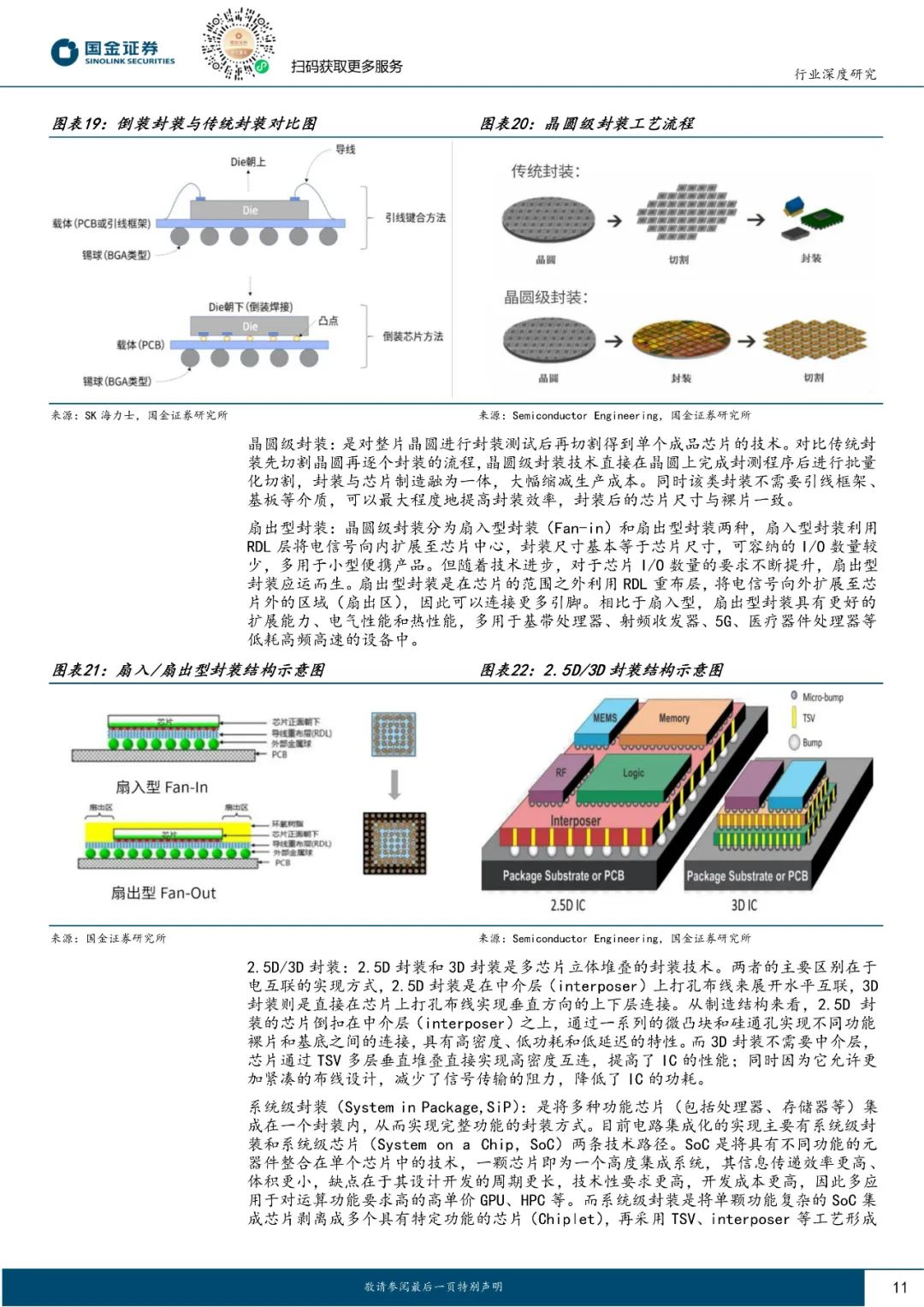

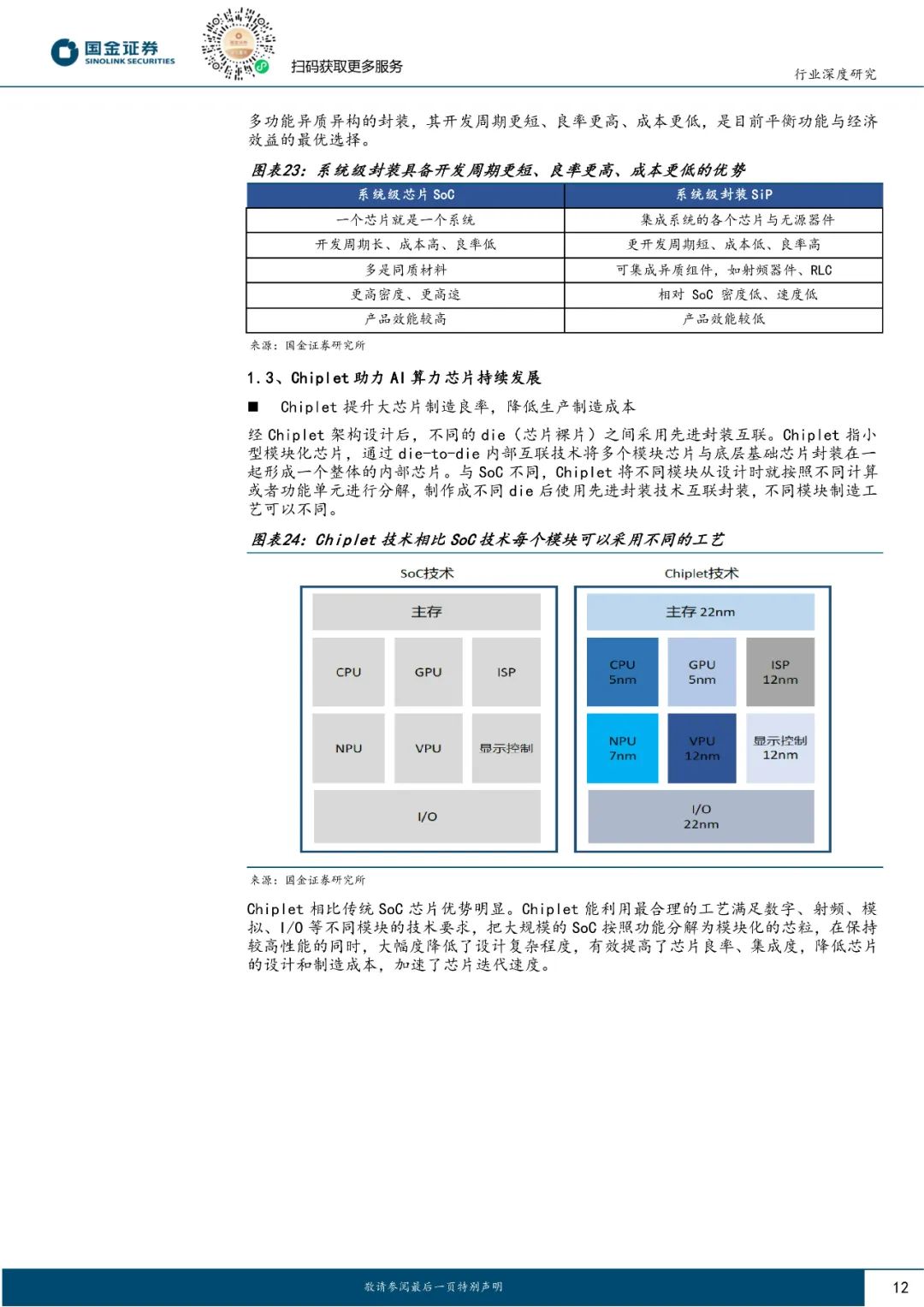

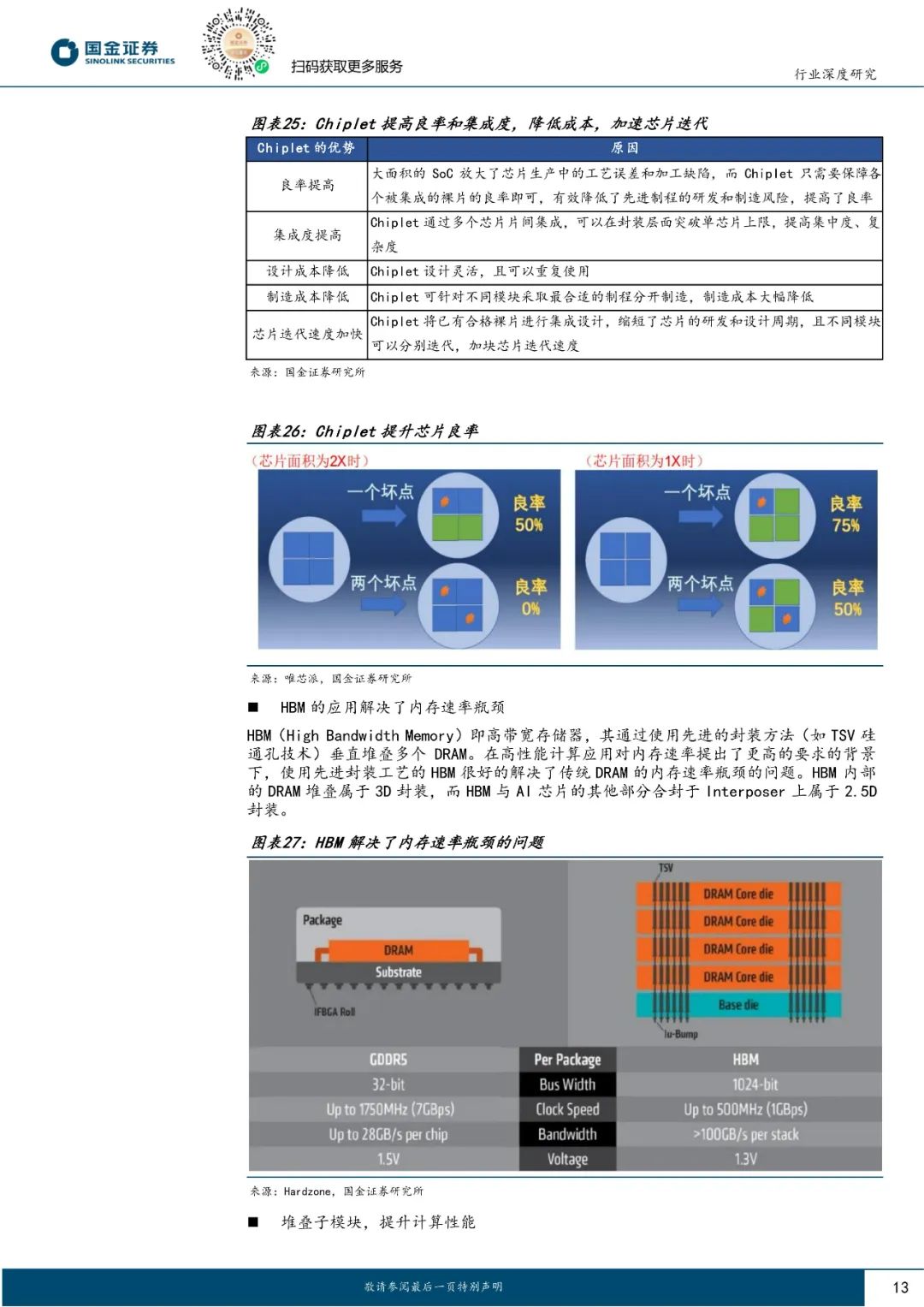

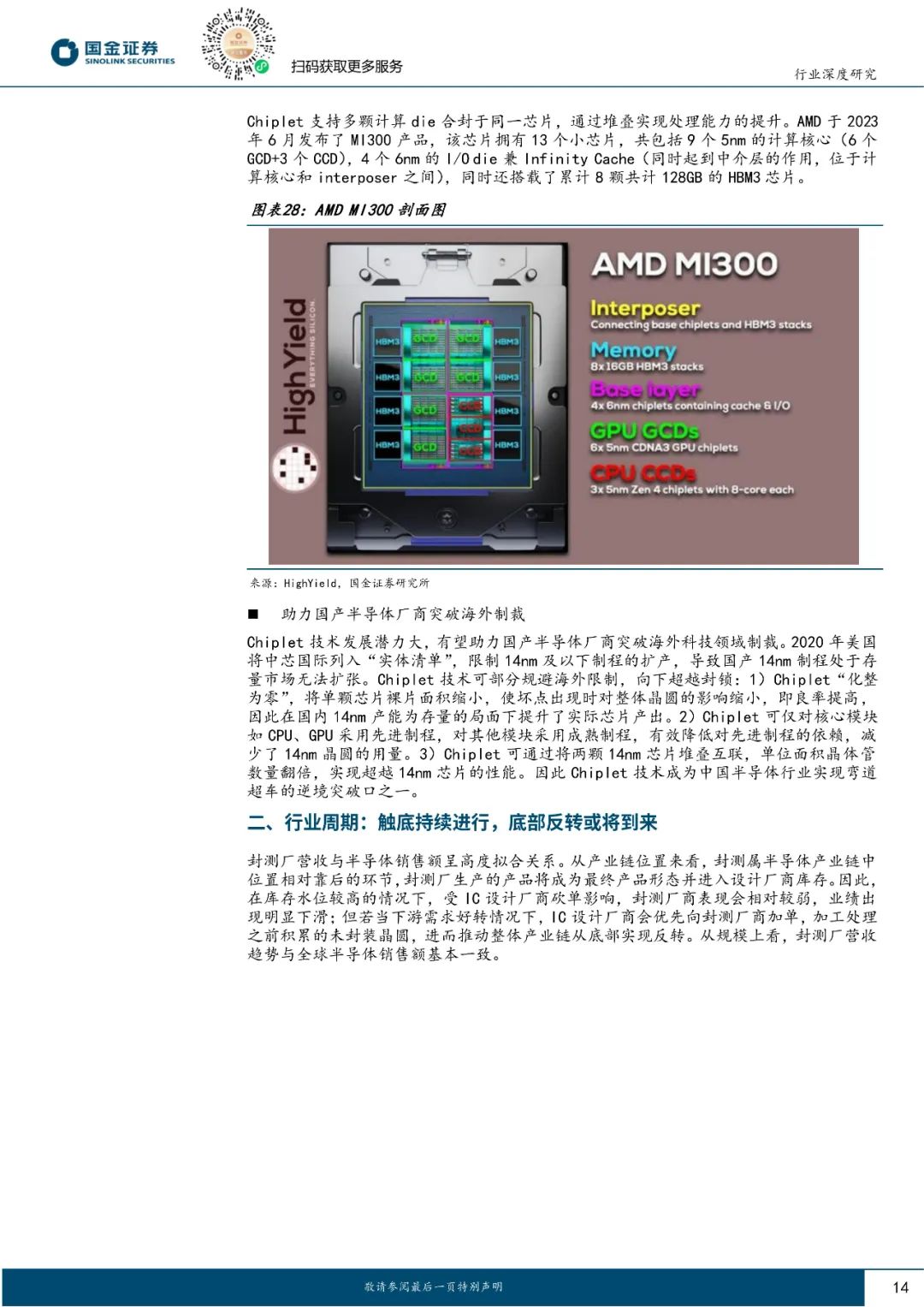

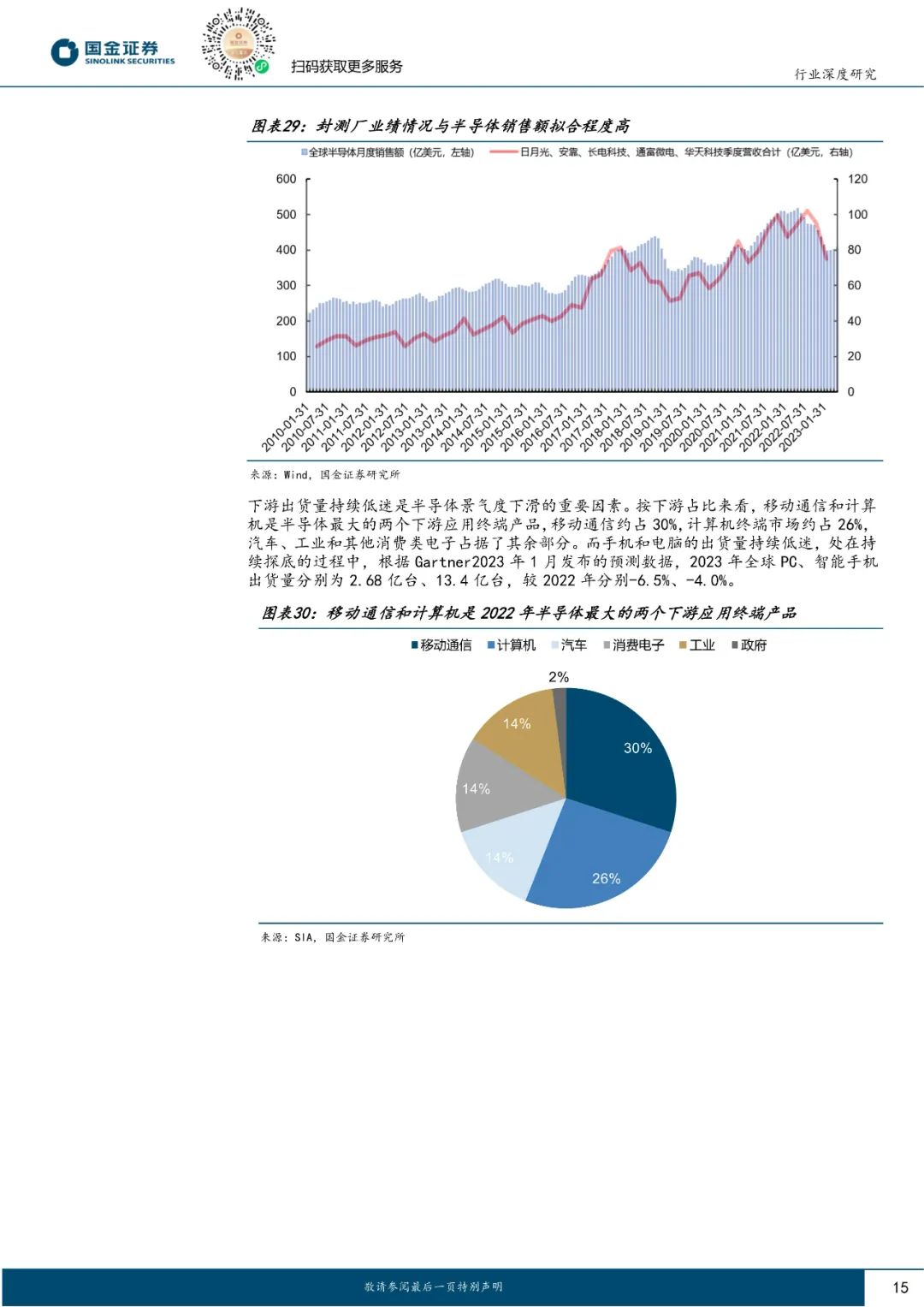

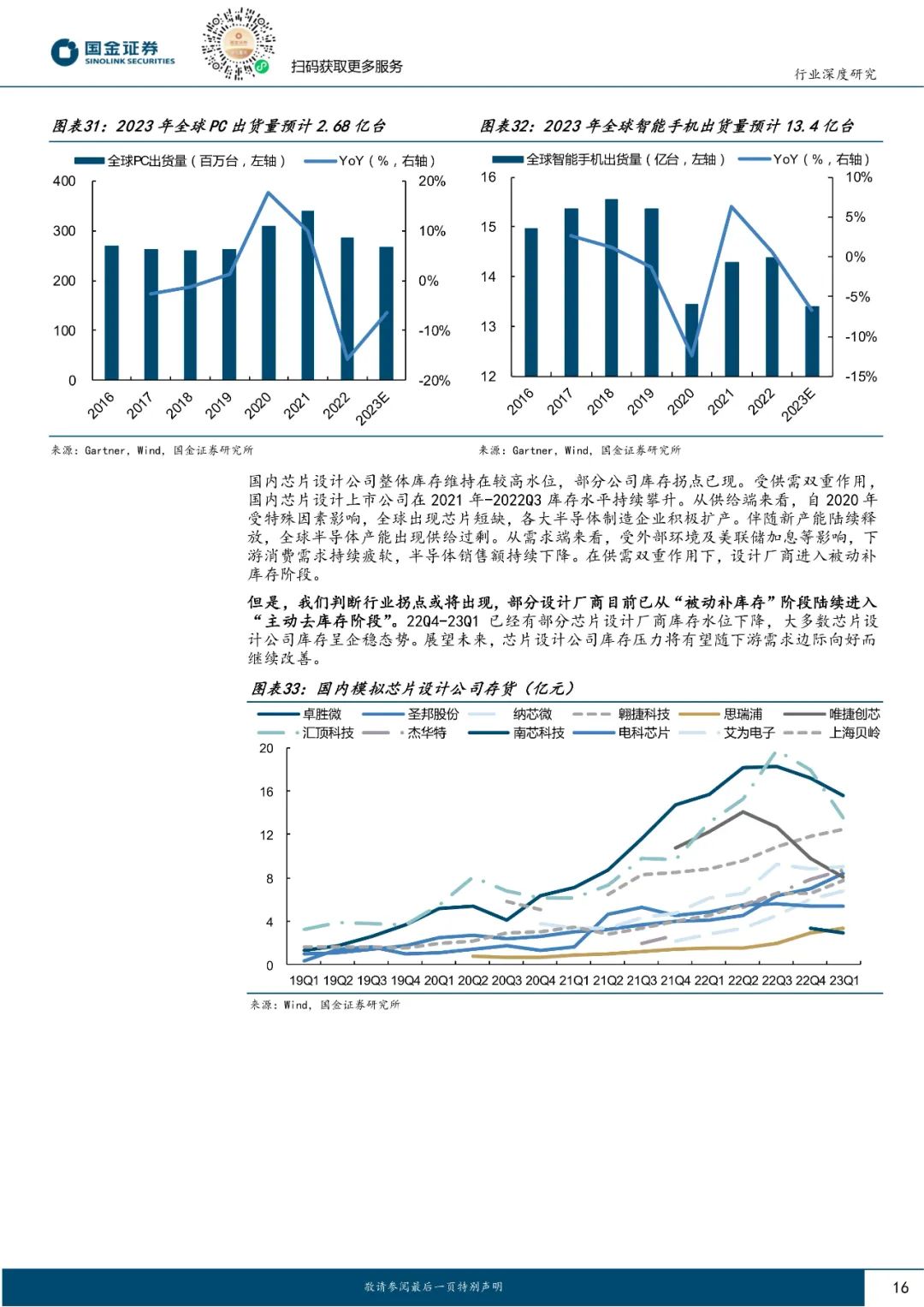

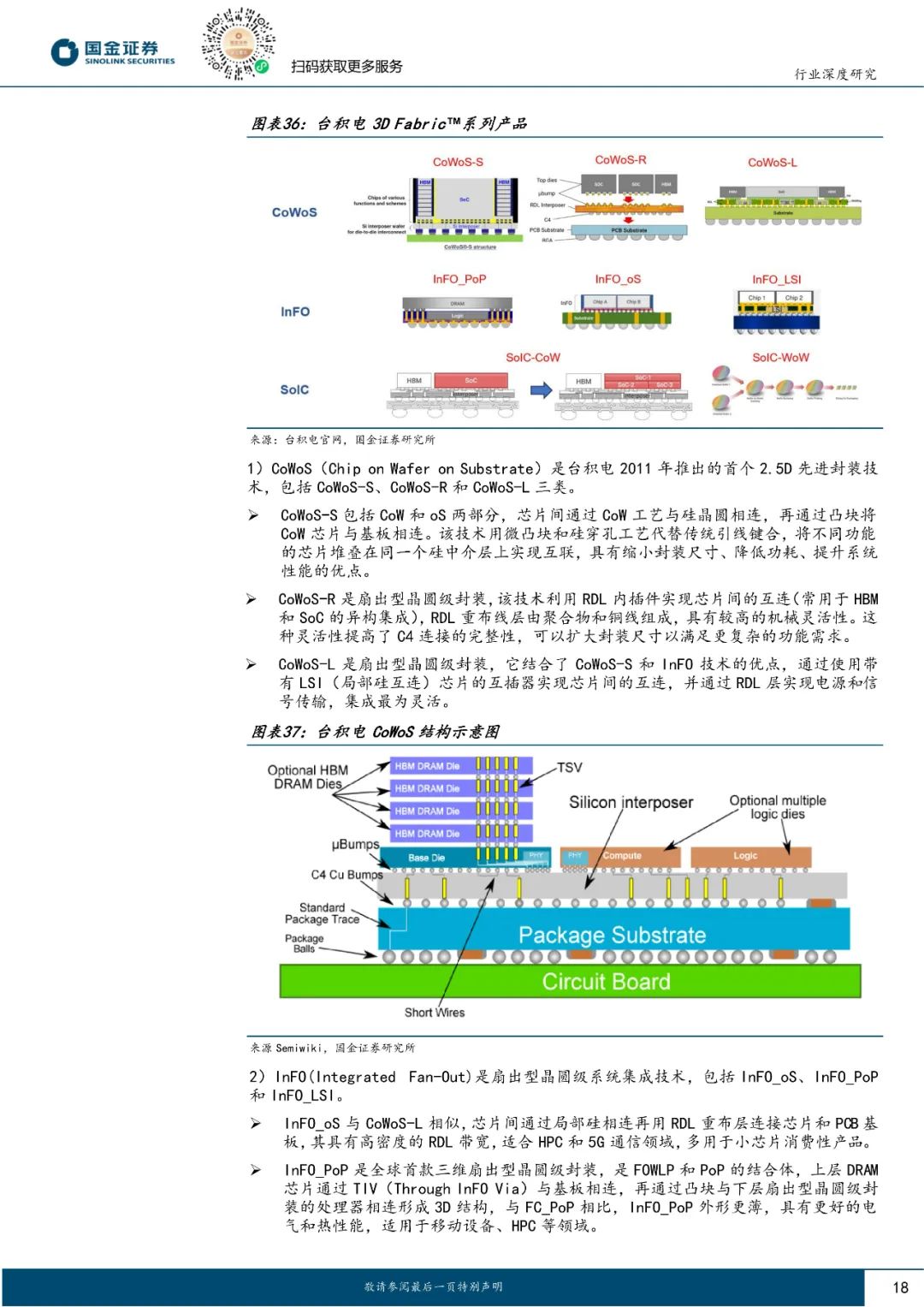

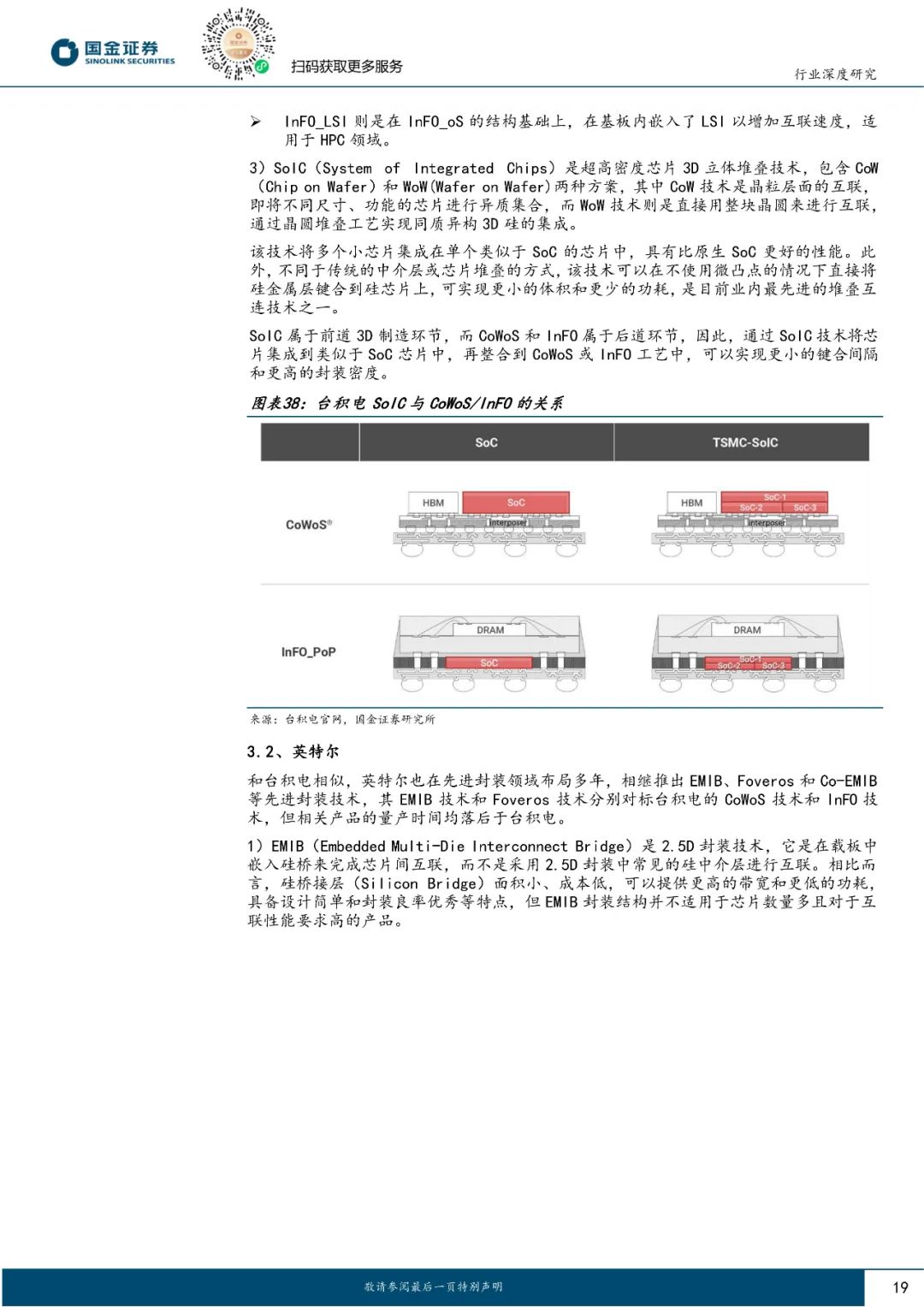

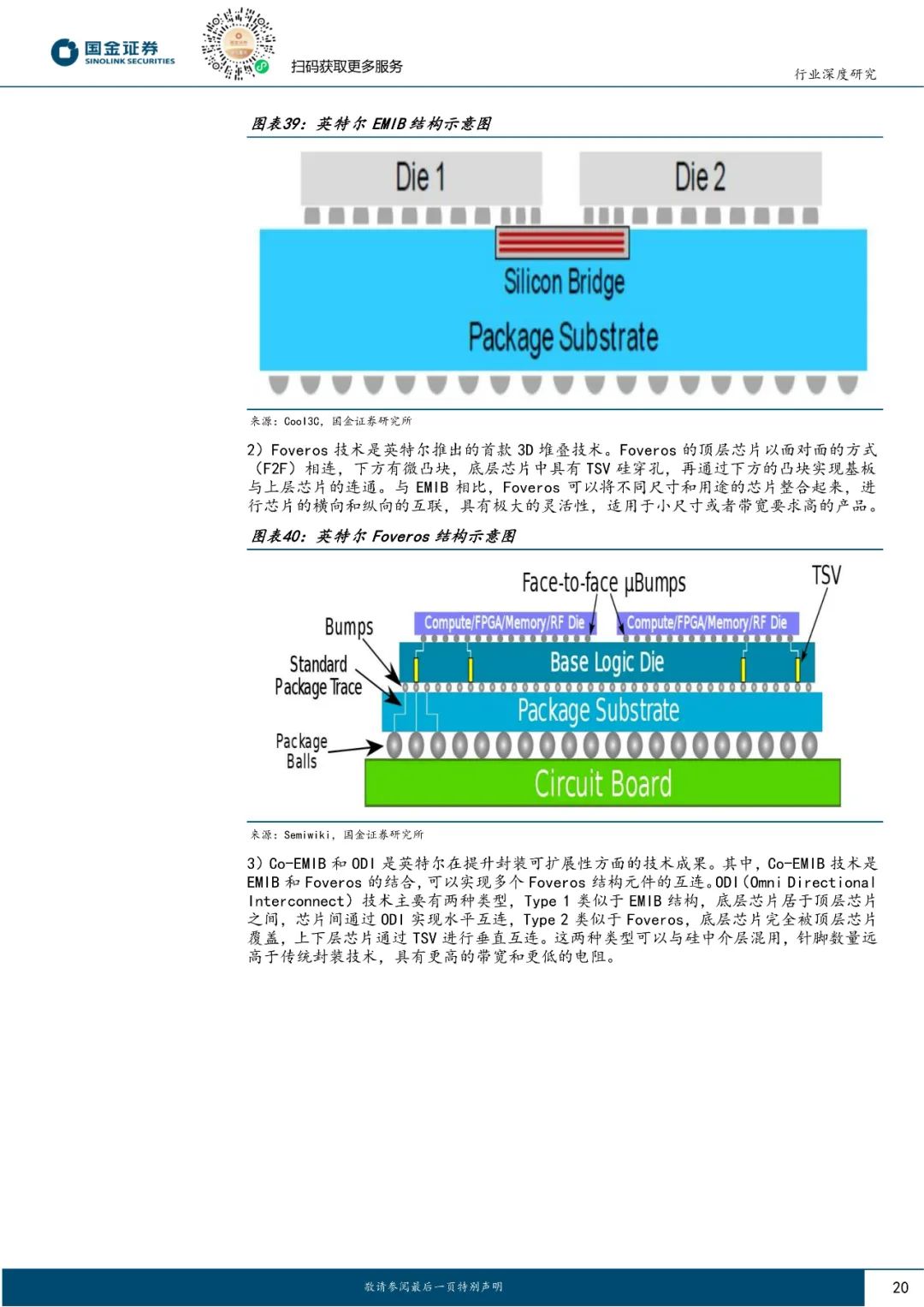

先进封装应用广泛,是实现 Chiplet 设计的基础。在 Chiplet 设计方案中,不同的 die(芯片裸片)之间采用先进封装互联。目前,先进封装向连接密集化、堆叠多样化和功能系统化方向发展主要依赖四大要素:凸块(Bump)、重布线层(RDL)、晶圆(wafer)以及硅通孔(TSV)技术。其中,RDL 和 TSV 分别起到横向及纵向电气延伸的作用,Bump 及晶圆级封装主要起到缩小封装尺寸,提升单位体积性能的作用。目前主流的先进封装方案包括倒装封装(FC)、晶圆级封装、扇出型封装(Fan Out)、2.5D/3D 封装以及系统级封装(SiP)。根据 Yole 及集微咨询数据,倒装封装技术是目前市场份额最大的板块,2022年全球倒装封装技术市场规模为290.9亿美元,占比达76.7%。未来 3D 封装有望快速成长,份额有望快速提升。 AI 加速落地,带动先进封装需求快速增长。先进封装在高算力芯片上优势显著:HBM 方案的提出,解决了存储内存速率瓶颈的问题;AMD 的新款算力芯片 MI300 由 13 个小芯片堆叠而成,采用堆叠子模块的方式进一步提升性能;CoWoS 技术在 GPU 芯片的批量应用,解决了互联密度的问题。目前,伴随 AI 相关应用的加速落地,对于算力芯片的需求快速提升,与之配套的先进封装需求快速增长。目前 CoWoS 的发明者台积电计划斥资 900 亿新台币设立生产先进封装的晶圆厂以满足日益饱满的订单,其他海外大厂也在加快布局,以满足日益增长的先进封装需求。我国先进封装快速发展且潜力巨大。我国先进封装市场快速成长,据中国半导体行业协会统计及集微咨询数据,预计 2023 年中国先进封装市场规模预计达 1330 亿元,2020-2023 年 4 年的复合增长率约为 13.8%。但是,目前国内先进封装市场占比仅为 39.0%,与全球先进封装市场占比(48.8%)相比仍有较大差距,尚有较大提升空间。目前,由于制裁不断升级,国内先进制程发展受阻,Chiplet 设计及先进封装制造有希望成为国产替代的突破口,我国先进封装产业有望进入发展快车道。 周期复盘:行业触底持续进行,底部反转或将到来。封测厂营收与半导体销售额呈高度拟合关系,受下游需求侧不景气的影响,封测厂商稼动率底部承压。但是,我们判断拐点或将出现,部分设计厂商目前已从“被动补库存”阶段陆续进入“主动去库存阶段”,封测厂商稼动率已有回暖迹象。展望未来,芯片设计公司库存压力将有望随下游需求边际向好而继续改善,待需求底部反转后,由于封测公司在产业链中的位置相对靠后,封测公司有望率先收益。此外,由于封测行业重资产属性强,进入上行周期后,有望表现更高的利润弹性。报告来源《先进封装价值量提升叠加需求回暖,封测产业链机遇将至》,国金证券,作者樊志远、赵晋

先进封装论坛 2023年9月24-26日 中国·深圳AEMIC先进封装论坛针对全球先进封装产业频现“软肋”的核心技术与产业问题,论坛从先进封装工艺、异构集成的前沿技术、关键材料与设备、可靠性与产品失效分析、最新市场应用、以及产业发展的新机遇与挑战等问题进行攻关,着力突破先进封装产业发展难题,实现原材料-材料-工艺-器件的原始创新性与产业平衡发展。

扫码加小助手微信(夏雪),加入技术交流群

以下为报告节选内容

免责声明 | 部分素材源自网络,版权归原作者所有。如涉侵权,请联系我们处理