本系列为线下学员学习笔记整理分享,如有想要报名参加线下培训,可以点击以下超链接文章了解,购买开发板可以到叁芯智能科技企业淘宝店下单。

FPGA就业班,2023.09.12开班,系统性学习FPGA,高薪就业,线上线下同步!

本篇文章描述状态机的一段式、二段式、三段式区别

一、状态机

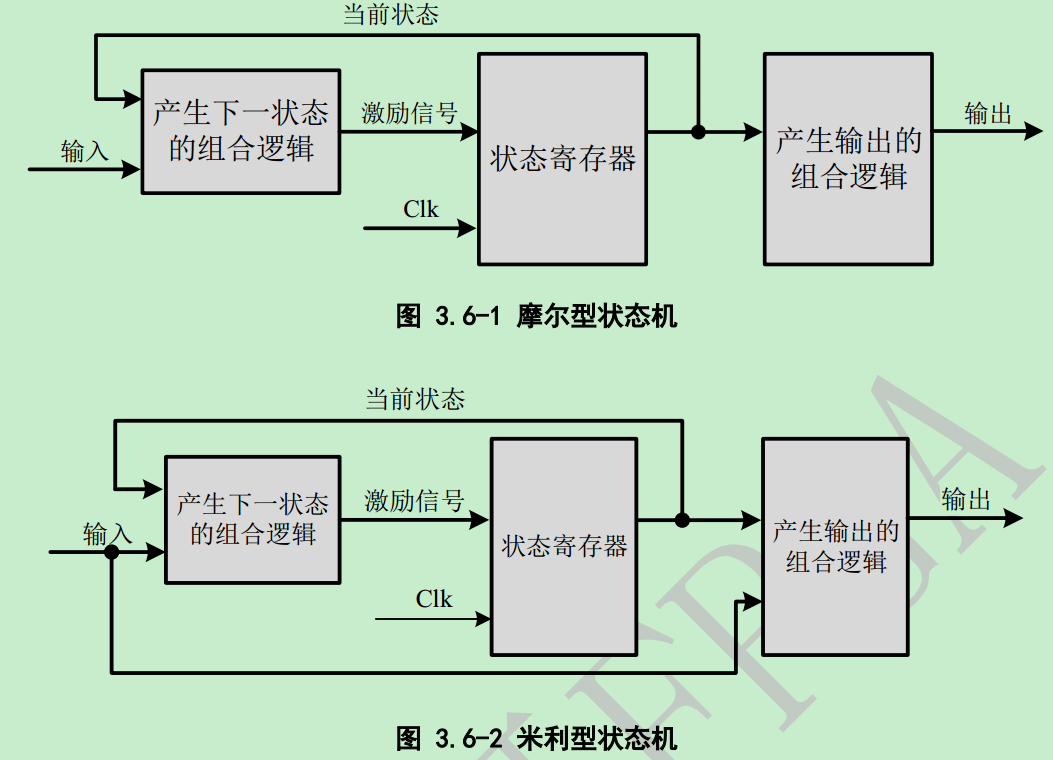

再次给出状态机的示意图:

1.1、摩尔型,输出只与状态寄存器的输出状态有关

1.2、米粒型,输出不仅与状态寄存器的输出状态有关,还与组合逻辑的输入有关

二、一段式、二段式、三段式区别

根据状态机的结构,状态机描述方式 可分为:一段式、二段式、三段式

1.1、一段式

整个状态机写到一个 always 模块里面。在该模块中既描述状态转移,又描述状态的输入和输出 。

1.2、二段式

用两个 always 模块来描述状态机。

1.2.1、其中一个 always 模块采用同步时序描述状态转移;

1.2.2、另一个 always模块采用组合逻辑判断状态转移条件,描述状态转移规律及其输出 ,注意组合逻辑输出要用阻塞赋值。

1.3、三段式

在两个 always 模块描述方法基础上,使用三个 always 模块。

1.3.1、 一个 always 模块采用同步时序描述状态转移;

1.3.2、一个 always 采用组合逻辑判断状态转移条件,描述状态转移规律,注意组合逻辑输出要用阻塞赋值;

1.3.3、另一个 always 模块描述状态输出(可以用组合电路输出,也可以时序电路输出),注意组合逻辑输出要用阻塞赋值。

1.4、综合

可以看出两段式有限状态机与一段式有限状态机的区别是将时序部分(状态转移)和组合部分(判断状态转移条件和产生输出)分开,写为两个 always语句,即为两段式有限状态机。将组合部分中的判断状态转移条件和产生输出再分开写,则为三段式有限状态机。

三、自动售货机、一段式

module auto_sell(input clk,input rst_n,input coin_one,input coin_half,output reg water,output reg coin_back);parameter ZERO = 3'b000;parameter HALF = 3'b001;parameter ONE = 3'b010;parameter ONE_HALF = 3'b011;parameter TWO = 3'b100;//一段式状态机reg [2:0] status;clk,negedge rst_n)beginif(!rst_n)beginstatus <= ZERO;water <= 0;coin_back <= 0;endelsecase(status)ZERO :beginwater <= 0;coin_back <= 0;if(coin_half)status <= HALF;else if(coin_one)status <= ONE;elsestatus <= status;endHALF :beginwater <= 0;coin_back <= 0;if(coin_half)status <= ONE;else if(coin_one)status <= ONE_HALF;elsestatus <= status;endONE :beginwater <= 0;coin_back <= 0;if(coin_half)status <= ONE_HALF;else if(coin_one)status <= TWO;elsestatus <= status;endONE_HALF :beginif(coin_half)beginstatus <= TWO;water <= 1'b0;coin_back <= 1'b0;endelse if(coin_one)beginstatus <= ZERO;water <= 1'b1;coin_back <= 1'b0;endelsebeginstatus <= status;water <= 1'b0;coin_back <= 1'b0;endendTWO :beginif(coin_half)beginstatus <= ZERO;water <= 1'b1;coin_back <= 1'b0;endelse if(coin_one)beginstatus <= ZERO;water <= 1'b1;coin_back <= 1'b1;endelsebeginstatus <= status;water <= 1'b0;coin_back <= 1'b0;endenddefault:beginstatus <= ZERO;water <= 1'b0;coin_back <= 1'b0;endendcaseendendmodule

四、自动售货机、二段式

1.1、二段式,写法一

module auto_sell(input clk,input rst_n,input coin_one,input coin_half,output reg water,output reg coin_back);parameter ZERO = 3'b000;parameter HALF = 3'b001;parameter ONE = 3'b010;parameter ONE_HALF = 3'b011;parameter TWO = 3'b100;1 ok--------------------------//二段式状态机reg [2:0] c_status;reg [2:0] n_status;//状态转移clk,negedge rst_n)beginif(!rst_n)c_status <= ZERO;elsec_status <= n_status;end//描述状态转移规律以及输出clk,negedge rst_n)beginif(!rst_n)beginn_status <= ZERO;water <= 1'b0;coin_back <= 1'b0;endelsecase(c_status)ZERO :beginwater <= 1'b0;coin_back <= 1'b0;if(coin_half)n_status <= HALF;else if(coin_one)n_status <= ONE;elsen_status <= ZERO;endHALF :beginwater <= 1'b0;coin_back <= 1'b0;if(coin_half)n_status <= ONE;else if(coin_one)n_status <= ONE_HALF;elsen_status <= HALF;endONE :beginwater <= 1'b0;coin_back <= 1'b0;if(coin_half)n_status <= ONE_HALF;else if(coin_one)n_status <= TWO;elsen_status <= ONE;endONE_HALF :beginwater <= 1'b0;coin_back <= 1'b0;if(coin_half)n_status <= TWO;else if(coin_one)beginn_status <= ZERO;water <= 1'b1;coin_back <= 1'b0;endelsen_status <= ONE_HALF;endTWO :beginwater <= 1'b0;coin_back <= 1'b0;if(coin_half)beginn_status <= ZERO;water <= 1'b1;coin_back <= 1'b0;endelse if(coin_one)beginn_status <= ZERO;water <= 1'b1;coin_back <= 1'b1;endelsen_status <= TWO;enddefault:n_status <= ZERO;endcaseendendmodule

1.2、二段式,写法二

module auto_sell(input clk,input rst_n,input coin_one,input coin_half,output reg water,output reg coin_back);parameter ZERO = 3'b000;parameter HALF = 3'b001;parameter ONE = 3'b010;parameter ONE_HALF = 3'b011;parameter TWO = 3'b100;2 ok--------------------------------------//二段式状态机reg [2:0] status;//状态转移clk,negedge rst_n)beginif(!rst_n)status <= ZERO;elsebegincase(status)ZERO :beginif(coin_half)status <= HALF;else if(coin_one)status <= ONE;elsestatus <= ZERO;endHALF :beginif(coin_half)status <= ONE;else if(coin_one)status <= ONE_HALF;elsestatus <= HALF;endONE :beginif(coin_half)status <= ONE_HALF;else if(coin_one)status <= TWO;elsestatus <= ONE;endONE_HALF :beginif(coin_half)status <= TWO;else if(coin_one)beginstatus <= ZERO;endelsestatus <= ONE_HALF;endTWO :beginif(coin_half)beginstatus <= ZERO;endelse if(coin_one)beginstatus <= ZERO;endelsestatus <= TWO;enddefault:status <= ZERO;endcaseendend时序逻辑clk,negedge rst_n)beginif(!rst_n)beginwater <= 1'b1;coin_back <= 1'b0;endelsecase(status)ONE_HALF:beginif(coin_one)beginwater <= 1'b1;coin_back <= 1'b0;endelsebeginwater <= 1'b0;coin_back <= 1'b0;endendTWO:beginif(coin_half)beginwater <= 1'b1;coin_back <= 1'b0;endelse if(coin_one)beginwater <= 1'b1;coin_back <= 1'b1;endelsebeginwater <= 1'b0;coin_back <= 1'b0;endenddefault:beginwater <= 1'b0;coin_back <= 1'b0;endendcaseendendmodule

五、自动售货机、三段式

module auto_sell(input clk,input rst_n,input coin_one,input coin_half,output reg water,output reg coin_back);parameter ZERO = 3'b000;parameter HALF = 3'b001;parameter ONE = 3'b010;parameter ONE_HALF = 3'b011;parameter TWO = 3'b100;//三段式状态机reg [2:0] c_status;reg [2:0] n_status;//状态转移clk,negedge rst_n)beginif(!rst_n)c_status <= ZERO;elsec_status <= n_status;end//状态转移规律及状态输出,组合逻辑输出只与输入有关= n_status,电路会出错;always@(*)begincase(c_status)ZERO :beginif(coin_half)n_status = HALF;else if(coin_one)n_status = ONE;elsen_status = ZERO;endHALF :beginif(coin_half)n_status = ONE;else if(coin_one)n_status = ONE_HALF;elsen_status = HALF;endONE :beginif(coin_half)n_status = ONE_HALF;else if(coin_one)n_status = TWO;elsen_status = ONE;endONE_HALF :beginif(coin_half)n_status = TWO;else if(coin_one)n_status = ZERO;elsen_status = ONE_HALF;endTWO :beginif(coin_half)n_status = ZERO;else if(coin_one)n_status = ZERO;elsen_status = TWO;enddefault:n_status = ZERO;endcaseendclk,negedge rst_n)beginif(!rst_n)beginwater = 1'b1;coin_back = 1'b0;endelsecase(c_status)ONE_HALF:beginif(coin_one)beginwater = 1'b1;coin_back = 1'b0;endelsebeginwater = 1'b0;coin_back = 1'b0;endendTWO:beginif(coin_half)beginwater = 1'b1;coin_back = 1'b0;endelse if(coin_one)beginwater = 1'b1;coin_back = 1'b1;endelsebeginwater = 1'b0;coin_back = 1'b0;endenddefault:beginwater = 1'b0;coin_back = 1'b0;endendcaseendendmodule

六、仿真脚本

1ns/1psmodule auto_sell_tb;reg clk;reg rst_n;reg coin_one;reg coin_half;wire water;wire coin_back;initial beginclk = 0;rst_n = 0;coin_one = 0;coin_half = 0;#20;rst_n = 1;//延时200us#10000//投2.5元coin_half = 1;#20;coin_half = 0;#20;coin_one = 1;#20;coin_one = 0;#20;coin_half = 1;#20;coin_half = 0;#20;coin_half = 1;#20;coin_half = 0;#20;//延时200us#10000//投3元coin_half = 1;#20;coin_half = 0;#20;coin_one = 1;#20;coin_one = 0;#20;coin_half = 1;#20;coin_half = 0;#20;coin_one = 1;#20;coin_one = 0;#20;//延时200us#10000$stop;endauto_sell auto_sell_inst((clk),(rst_n),(coin_one),(coin_half),(water),(coin_back));always #10 clk = ~clk;endmodule

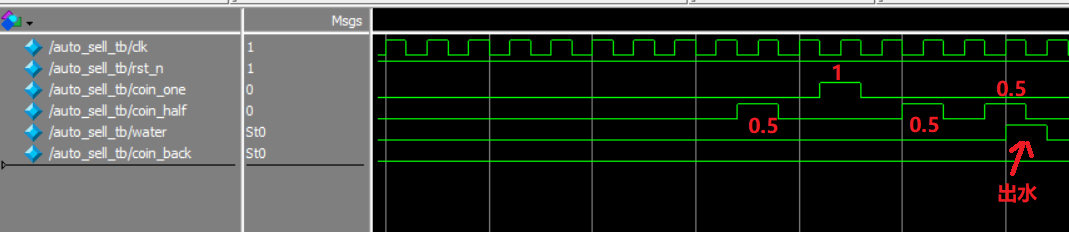

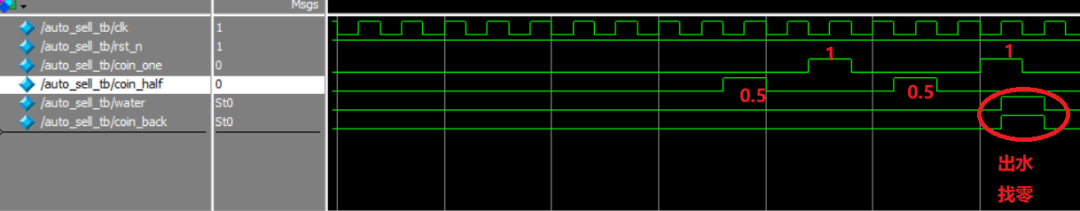

七、仿真结果

- -THE END- -

往期精选

FPGA技术江湖广发江湖帖

无广告纯净模式,给技术交流一片净土,从初学小白到行业精英业界大佬等,从军工领域到民用企业等,从通信、图像处理到人工智能等各个方向应有尽有,QQ微信双选,FPGA技术江湖打造最纯净最专业的技术交流学习平台。

FPGA技术江湖微信交流群

加群主微信,备注姓名+学校/公司+专业/岗位进群

FPGA技术江湖QQ交流群

备注姓名+学校/公司+专业/岗位进群