使用高级综合HLS,开发 2D 中值滤波器算法 (HLS) 。

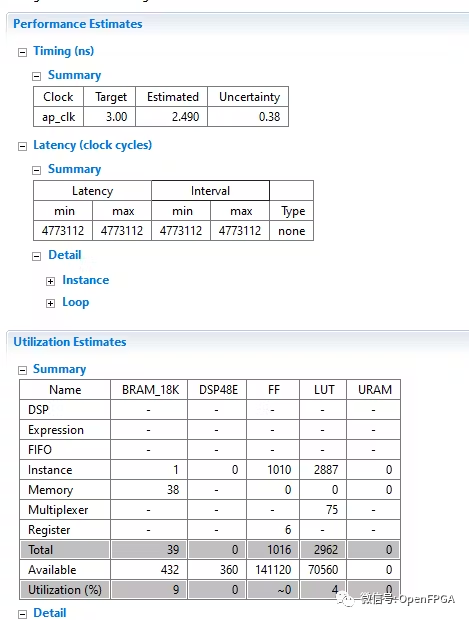

该项目包含使用高级综合 (HLS) 的 2D 中值滤波器算法的实现。该项目的目标是在不到 3 ms的时间内对测试图像进行去噪,同时消耗不到 25% 的可用 PL 资源。特征如下:

该项目包含以下内容:

该项目已在 Vivado HLS 中设计和测试。要设置并运行项目:

将项目导入 Vivado HLS 后:

请注意:可能需要根据所使用的 FPGA 板调整代码中的 HLS 编译指示以获得最佳性能。

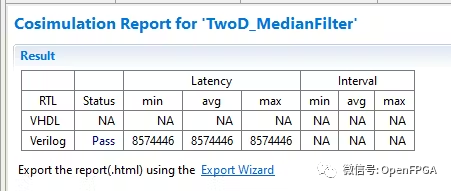

最终设计应用于测试数据时,在不到 12 ms的时间内实现了去噪,总体 PL 资源利用率约为 13%。

❝https://github.com/suisuisi/Xilinx_Library/tree/main/HLS/2D-median-filter-algorithm-HLS

❞

- -THE END- -

往期精选

FPGA技术江湖广发江湖帖

无广告纯净模式,给技术交流一片净土,从初学小白到行业精英业界大佬等,从军工领域到民用企业等,从通信、图像处理到人工智能等各个方向应有尽有,QQ微信双选,FPGA技术江湖打造最纯净最专业的技术交流学习平台。

FPGA技术江湖微信交流群

加群主微信,备注姓名+学校/公司+专业/岗位进群

FPGA技术江湖QQ交流群

备注姓名+学校/公司+专业/岗位进群