今日“芯”分享

多芯片设计中的作用力。

来源 I SemiWiki

编译 I 芯潮IC

图片来源 I Intel

这种趋势是不可否认的。高度集成的单片式芯片已经无法满足下一代系统的需求。这种设计变化的原因很多,你可以在此更好了解多芯片设计中的作用力。

这些变化代表了追求最初由摩尔定律定义的指数缩放的新篇章。因此,人们会自然而然地寻求摩尔定律的发源地英特尔的线索,来看看未来会发生什么。

阅读此文,了解英特尔如何通过封装创新来推动多芯片革命。

01

封装挑战

向多芯片系统的转变带来了巨大的设计和制造方面的挑战。现在,数十亿个晶体管分布在多个芯片上,这些芯片与包含数百万个凸点连接的复杂封装形状因素集成在一起。由此产生的异构集成需要硅、封装和电路板协同设计方法。

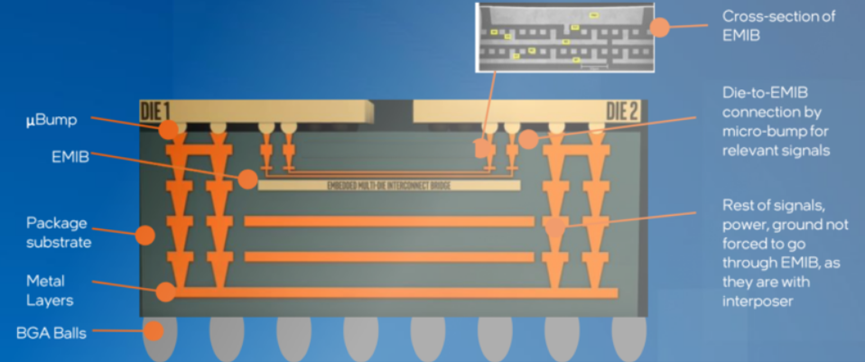

解决这些挑战的传统方法通常涉及硅中介层来实现“2.5D”集成。这种方法的缺点包括额外硅片的成本、设计复杂性的增加以及产量的降低。与此同时,这种方法也限制了可集成的芯片数量和类型。

02

寻找更好的方式 - EMIB

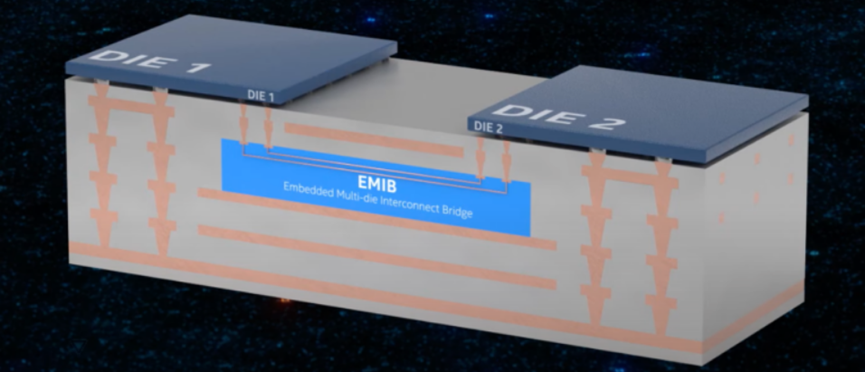

英特尔已经找到了绕过2.5D封装中许多现有限制的方法。在封装中嵌入一个小型硅桥芯片就是正确的答案。嵌入式多芯片互连桥(EMIB)提供了一种经济高效的连接多个芯片的方式。下图概述了这种方法。

03

EMIB概述

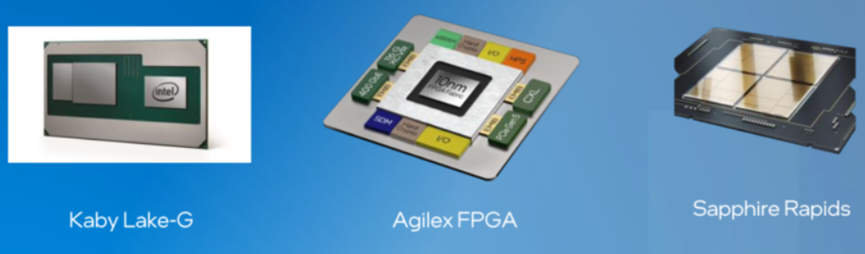

EMIB提供了高度可扩展的功能。现在可以根据实际设计需要进行灵活的设计尺寸、芯片桥尺寸和局部优化,以支持各种异构配置。EMIB已在多个设计中得到验证,如下图所示。

真实的产品示例

04

EMIB 的实施- 生态系统的力量

基于EMIB的封装设计也面临着一系列挑战。这种方法要求具备高引脚、网络数量和设计密度。示例设计可以包含24层、52000个网络和240000个引脚。所有这些都必须在异构设计流程中进行管理,以实现低延迟和最佳能效。

英特尔晶圆制造服务公司(IFS)一再表示,他们致力于通过行业标准和强大的制造生态系统将英特尔技术带给客户。为了履行这一承诺,英特尔通过标准与生态系统协同合作来解决这个问题。数据管理、硅/封装/板协同设计、一致的建模/分析以及通过设计重用优化的成本和性能都得到了全面的封装组件设计工具包(PADK)的支持。

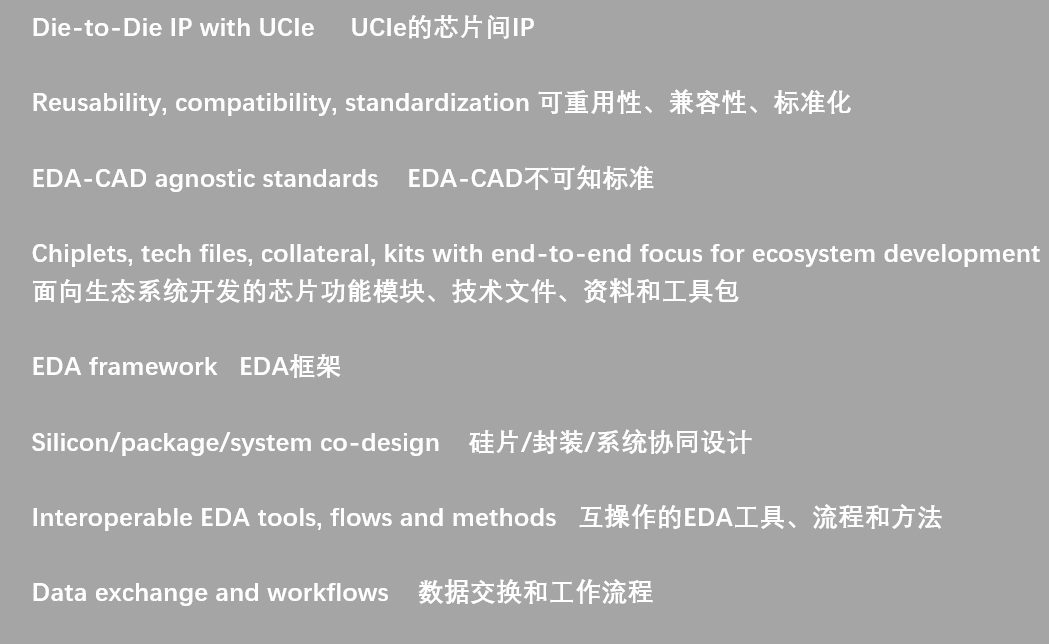

PADK包括:

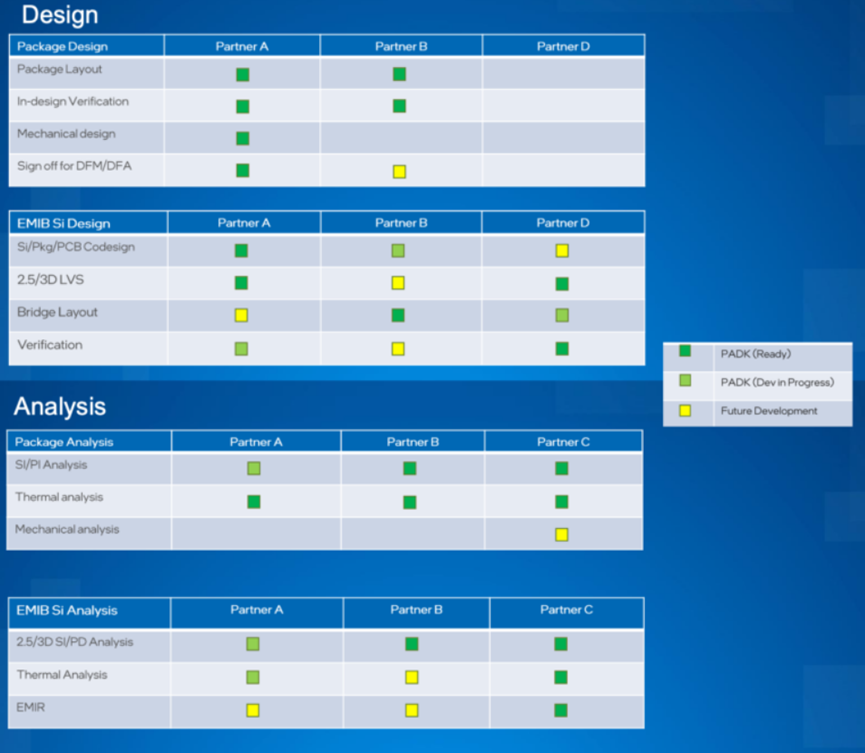

利用这些信息,英特尔与其主要EDA合作伙伴建立了基于EMIB的参考流程。开发中有一个设计和分析流程。下图总结了整个生态系统中每个流程的状态。

Design Flow Status设计流程

英特尔在这一领域还有更多的工作要做。

工作包括:

05

总结

英特尔认为,先进的封装技术、内容密度和封装复杂性需要采用新的方法来提升设计效率。重点是使用设计标准和与供应商无关的工具、流程和方法进行生态系统合作开发。这就是英特尔如何通过封装创新推动多芯片革命的方式,而IFS则将其交付给外部客户。

*免责声明:本文由原作者创作。文章内容系其个人观点,芯潮IC转载仅为分享与讨论,不代表芯潮IC对该观点赞同或支持,如果有任何异议,请联系我们。

芯潮IC Group/

插播一条广告 📢

芯潮IC 愿意为群友搭建沟通和传播的渠道,除提供干货分享外,还可以免费帮忙发布商业需求、异业合作、求职招聘……谢谢各位同行的捧场,也希望我们的文章和服务对你真的有帮助,一起“芯”向未来!

扫码添加芯潮IC编辑「叙白」

入群聊聊行业八卦~

推荐阅读

深度解读丨

算力狂欢,谁是“中国版”英伟达?

深度解读丨

扣住世界半导体的口粮

深度解读丨

光与芯,撑起一座城

深度解读丨

烫火锅、造芯片,成都的双面人生

深度解读丨

车企造芯,赔本生意?

更多精彩,点击关注

芯潮IC

微信号|xinchaoIC