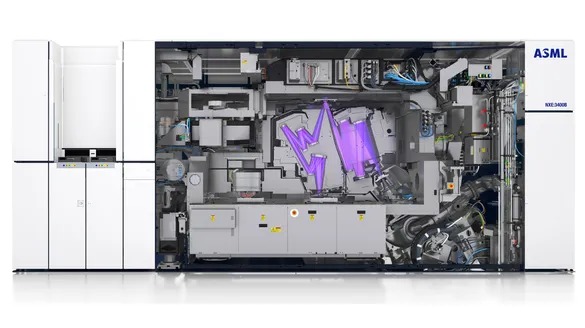

ASML的高数值孔径极紫外光刻机EXE:5000的照片说明了它的巨大规模。来源:ASML

在过去的半个世纪里,我们已经开始把摩尔定律——硅领域中晶体管数量大约每两年翻一番,推动计算向前发展的增益——看作是刚刚发生的事情,就好像它是一个自然的、不可避免的过程,类似于进化或衰老。当然,现实情况大不相同。与摩尔定律保持同步需要花费几乎难以想象的时间、精力和人类智慧——成千上万的人生活在多个大陆,数不清的土地上摆放着地球上最复杂的机器。

也许这些机器中最重要的就是进行极紫外线(EUV)光刻。EUV光刻技术是几十年研发的成果,如今已成为过去两代尖端芯片的驱动技术,在过去三年中,EUV光刻技术用于所有高端智能手机、平板电脑、笔记本电脑和服务器。 然而,摩尔定律必须继续前进,芯片制造商继续推进他们的路线图,这意味着他们将需要进一步缩小器件的几何尺寸。

所以,在ASML,我和我的同事们正在开发下一代光刻技术。 它被称为高数值孔径EUV光刻技术,需要对系统的内部光学系统进行重大检修。 高数值孔径EUV光刻技术预计在2025年投入商业使用,芯片制造商将依靠其在本十年末实现承诺的进步。

01

光刻的三个因素

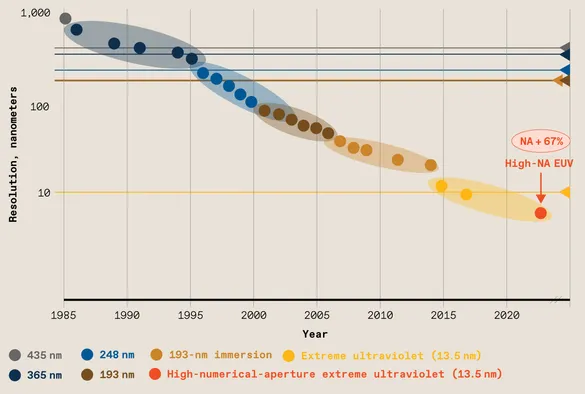

摩尔定律依赖于提高光刻技术的分辨率,以便芯片制造商能够铺设更精细的电路。在过去的35年中,工程师们通过研究三个因素的组合,实现了两个数量级的分辨率降低:光的波长、k1(封装过程相关因素的系数)和数值孔径(NA)(衡量系统发光角度范围的指标)。

来源:IEEE Spectrum

临界尺寸——即你可以用某种光刻曝光工具打印的最小特征尺寸——与光波长除以光学器件的数值孔径成正比。 所以,你可以通过使用更短的光波长或者更大的数值孔径,或者两者组合来获得更小的临界尺寸。例如,可以通过改进生产过程控制,使k1值尽可能接近 0.25 的物理下限。

一般来说,提高分辨率的最经济的方法是增加数值孔径、改进工具和过程控制,以实现更小的k1值。 只有当芯片制造商没有进一步改善数值孔径和k1值的选择后,他们才求助于降低光源的波长。

然而,该行业不得不多次改变波长。20世纪90年代末,波长由汞灯产生的365纳米通过氟化氪激光器发展到248纳米,在本世纪初又通过氟化氩激光器发展到193纳米。 在工业跃升到更短的波长之前,每一代光刻系统的数值孔径逐渐增大。

例如,随着193纳米技术的应用接近尾声,一种新的增加数值孔径的方法被引入:浸没式光刻。通过在透镜底部和晶圆之间放置水,NA可以从0.93显着扩大到1.35。自 2006 年左右推出以来,193 纳米浸没式光刻技术就成为业界最前沿光刻技术的研究热点。

在过去的四十年中,光刻技术的分辨率提高了大约一万倍。 这部分是由于使用了更小的光波长,但也需要更大的数值孔径和改进的处理技术。(来源:ASML)

02

EUV的黎明

但是,随着制造小于 30 纳米特征的需求增加,以及 193 纳米光刻技术的 NA 已达到极限,跟上摩尔定律的步伐变得越来越困难。

要制造小于30纳米的特征,要么使用多个图案来制作单层芯片特征——这在技术和经济上都是一项繁重的技术,要么就需要改变波长。经过 20 多年前所未有的开发努力,下一个新波长才得以问世:13.5 纳米EUV。

EUV需要一种全新的发光方式。 这是一个非常复杂的过程,需要用强大的二氧化碳激光在飞行途中撞击熔化的锡金属液滴。激光将锡蒸发成等离子体,发出光子能量的光谱。从这个光谱中,EUV光学系统收集所需的13.5纳米波长,然后通过一系列反射镜将其反射到图案掩模上,将图案投射到晶圆上。 所有这些都必须在超净真空下进行,因为13.5纳米波长会被空气吸收。 (在前几代光刻技术中,光通过掩模投射到晶圆上。 但是EUV很容易被吸收,因此掩模和其他光学元件必须具有反射性。)

长方形机器的剖面图。 紫色光束从机器内的物体上反射。在真空室中,EUV光(紫色)在从光掩模(顶部中心)反射之前,被多个镜面反射。 从那里,光继续它的旅程,直到它被投射到晶圆片(底部中心)上,带着光掩模的图案。 图示显示当今的商业系统,数值孔径为0.33。 未来系统中的光学系统将有所不同,数值孔径为0.55。(资料来源: ASML)

从193纳米光转换到EUV,在一定程度上降低了临界尺寸。 为了利用光刻技术的局限性,被称为“制造用设计”的过程,包括设置电路块的设计规则,在降低k1值方面做了很多工作。从现在的0.33到0.55, 现在是时候再次提高数值孔径了。

03

让高数值孔径EUV

发挥作用

将数值孔径从今天的0.33提高到目标值0.55不可避免地需要一系列其他调整。 像EUV光刻这样的投影系统,在晶圆片上和掩模上都有数值孔径。当你在晶片上增加数值孔径时,它也会增加掩模上的NA。因此,在掩模处,入射光锥和出射光锥变大,必须相互倾斜以避免重叠。 重叠的光锥会产生不对称的衍射图案,从而产生令人不悦的成像效果。

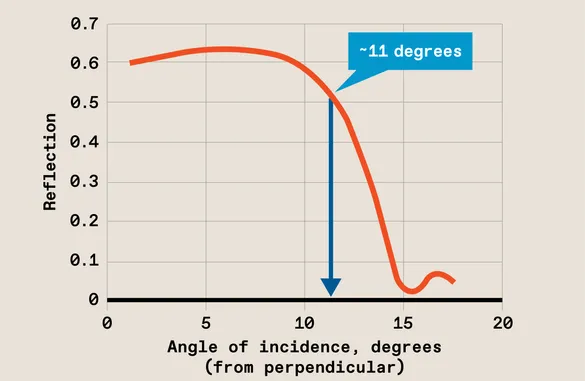

但是这个角度是有限的。 由于EUV光刻所需的反射掩模实际上是由多层材料制成的,因此无法确保在特定反射角以上获得适当的反射。EUV掩模的最大反射角为11度。还有其他的挑战,但反射角是最大的挑战。

曲线图向上弯曲,然后向右下降。下降的一个点被突出显示。如果EUV光以过于陡峭的角度照射掩膜,就无法正常反射。(来源:ASML)

一排三幅图像显示紫色圆锥体指向一个图案化的正方形。在今天的EUV中,掩模的反射角处于极限(左),增加EUV数值孔径将导致反射角过宽(中)。 因此,高数值孔径EUV使用非晶态光学,只允许角度在一个方向上增加(右)。 这样可以成像的场的大小是掩模的一半,因此掩模上的图案必须向一个方向变形,但这足以维持通过机器的吞吐量。(资料来源: ASML)

克服这一挑战的唯一途径是提高一种被称为“消磁”的质量。 消磁就像它听起来的那样——从面具上取下反射的图案并缩小它。为了弥补反射角的问题,我和我的同事不得不将退焦倍率提高一倍,达到8倍。 因此,在晶圆片上成像的掩模部分会小得多。 较小的图像场意味着它需要更长的时间来生成完整的芯片图案。 事实上,这一要求将使我们高数值孔径扫描仪的吞吐量降低到每小时100片以下——这一生产率水平将使芯片制造变得不经济。

值得庆幸的是,我们发现只需要增加一个方向的退磁,即反射角最大的方向。其他方向的退磁可以保持不变。这样,晶圆上的磁场尺寸就可以接受了——大约是当今 EUV 系统所用尺寸的一半,即 26 x 16.5 毫米,而不是 26 x 33 毫米。这种与方向有关的消磁(或称变形消磁)构成了我们的高 NA 系统的基础。光学元件制造商卡尔蔡司(Carl Zeiss)为设计和制造符合我们新机器所需规格的变形透镜付出了巨大的努力。

为了确保与半尺寸场相同的生产率水平,我们必须重新设计系统的光圈和晶圆台(分别容纳掩模和晶圆台的平台),并在扫描过程中使它们彼此同步。 这种重新设计的结果是纳米级精度,加速地提高了四倍。

04

2025年

高数值孔径EUV产量情况

第一个高数值孔径EUV系统,ASML EXE:5000,将于2024年初安装在我们与比利时纳米电子研究机构Imec联合开设的新实验室中。 该实验室将允许客户、掩模制造商、光刻胶供应商和其他人开发实现高数值孔径EUV所需的基础设施。

我们必须实现这一目标,因为高数值孔径EUV是维持摩尔定律的重要组成部分。 不过,达到0.55 NA 并不是最后一步。 从那时起,ASML、蔡司和整个半导体生态系统将进一步向更好、更快、更具创新性的技术迈进。

▶ 博通芯片疯了吧 !这行情还能暴涨十几倍!

▶ 不缺芯了,TI德州仪器急了

▶ 低端已经倒挂,高端还在涨价!TI、ST、NXP等热门芯片料号鉴定

▶ 英伟达A800显卡从7万飙到10万,需求倒爷满天飞

▶ AI服务器价格涨近20倍!带火哪些芯片?

点击查看往期内容

↓↓↓

你“在看”我吗?