上期话题

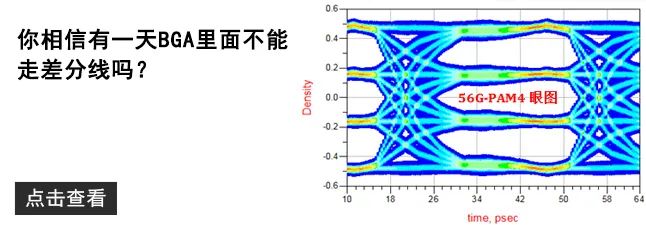

你相信有一天BGA里面不能走差分线吗?

(戳标题,即可查看上期文章回顾)

关于高速串行信号的PCB设计,大家会比较关注哪些点呢?

感谢各位网友的热情回答,本期是一个比较宽泛的问题,针对大多网友的回答,高速先生这边说下我们的一些看法:

1,首先很多网友问为什么会出现谐振点,其实主要原因是走线在反焊盘区域的参考层被削减了很多,因此导致该部分的阻抗发生突变,能量容易从这个区域泄露出去,再加上加工的层偏因素,因此会出现在比较高频的位置出现很大的谐振点;

2,因此我们在超高速的时候一定要注意这个影响,能做的事情包括pin的规划,不要在很内圈的位置定义高速pin,另外有空间的话尽量选择单端扇出的方式,还有就是叠层要设置合理,使得里面的走线既能满足阻抗的要求,走线也不至于太宽,保留更多的参考地;另外在加工方面也做更好的管控,使得层偏的风险减小;

3,其他更广泛的高速设计的一些原则就太多了,这边大概列几点比较重要的,例如等长、阻抗、stub、长度,这里就不一一展开了。

(以下内容选自部分网友答题)

那只能说ic设计太烂,pin规划没有做好

@ 何明远

评分:2分

我们公司更关注眼图。只要眼图没问题,就默认其阻抗,插损,反射,抖动,噪声没问题。如果眼图有问题,就得具体分析是什么问题和具体如何改善了

@ 欧阳

评分:2分

会关心以下几点。1.阻抗。通道中若阻抗一致能减小反射、串扰等问题。板厂和来料检验会用很大的精力和成本来进行阻抗管控,有他们层层把关我放心。一个系统是靠单板的强劲和顺畅的沟通维持着良好运转。多个单板组成一个系统,由连接器连接彼此,接口处沟通不顺畅,阻抗不连续是我们关心的问题。2.等长。等长影响接收端时序和共模大小,几mil差异是客户和领导非常关注的点。3.衰减。减肥跑步时,路程越远消耗热量越多,跑完,心崩气堵,不闻雷声。为了不累趴下,可以骑车,骑完,清风追花香,明月惊鸟语,微汗如信步。为了信号火力十足,要和板厂合作交流,联合进行好板材好铜箔的研究应用。4.拿以上文字请教硬件同事,硬汉说抖动也是客户关心的测试指标。

@ 山水江南

评分:3分

1.整个链路阻抗匹配。2.减小损耗。3.减小串扰。这是整体思路,详细的手段都是服务这三点。

@ 刘浩

评分:3分

可不可以理解为信号线跨分割地走线了

@ 柒

评分:2分

参考平面完整;尽量不换层,若换层则在换层过孔旁加地孔;要么不包地,要么保持一定距离均匀包地;注意端接电阻、电容的摆放及位置。

@ 涌

评分:2分

关键是参考层被分割,不连续,可以增加参考层的layout和盲孔工艺避免参考平面被分割

@ 天将降大任于我

评分:2分

觉得最本质的就是信号完整性,细分开来有诸如阻抗匹配、串扰、回流、时序等等关注点。但是在实际设计中往往会遇到这样一些让人困惑得问题:有必要把针对所有高速问题的解决措施都用到同一块PCB上吗?设计过的案子多了,也累积了各种各样的“经验法则”,当这些法则在同一个板子上冲突的时候,如何取舍?仿真不失为解决问题的有效手段,但是得到仿真结果后,我们如何对结果进行量化评估?

@ 陈达龙

评分:3分

会关注走线阻抗匹配,参考平面完整性,包地打过孔的间距,串扰大小,板材选择,玻纤布影响,铜箔粗糙度等等

@ 两处闲愁

评分:3分

高速串行主要考虑的还是损耗。根据走线长度和协议来考虑,一是板材的选择,二是stub的控制,三是过孔反焊盘和AC耦合电容焊盘优化,四是参考面的完整和连续(回流地过孔、缝补电容)。另外,BGA扇出区域的走线尽量避免经过过孔的反焊盘区域。最后是串扰控制,尽量TX和RX分层走线,实在分不开的要注意增大走线间距。

@ 绝对零度

评分:3分

关于高速串行信号PCB设计要注意若干方面,比如:【1】、等长为了等时,差分走线长度要匹配。【2】、走出BGA后,走线请保持恒定的宽度,以保持阻抗恒定。差分对间的间距尽可能的扩大。【3】、高速差分线串联阻容下面的地请100%挖空,至少挖空两个PCB层;【4】、要考虑玻纤效应、趋肤效应等。【5】、走线禁止跨越不完整的地平面。如果走线跨越分割地平面不可避免,请用1uF以下电容拼接两个地平面。【6】、如果差分走线不可避免使用过孔,请确保过孔的数量相等,并且过孔的间距相等。推荐过孔尽量靠近放在SOC芯片端。【7】、优化层叠方案、选用合适的高速板材及恰当的生产制程工艺;【8】、阻抗匹配、插损、回损、3W原则、眼图、Layout guide、信号换层处理也不可忽视、SI/PI/EMI方面也要注意,必要时借助仿真和测试手段……

@ 龍鳳呈祥

评分:3分

高速就走盲埋孔hdi啊,这样就没有参考的限制了

@ 伟波

评分:2分

阻抗匹配;走线串扰,考虑是否要包地;走线的换层与信号的回流问题;走线是否跨分割;信号的等长设计等。差分信号,高速信号速还需要考虑玻纤效应和趋肤效应等

@ 晴天

评分:3分

单根引出,不保持bga下差分阻抗的情况如何呢。

@ 柳辉

评分:2分

高速信号永远的,最基本的主题:阻抗控制和损耗。比如BGA内部差分出线、过孔换层、AC耦合电容、趋肤效应、玻璃纤布效应、连接器等引起的。

@ Ben

评分:3分

高速串行总线的pcb设计要注意阻抗连续,在过孔耦合电容都需要反焊盘处理,走线要参考平面完整,不要跨分割,走线尽量短

@ Alan

评分:3分

万不得已,等长>参考>阻抗

@ 见目辛

评分:2分

高速串行走线非常重要的一点就是损耗,这是保证信号质量的重要参数之一。介质损耗角,材料,层叠,加工工艺等都会影响损耗。此外,参考平面的选择,走线跨分割,与相邻层反焊盘距离等,过孔设计,时序等长规则,走线拐角,过孔穿线等都需要关注。最后别忘了仿真!!

@ 杆

评分:3分

如何看2020积分排行榜:

在主页输入关键词:2020积分

高速先生精选