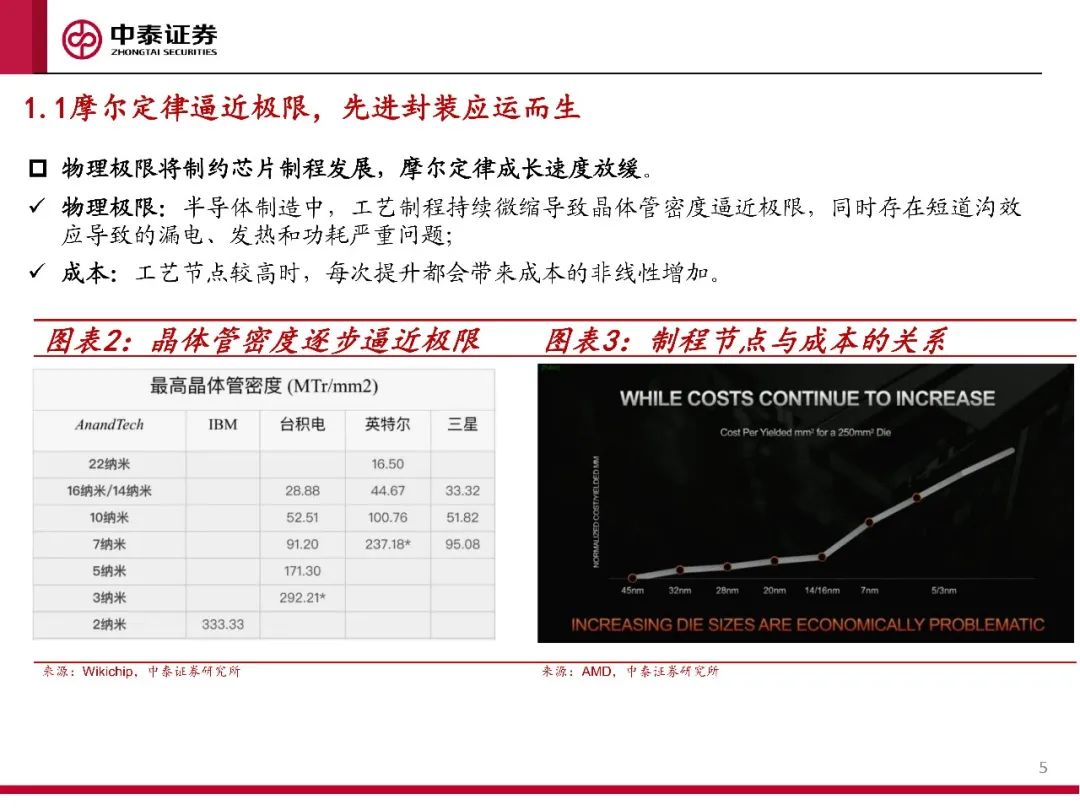

1.1摩尔定律逼近极限,先进封装应运而生

封装是指将生产加工后的晶圆进行切割、焊线塑封,使电路与外部器件实现连接,并为半 导体产品提供机械保护,使其免受物理、化学等环境因素损失的工艺。

半导体封装技术发展历程:第一阶段(20世纪70年代之前)通孔插装时代:典型的封装形式包括最初的金属圆形(TO型) 封装、双列直插封装(DIP)等;第二阶段(20世纪80年代以后)表面贴装时代:从通孔插装型封装向表面贴装型封装的转 变,从平面两边引线型封装向平面四边引线型封装发展; 第三阶段(20世纪90年代以后)面积阵列封装时代:从平面四边引线型向平面球栅阵列型 封装发展,引线技术从金属引线向微型段焊球方向发展。

先进封装应运而生:在“后摩尔时代”,行业从过去着力于晶圆制造技术节点的推进,逐渐转 向封装技术的创新。先进封装技术不仅可以增加功能、提升产品价值,还能有效降低成本,成 为延续摩尔定律的重要路径。

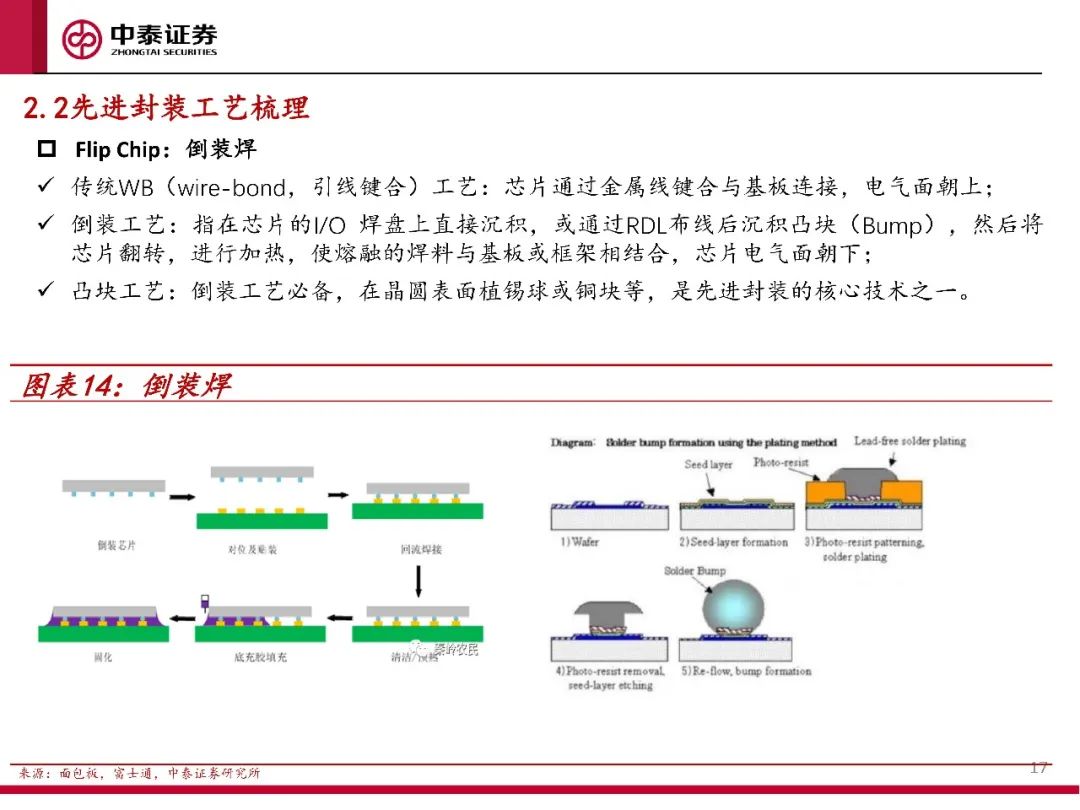

先进封装定义:采用了先进的设计思路和先进的集成工艺,对芯片进行封装级重构,并且能有 效提系统高功能密度的封装技术。现阶段先进封装主要是指倒装焊(Flip Chip)、 晶圆级封装 (WLP) 、2.5D封装(Interposer) 、3D封装(TSV)等。

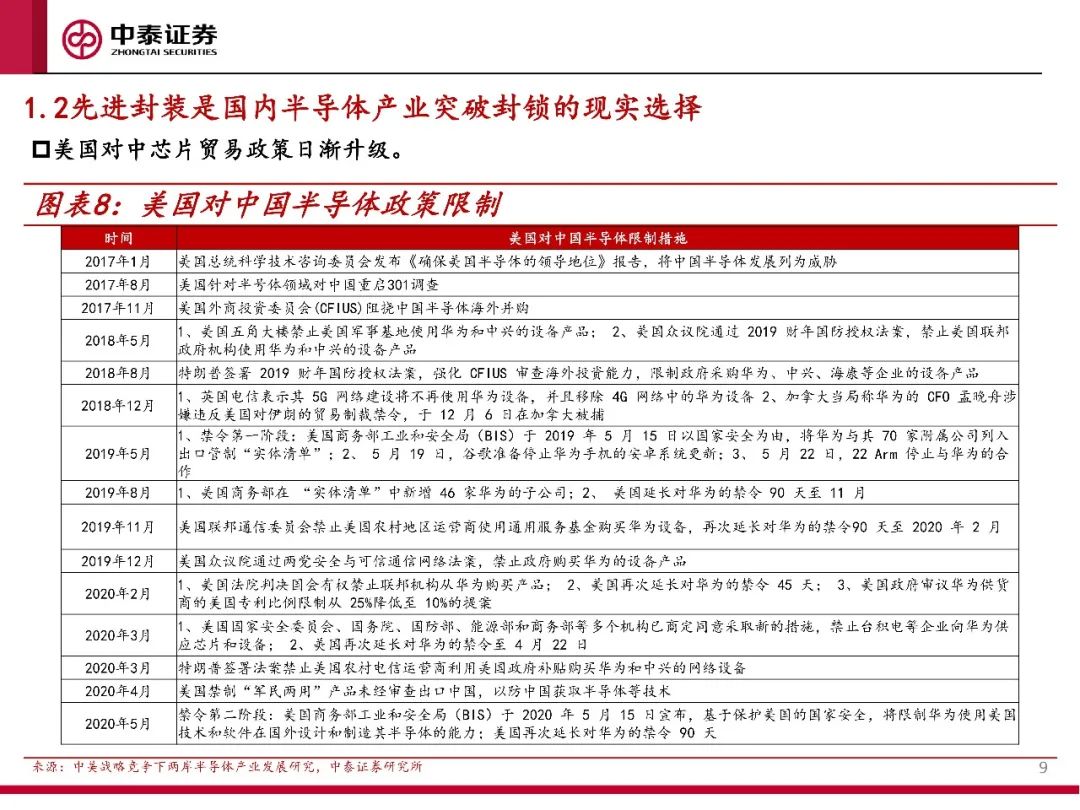

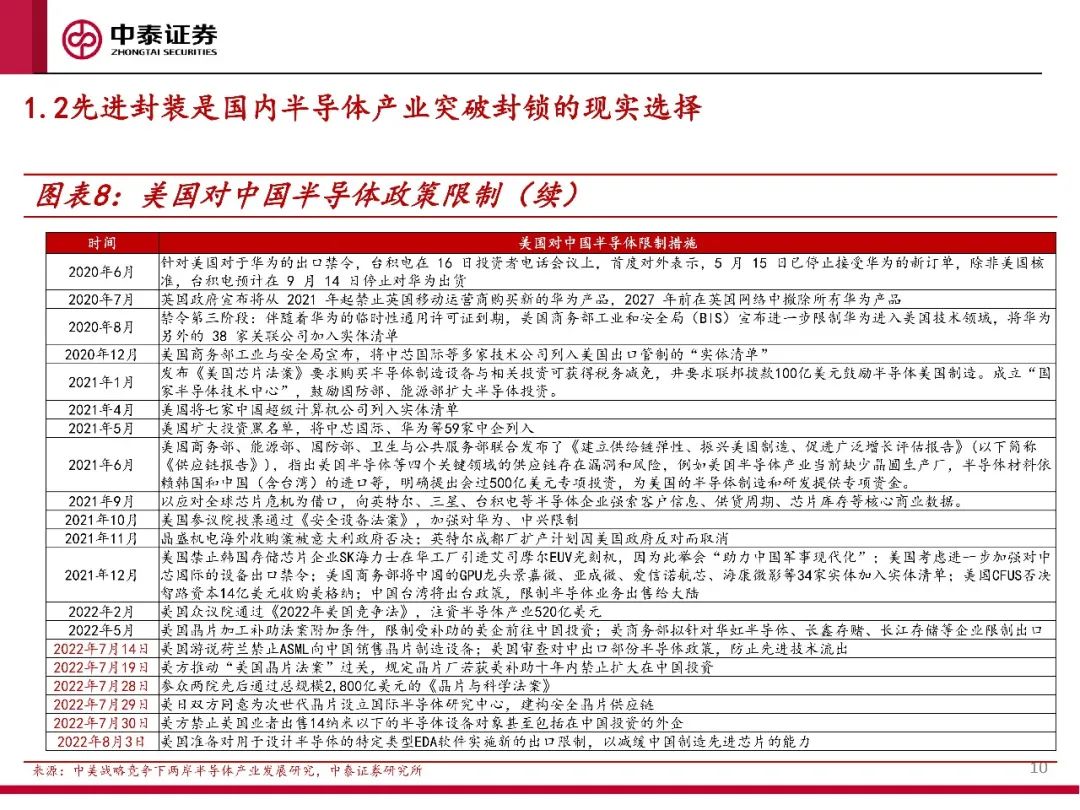

1.2 先进封装是国内半导体产业突破封锁的重要方式

先进封装是国内半导体产业突破封锁的重要方式:半导体是中国卡脖子问题,美国遏制中国 发展先进技术的政策,长期不会改变。先进封装可在现有技术节点下,进一步提升芯片性能, 是国内半导体企业突破封锁的重要方式。

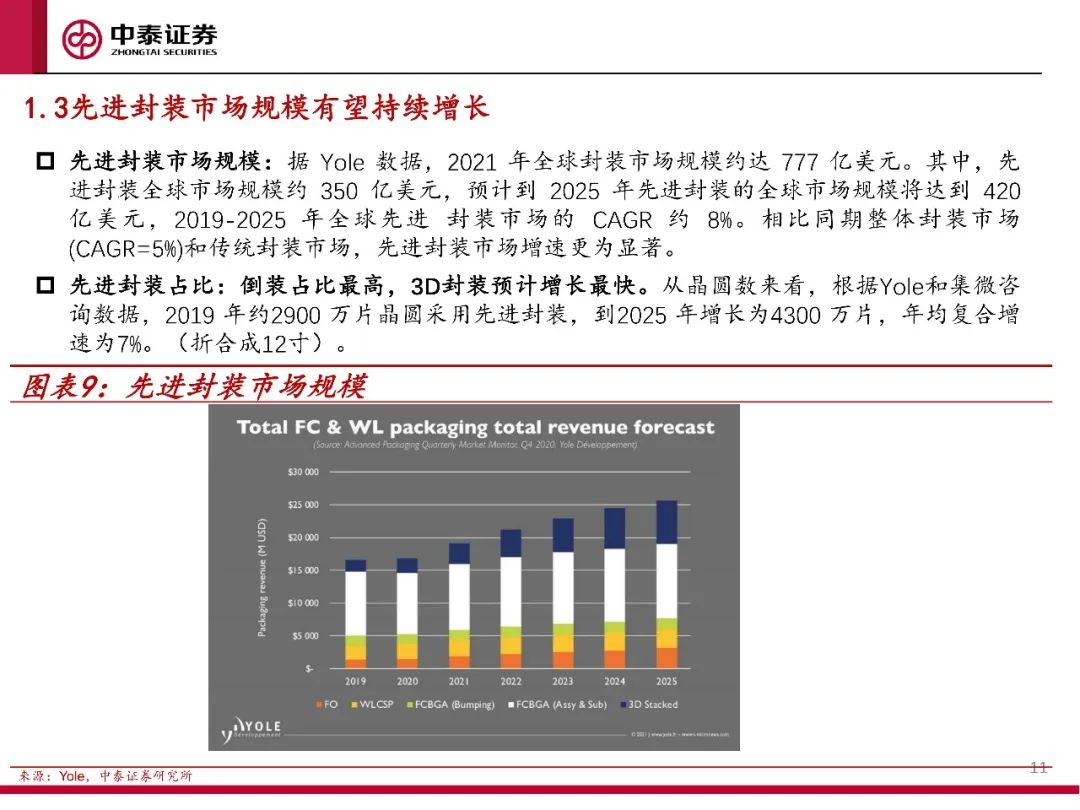

1.3 先进封装市场规模有望持续增长

先进封装市场规模:据 Yole 数据,2021 年全球封装市场规模约达 777 亿美元。其中,先 进封装全球市场规模约 350 亿美元,预计到 2025 年先进封装的全球市场规模将达到 420 亿美元,2019-2025 年全球先进 封装市场的 CAGR 约 8%。相比同期整体封装市场 (CAGR=5%)和传统封装市场,先进封装市场增速更为显著。

先进封装占比:倒装占比最高,3D封装预计增长最快。从晶圆数来看,根据Yole和集微咨 询数据,2019 年约2900 万片晶圆采用先进封装,到2025 年增长为4300 万片,年均复合增 速为7%。(折合成12寸)。

2.1半导体封装工艺

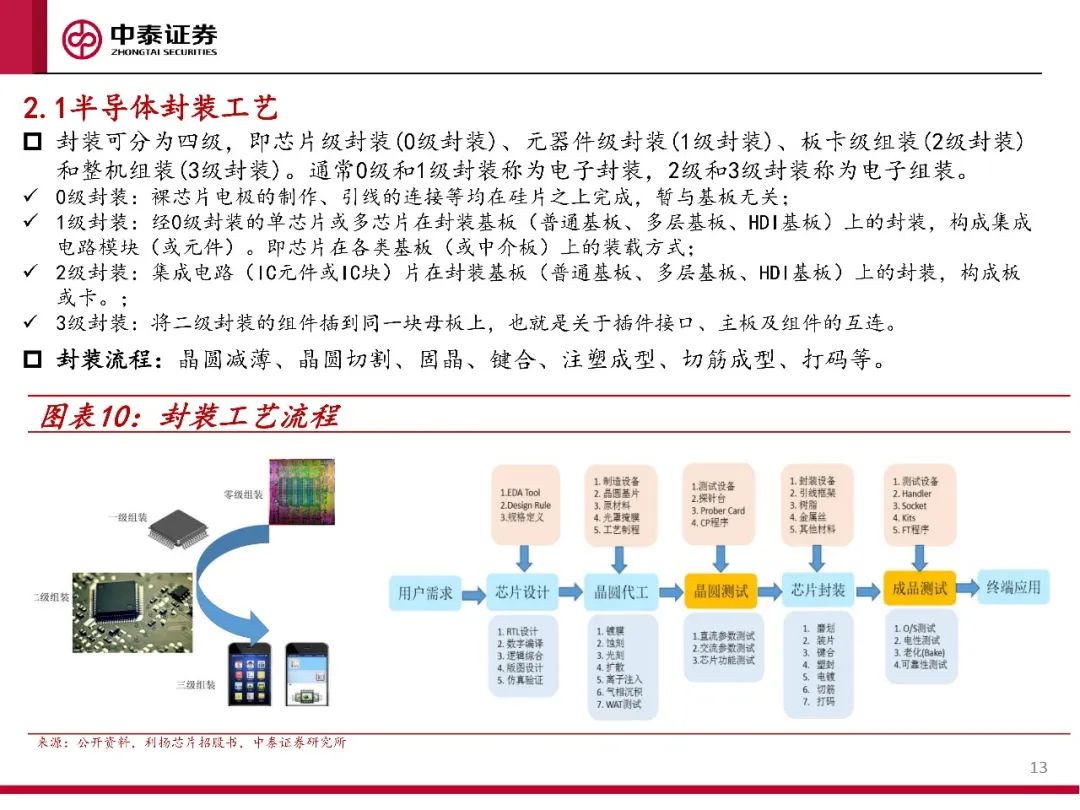

封装可分为四级,即芯片级封装(0级封装)、元器件级封装(1级封装)、板卡级组装(2级封装) 和整机组装(3级封装)。通常0级和1级封装称为电子封装,2级和3级封装称为电子组装。0级封装:裸芯片电极的制作、引线的连接等均在硅片之上完成,暂与基板无关;1级封装:经0级封装的单芯片或多芯片在封装基板(普通基板、多层基板、HDI基板)上的封装,构成集成 电路模块(或元件)。即芯片在各类基板(或中介板)上的装载方式;2级封装:集成电路(IC元件或IC块)片在封装基板(普通基板、多层基板、HDI基板)上的封装,构成板 或卡。;3级封装:将二级封装的组件插到同一块母板上,也就是关于插件接口、主板及组件的互连。封装流程:晶圆减薄、晶圆切割、固晶、键合、注塑成型、切筋成型、打码等。

2.2先进封装工艺梳理

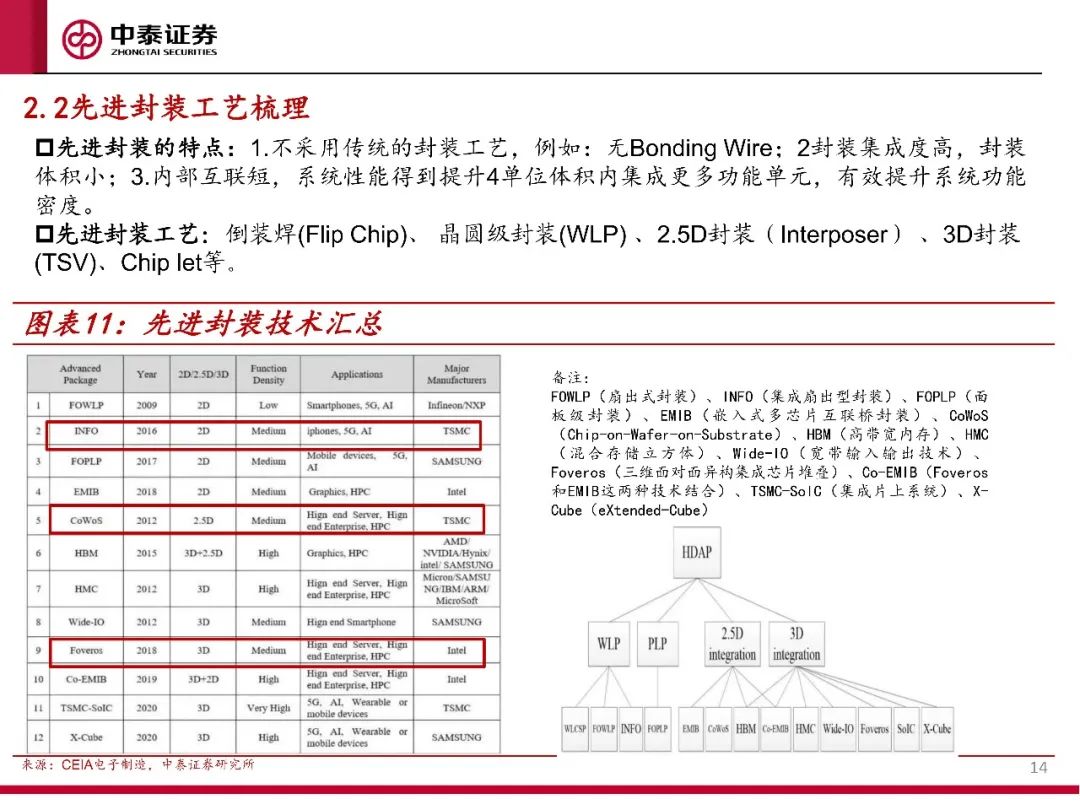

先进封装的特点:1.不采用传统的封装工艺,例如:无Bonding Wire;2封装集成度高,封装 体积小;3.内部互联短,系统性能得到提升4单位体积内集成更多功能单元,有效提升系统功能 密度。

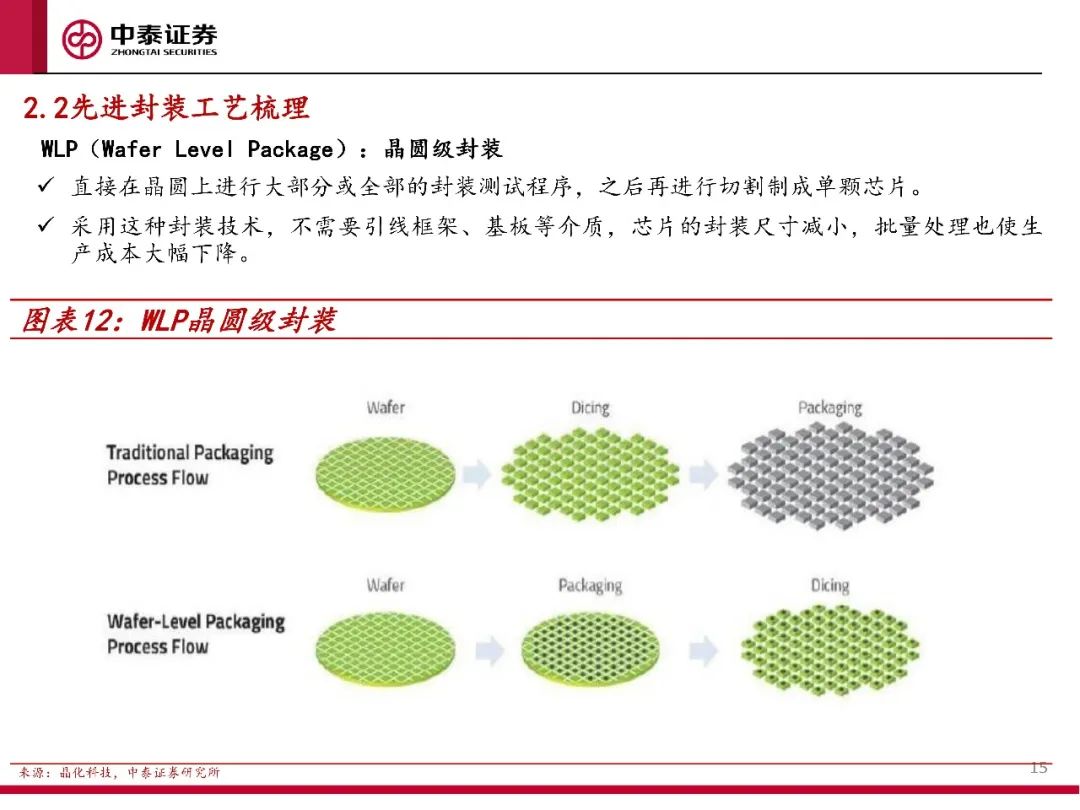

先进封装工艺:倒装焊(Flip Chip)、 晶圆级封装(WLP) 、2.5D封装(Interposer) 、3D封装 (TSV)、Chip let等。

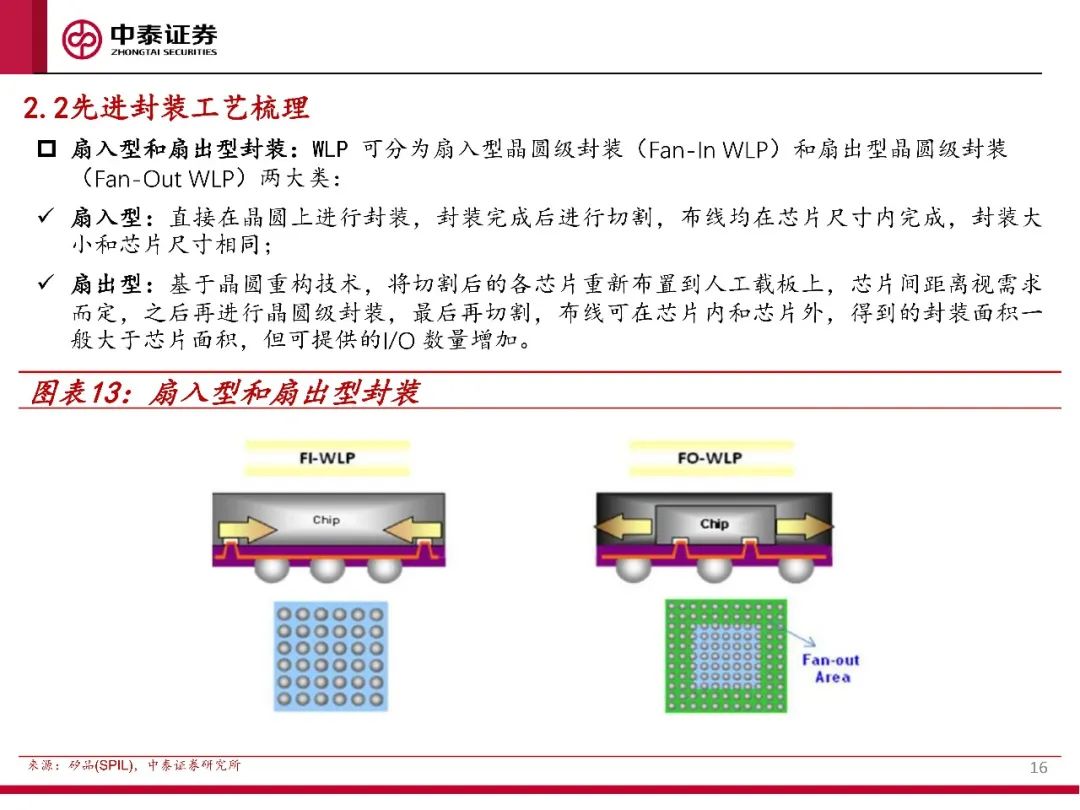

扇入型和扇出型封装:WLP 可分为扇入型晶圆级封装(Fan-In WLP)和扇出型晶圆级封装 (Fan-Out WLP)两大类:扇入型:直接在晶圆上进行封装,封装完成后进行切割,布线均在芯片尺寸内完成,封装大 小和芯片尺寸相同;扇出型:基于晶圆重构技术,将切割后的各芯片重新布置到人工载板上,芯片间距离视需求 而定,之后再进行晶圆级封装,最后再切割,布线可在芯片内和芯片外,得到的封装面积一 般大于芯片面积,但可提供的I/O 数量增加。

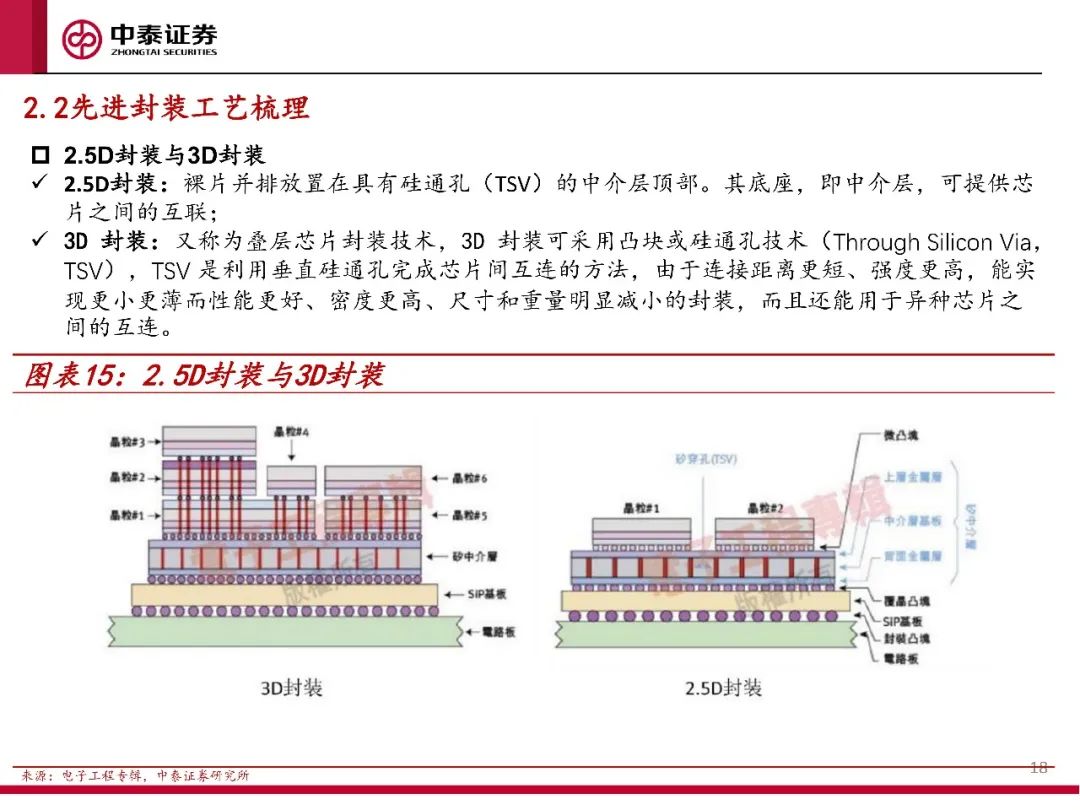

2.5D封装与3D封装 。2.5D封装:裸片并排放置在具有硅通孔(TSV)的中介层顶部。其底座,即中介层,可提供芯 片之间的互联;3D 封装:又称为叠层芯片封装技术,3D 封装可采用凸块或硅通孔技术(Through Silicon Via, TSV),TSV 是利用垂直硅通孔完成芯片间互连的方法,由于连接距离更短、强度更高,能实 现更小更薄而性能更好、密度更高、尺寸和重量明显减小的封装,而且还能用于异种芯片之 间的互连。

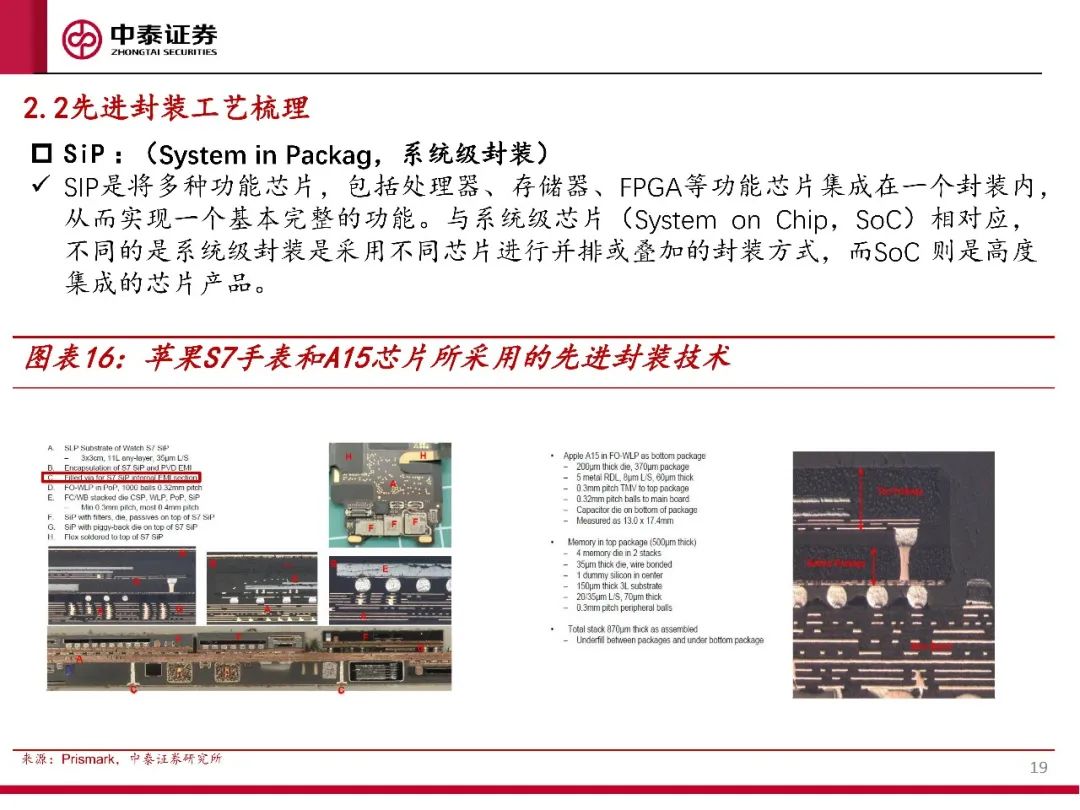

SiP:(System in Packag,系统级封装)。SIP是将多种功能芯片,包括处理器、存储器、FPGA等功能芯片集成在一个封装内, 从而实现一个基本完整的功能。与系统级芯片(System on Chip,SoC)相对应, 不同的是系统级封装是采用不同芯片进行并排或叠加的封装方式,而SoC 则是高度 集成的芯片产品。

Chiplet :Chiplet 技术是一种通过总线和先进封装技术实现异质集成的封装形式;作用:1.降低单片晶圆集成工艺良率风险,达到成本可控,有设计弹性,可实现芯片定制 化;2.Chiplet 将大尺寸的多核心的设计,分散到较小的小芯片,更能满足现今高效能运算处 理器的需求;3.弹性的设计方式不仅提升灵活性,且可实现包括模块组装、芯片网络、异构系 统与元件集成四个方面的功能。

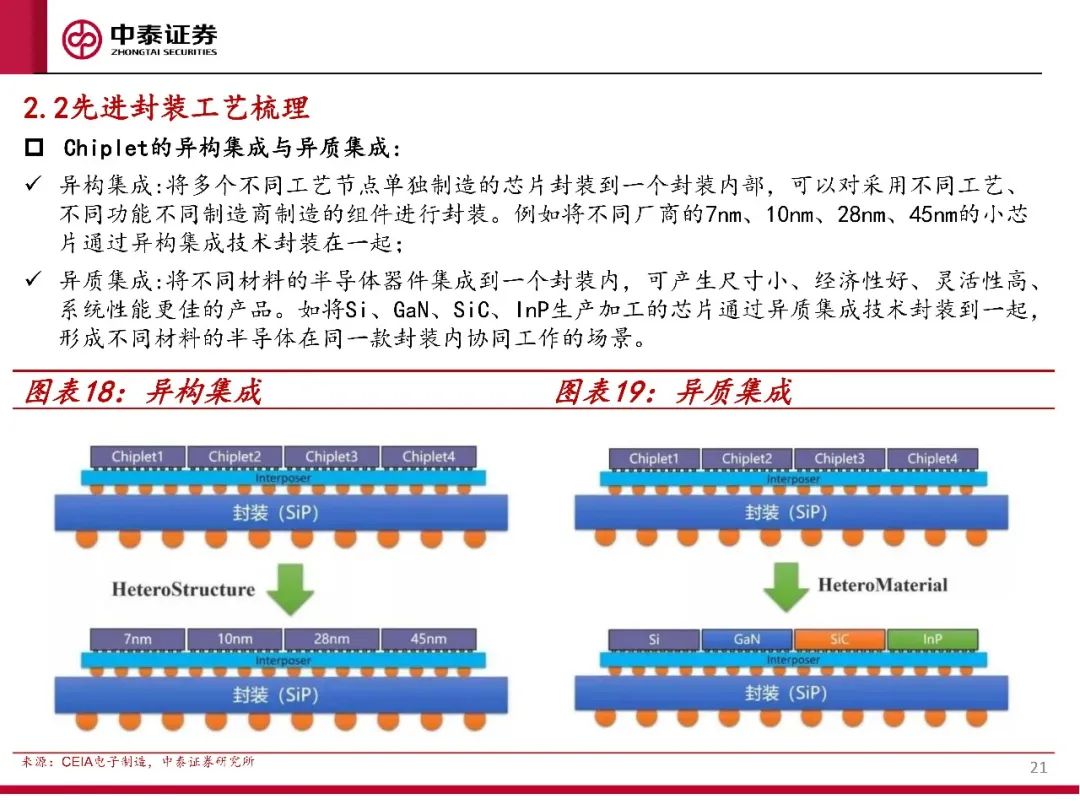

Chiplet的异构集成与异质集成:异构集成:将多个不同工艺节点单独制造的芯片封装到一个封装内部,可以对采用不同工艺、 不同功能不同制造商制造的组件进行封装。例如将不同厂商的7nm、10nm、28nm、45nm的小芯 片通过异构集成技术封装在一起;异质集成:将不同材料的半导体器件集成到一个封装内,可产生尺寸小、经济性好、灵活性高、 系统性能更佳的产品。如将Si、GaN、SiC、InP生产加工的芯片通过异质集成技术封装到一起, 形成不同材料的半导体在同一款封装内协同工作的场景。

2.3典型公司先进封装技术布局

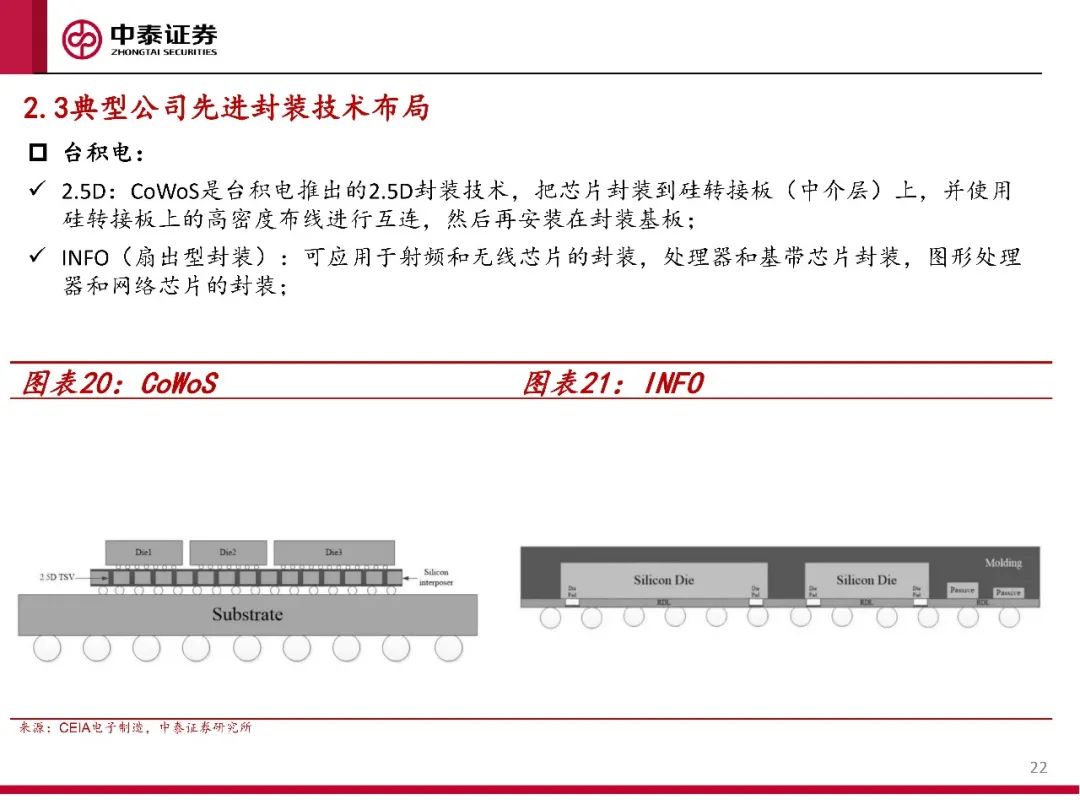

台积电:2.5D:CoWoS是台积电推出的2.5D封装技术,把芯片封装到硅转接板(中介层)上,并使用 硅转接板上的高密度布线进行互连,然后再安装在封装基板;INFO(扇出型封装):可应用于射频和无线芯片的封装,处理器和基带芯片封装,图形处理 器和网络芯片的封装;

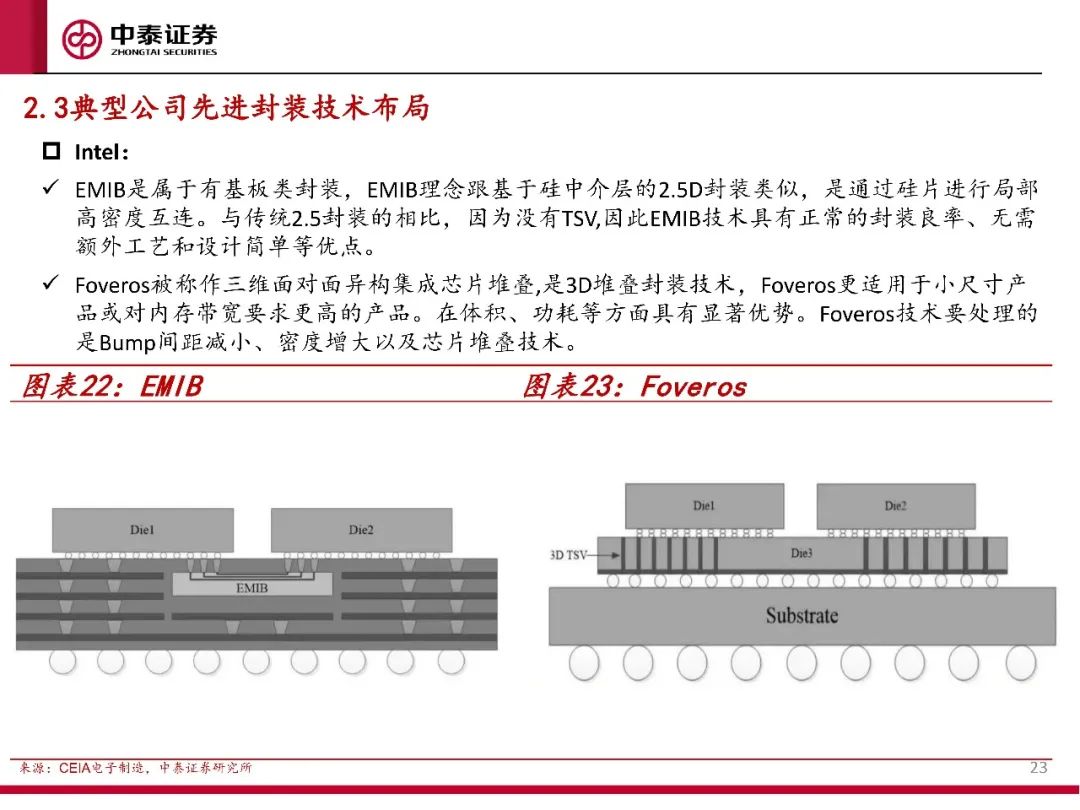

Intel:EMIB是属于有基板类封装,EMIB理念跟基于硅中介层的2.5D封装类似,是通过硅片进行局部 高密度互连。与传统2.5封装的相比,因为没有TSV,因此EMIB技术具有正常的封装良率、无需 额外工艺和设计简单等优点。Foveros被称作三维面对面异构集成芯片堆叠,是3D堆叠封装技术,Foveros更适用于小尺寸产 品或对内存带宽要求更高的产品。在体积、功耗等方面具有显著优势。Foveros技术要处理的 是Bump间距减小、密度增大以及芯片堆叠技术。

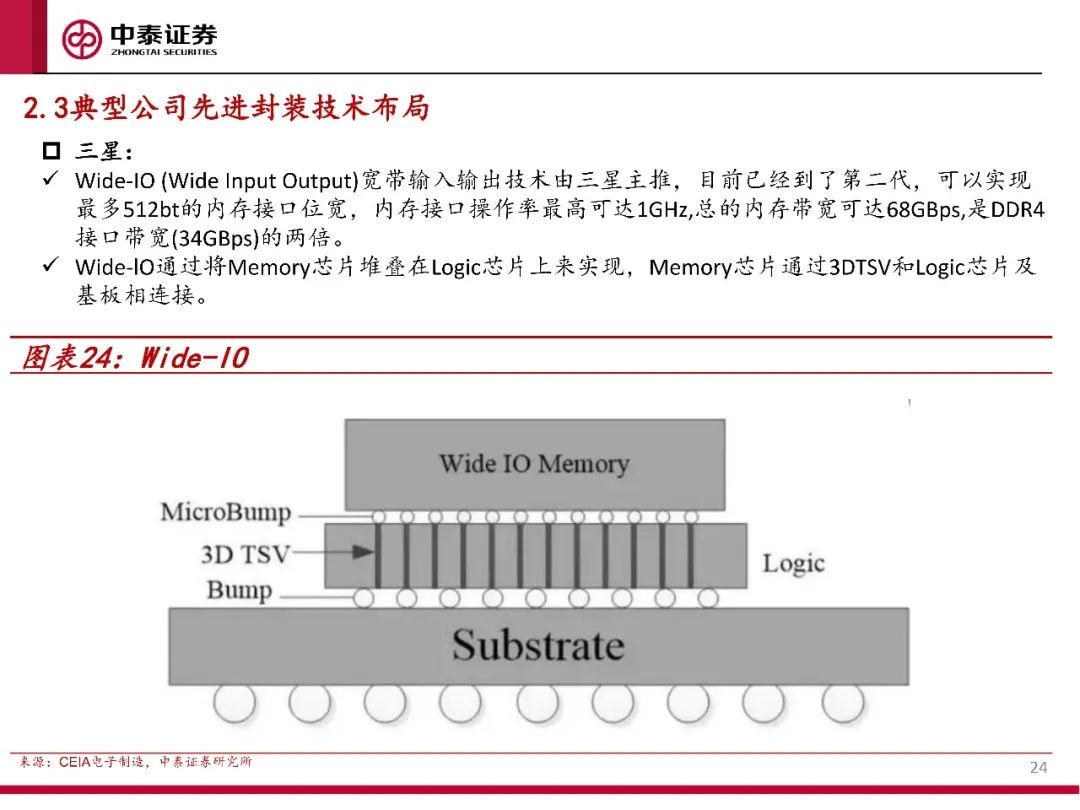

三星:Wide-IO (Wide Input Output)宽带输入输出技术由三星主推,目前已经到了第二代,可以实现 最多512bt的内存接口位宽,内存接口操作率最高可达1GHz,总的内存带宽可达68GBps,是DDR4 接口带宽(34GBps)的两倍。Wide-lO通过将Memory芯片堆叠在Logic芯片上来实现,Memory芯片通过3DTSV和Logic芯片及 基板相连接。

2.4半导体封装设备梳理

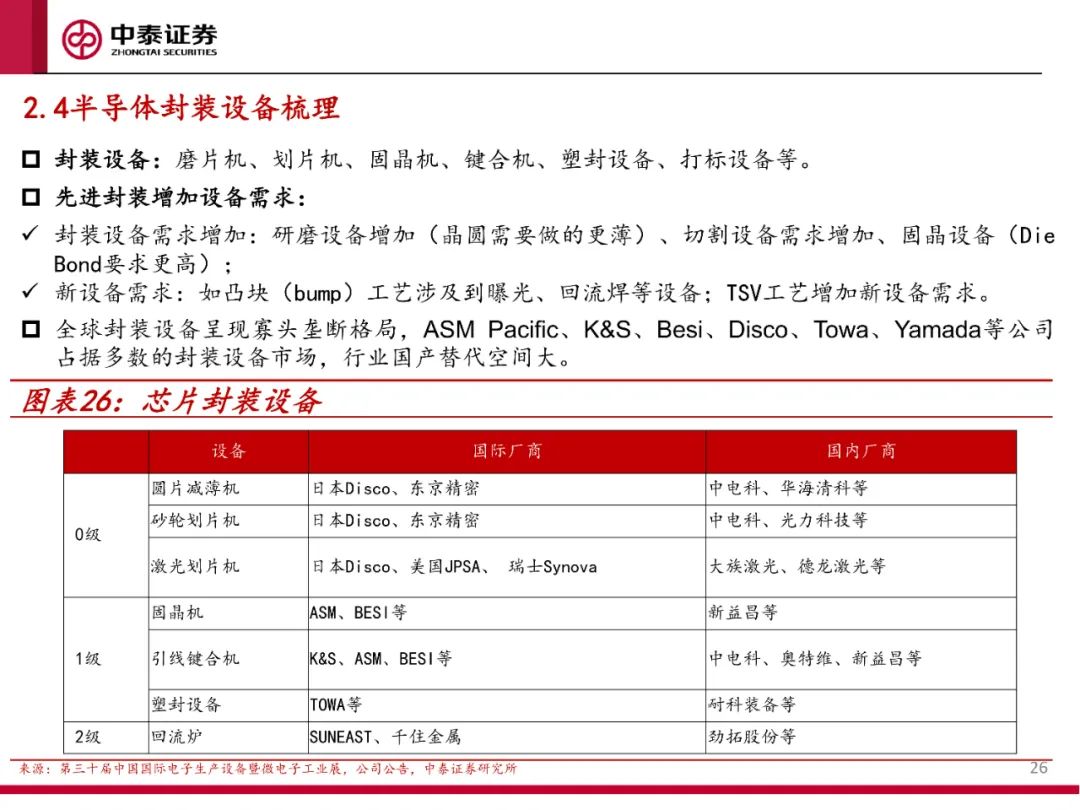

封装设备:磨片机、划片机、固晶机、键合机、塑封设备、打标设备等。先进封装增加设备需求:封装设备需求增加:研磨设备增加(晶圆需要做的更薄)、切割设备需求增加、固晶设备(Die Bond要求更高);新设备需求:如凸块(bump)工艺涉及到曝光、回流焊等设备;TSV工艺增加新设备需求。全球封装设备呈现寡头垄断格局,ASM Pacific、K&S、Besi、Disco、Towa、Yamada等公司 占据多数的封装设备市场,行业国产替代空间大。

文章来源:中泰证券

免责声明 | 部分素材源自网络,版权归原作者所有。如涉侵权,请联系我们处理

2023年9月24-26日 中国·深圳

2023先进电子材料创新大会聚焦于“新材料与产业发展新机遇”,瞄准全球技术和产业制高点,紧扣电子信息产业关键基础环节的短板,不断延展,着力突破高端先进电子材料产业化发展难题,拓宽新兴市场应用。本次大会挚邀请国内外知名专家、学者、头部企业,多视角共同探讨先进电子材料产业发展新机遇,从应用需求逆向开发,产学研联动,驱动先进电子产业协同创新发展,打造国际高端电子材料产学研交流对接平台。

扫码立即报名