图 (1)

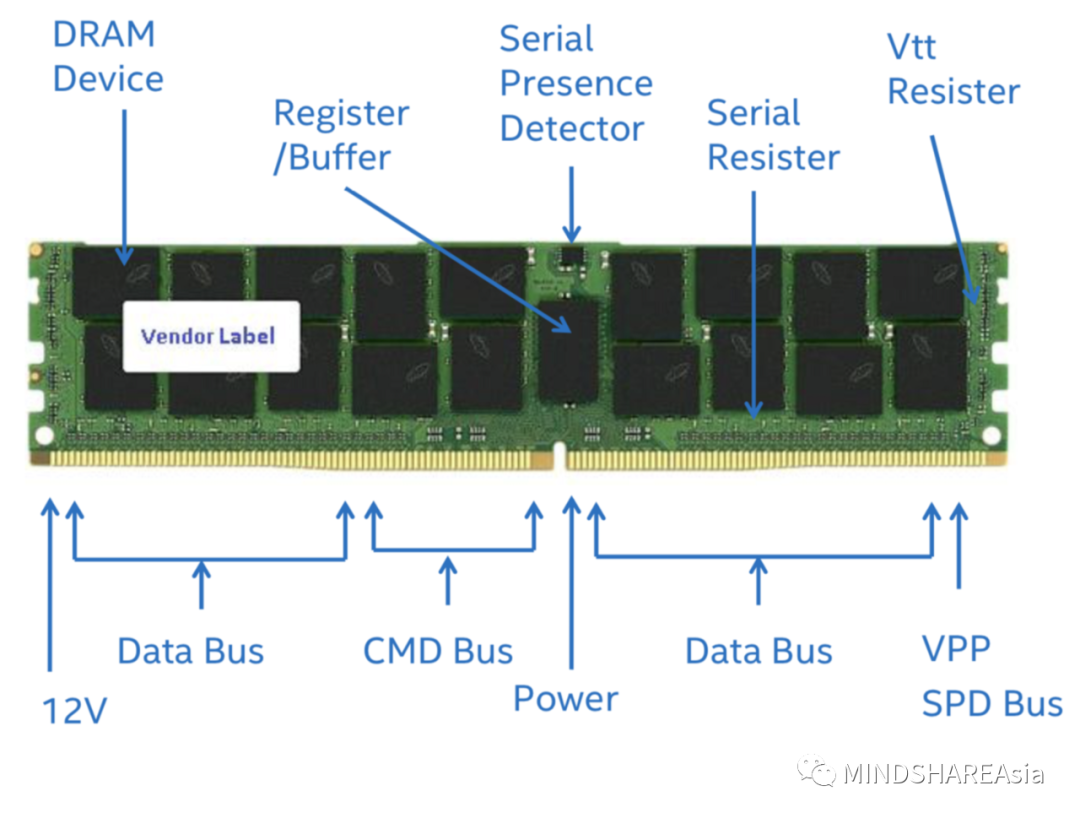

Channel:一个Channel由一个或者多个Rank组成,其宽度由控制器决定。当前主流的个人电脑和服务器中,一个Channel的宽度为64bit,可根据内存控制器是否支持ECC而扩展额外的8bit。也就是说如果不支持ECC的Channel,其宽度为64bit,而支持ECC的Channel,其宽度为72bit。市面上两种内存条都有销售。

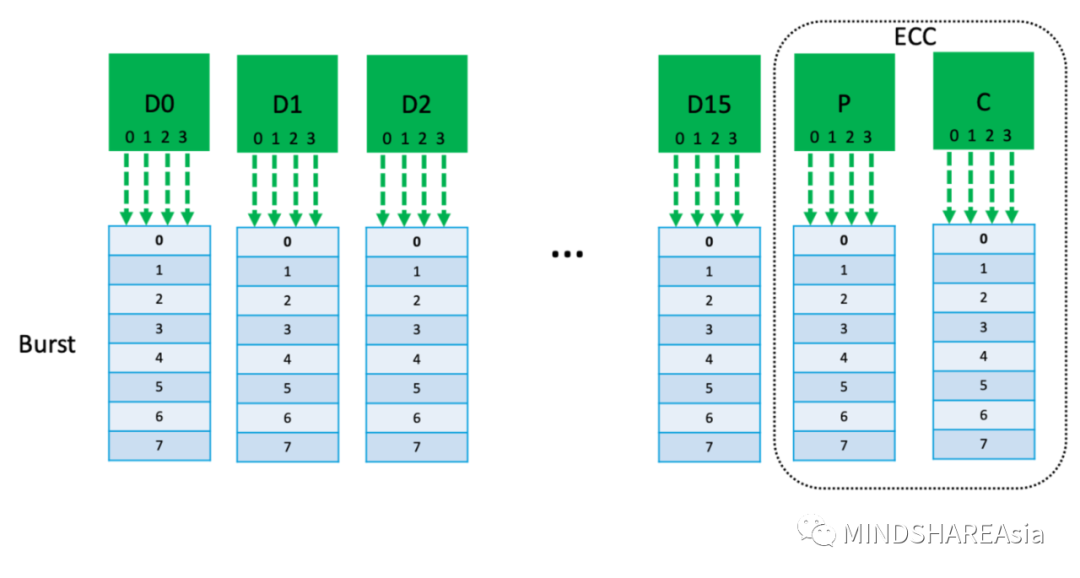

Rank:一个Channel里面,同一个CS(Chip Select)信号选中的所有Device就是一个Rank。同一个Rank中所有的Device共用命令,地址和控制信号。拿读操作举例,内存控制器发起的一个读操作,其实将作用于该Channel的某个Rank中所有的Device。所有Device的数据线共同输出达到内存控制器所需的宽度。例如,采用X4的颗粒,组成不带ECC功能的一个Rank则需要64/4 = 16个X4的Device。大家可以计算一下如果采用X8或者X16宽度的颗粒,需要多少个呢?

注:本文我们将主要以X4的Device来讨论

注:X16的颗粒一般不被用来组成带ECC的Rank

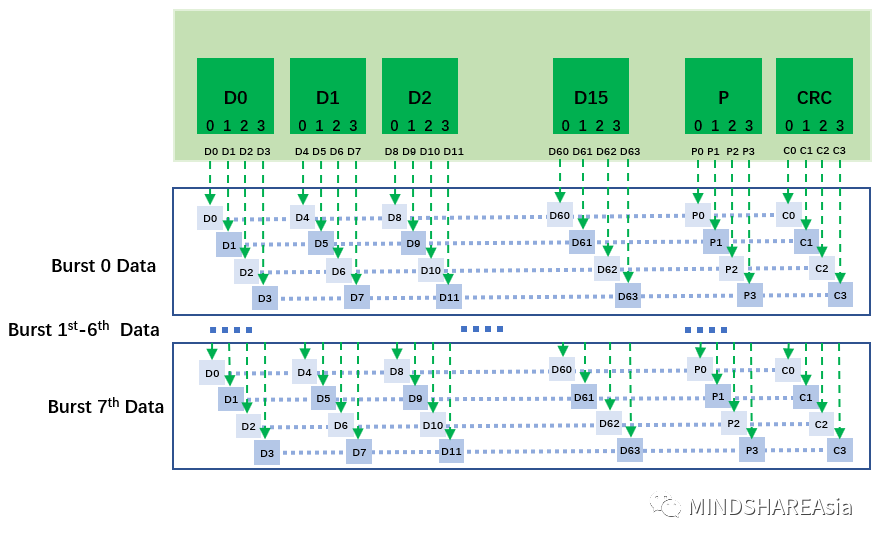

Cacheline:Cacheline通常是指是处理器中Cache Unit(缓存模块)缓存一笔数据的标准大小。根据处理器的不同,Cacheline的大小是不一样的。当前主流的个人电脑和服务器中,Cacheline的大小为64 Byte。为了设计方便,处理器内部搬运可被缓存的数据也采用同样的大小64B。为了满足该需求,一个Rank被设计成了64bit的数据位宽,而JEDEC(DDR标准组织)设计了burst传输。一个Burst的长度可以是8,从而一次读操作,可以让颗粒一次吐出8笔数据。从而达到64bit X 8 = 64B的大小。具体参考图(2)。

图(2)

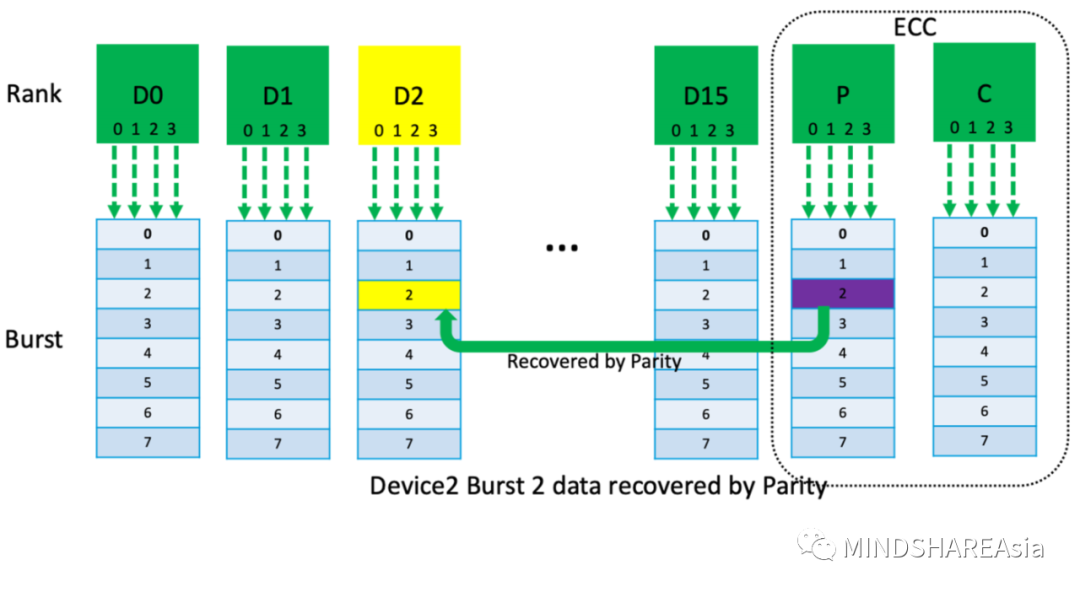

CE(CorrectableError):可纠正错误是指硬件(芯片)可以直接纠正的错误。由于内存控制器设计不一样,对于可纠正错误的能力可能存在不同。例如,主流x86服务器的内存控制器(支持带ECC的内存条),在一次读操作中,一个X4宽度的Device内的任意错误都是可纠正的,包括ECC的Device。如果Rank是X8宽度的Device组成,其纠正能力还是与X4的Device宽度及位置保持一致。在X8的一个Device中,只有DQ0-3,或者DQ4-7可以被纠正。如果是DQ2-5,虽然是X4宽度但位置与X4时不对应,也无法纠正。

注:DQ0即D0,或者D0_0,DQ63则是D63,或者D15_3

UCE(Uncorrectable Error): 不可纠正错误是指硬件(芯片)无法直接纠正的错误。例如,在一次读操作中,错误数据位分布在不同X4的Device范围,以现有内存控制设计来看,属于不可纠正错误。

图(3)

注:D15_3为Device15的DQ3信号,从Rank角度看,为图中的D63

D2_0=P0(-)(D0_0+D1_0+D3_0…D15_0+C0)

D2_1=P1(-)(D0_1+D1_1+D3_1…D15_1+C1)

D2_2=P2(-)(D0_2+D1_2+D3_2…D15_2+C2)

D2_3=P3(-)(D0_3+D1_3+D3_3…D15_3+C3)

图(4)

|

高端微信群介绍 |

|

|

创业投资群 |

AI、IOT、芯片创始人、投资人、分析师、券商 |

|

闪存群 |

覆盖5000多位全球华人闪存、存储芯片精英 |

|

云计算群 |

全闪存、软件定义存储SDS、超融合等公有云和私有云讨论 |

|

AI芯片群 |

讨论AI芯片和GPU、FPGA、CPU异构计算 |

|

5G群 |

物联网、5G芯片讨论 |

|

第三代半导体群 |

氮化镓、碳化硅等化合物半导体讨论 |

|

存储芯片群 |

DRAM、NAND、3D XPoint等各类存储介质和主控讨论 |

|

汽车电子群 |

MCU、电源、传感器等汽车电子讨论 |

|

光电器件群 |

光通信、激光器、ToF、AR、VCSEL等光电器件讨论 |

|

渠道群 |

存储和芯片产品报价、行情、渠道、供应链 |

< 长按识别二维码添加好友 >

加入上述群聊

带你走进万物存储、万物智能、

万物互联信息革命新时代