UTMI (USB2.0 Transceiver Macrocell Interface):USB2.0 通用传输接口。最初设计是为了减少开发厂商的工作量,旨在提供一种通用标准,来完成USB 2.0 的 底层协议数据处理。UTMI 的出现是为了加速USB2.0 外设的开发。

UTMI 最主要的作用主要是负责USB 协议中最底层的物理电信号的转换。其本质是一个接口规范,与usb phy 相连。

下图总结了在这个规范中表达的一些概念:

UTM 处理低级别的USB协议和信号。这包括诸如;数据序列化和反序列化、位填充和时钟恢复和同步等特性。

UTM的主要焦点是将数据的时钟域从USB 2.0速率转移到与ASIC中的一般逻辑兼容的速率。

UTM 的关键特点:

UTMI被设计用于支持HS/FS、仅FS和仅LS的UTM实现。这三个选项允许一个单一的SIE实现被使用与任何速度的USB收发器。供应商可以选择最满足其需求的收发器性能。

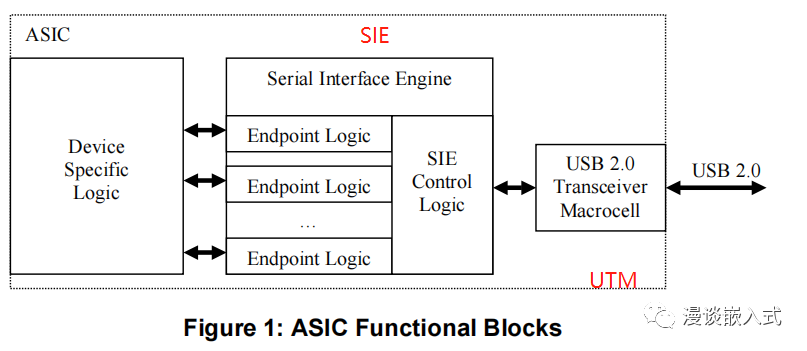

SIE 可以进一步细分为两种类型的子块:SIE 控制逻辑 和 端点逻辑。

SIE 控制逻辑包含 USB PID 和 地址识别逻辑,以及其他处理USB数据包和事务的排序和状态机逻辑。

端点逻辑:包含特定于端点的逻辑:端点编号识别、FIFO和FIFO控制等。

一般来说,任何USB实现都需要SIE控制逻辑,而端点的数量和类型将随着应用程序和性能要求的不同而变化。

这是将USB接口与设备的特定应用程序连接起来的逻辑。

UTM block 如上图。

Device-> HOST:并行 TxData -> bit Stufffer -> NRZI Encoder -> xmit -> D+/D- -> HOST HOST -> Device:Host -> D+/D- -> NRZI Decoder -> Bit Unstuffer -> 并行Rx Data -> Device

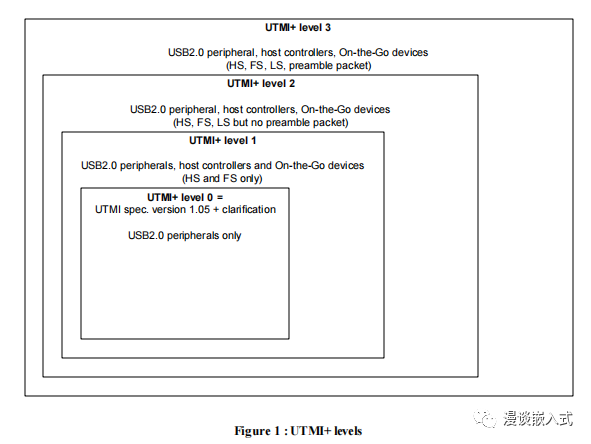

UTMI 第一个版本,是2001 年 发布的(UTMI spec V1.05)。后续随着UTM 发展,引出了UMTI+ 版本。具体的版本如下:

| 版本 | 功能 | 备注 |

|---|---|---|

| UTMI+ level0 | 仅仅支持 USB2.0 设备 | 也是UTMI 第一个版本, V1.05 版本 |

| UTMI+ leve1 | 支持USB2.0 设备、host 和 OTG 功能(HS/FS)。 | 不支持 LS, 2.0 用得最广的接口 |

| UTMI+ level2 | 支持USB2.0 设备、host 和 OTG 功能 (HS/FS/LS with no hub support) | 支持LS 模式 |

| UTMI+ level3 | 支持 USB2.0 设备、host 和 OTG 功能(HS/FS/LS with hub support) |

UTMI+ 不同版本接口协议规范是向下兼容的。对于学习USB2.0 我们可以研究UTMI+ level0 或者level1 就够了,高版本的协议无非是在旧有的协议基础上新增了一些信号处理。

UMTI+ 不同版本之间信号还是很多的。我们以usb2.0 device 为主先介绍level0/level1。

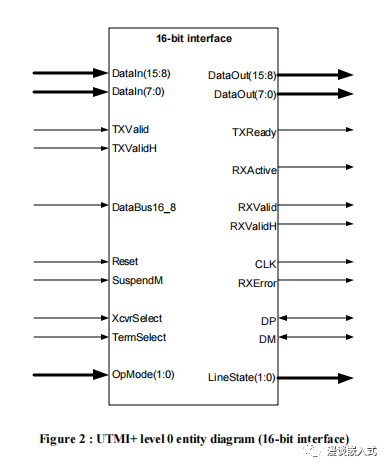

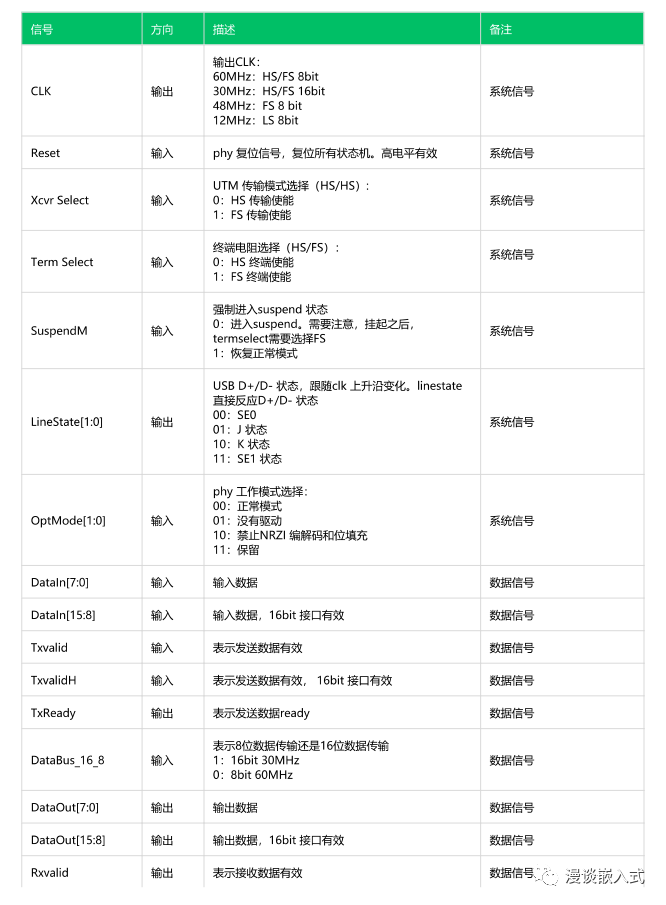

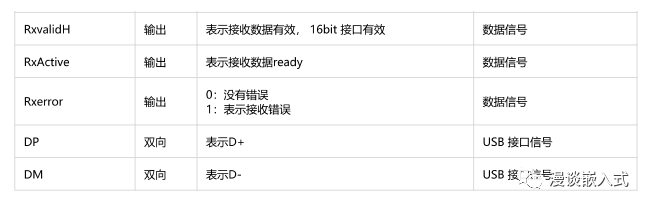

UTMI+ level0 规范,来源于UTMI 1.05 接口规范。下图给出了具有16位接口的UTMT+ level0 收发器所需要的所有接口信号:

对于具有8位接口的UTMI+0级收发器,TXValidH、RXValidH、DataBus16_8、DataIn(15:8)和DataOut(15:8)信号,则是不需要的。

对于 USB 2.0 phy 调试我们需要关注的几个信号(注意phy 的调试可能只在芯片fpga 阶段,或者外挂usb phy 才存在。一旦芯片集成完了,无法修改,后续的调试就大概率涉及不到phy 的调试):

一旦速度枚举成功,说明整个输入输出信号无误,剩下的就到软件层面了。

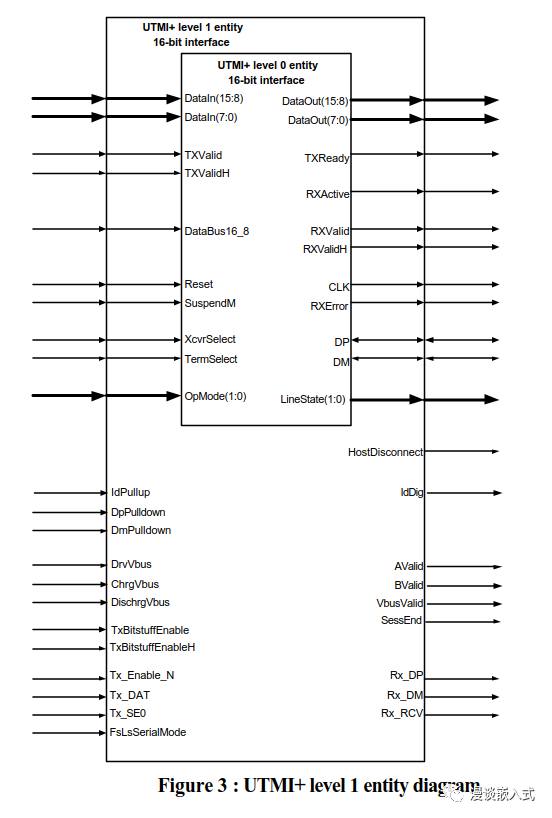

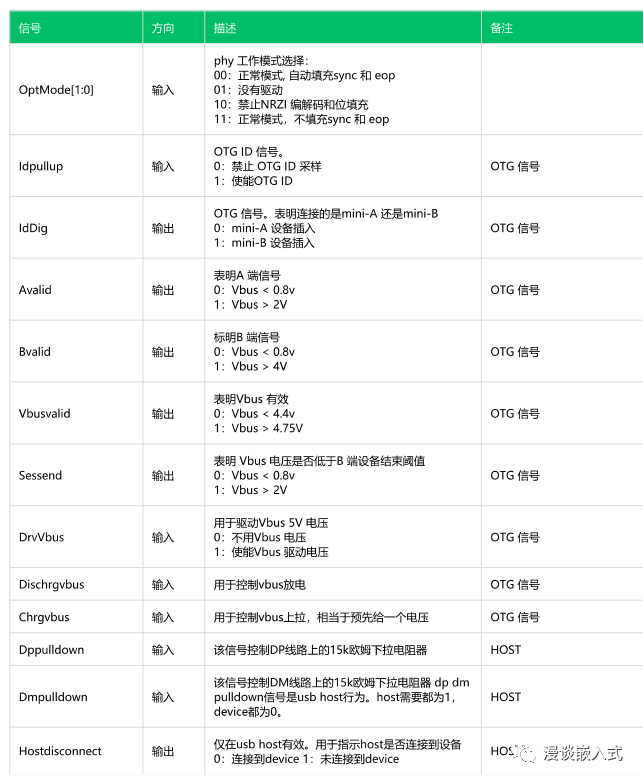

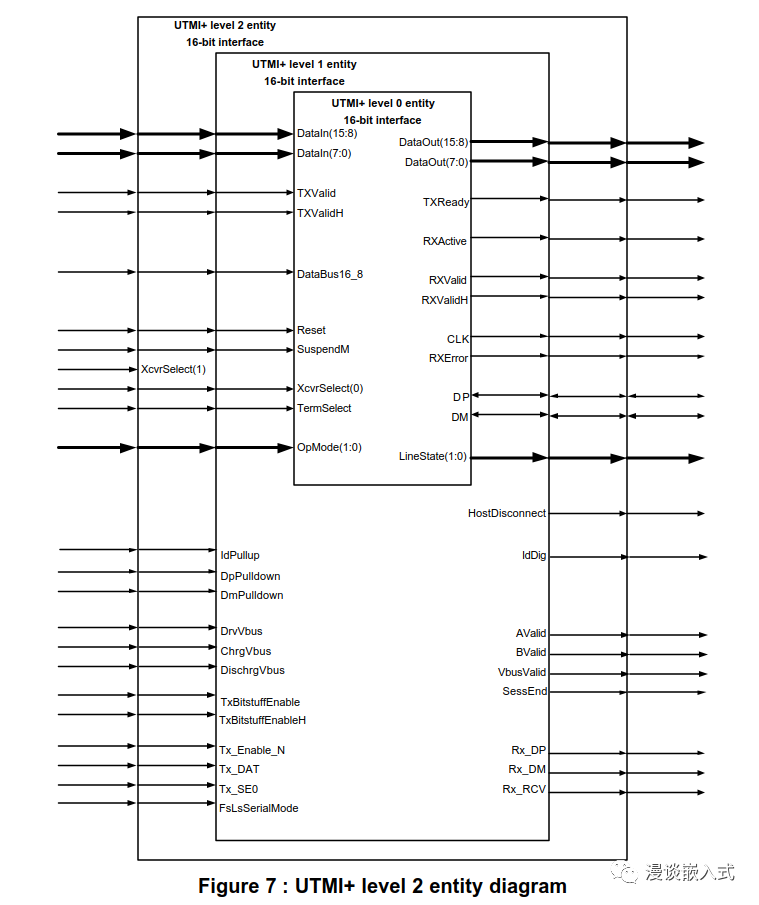

UTMI+ level1 规范相对于 level0 多了对OTG 设备的支持。新增了一些OTG /HOST 相关的接口。

信号接口如下:

对于USB2.0, 我们大多数情况下,用得最多的就是level1。同时支持:

对于单纯的只需要device 的设备我们在芯片设计阶段可以考虑,选择level0 的接口phy。

当然无论level 几,都可以向前兼容的。关键是usb 控制器的输入信号给的是什么标准。

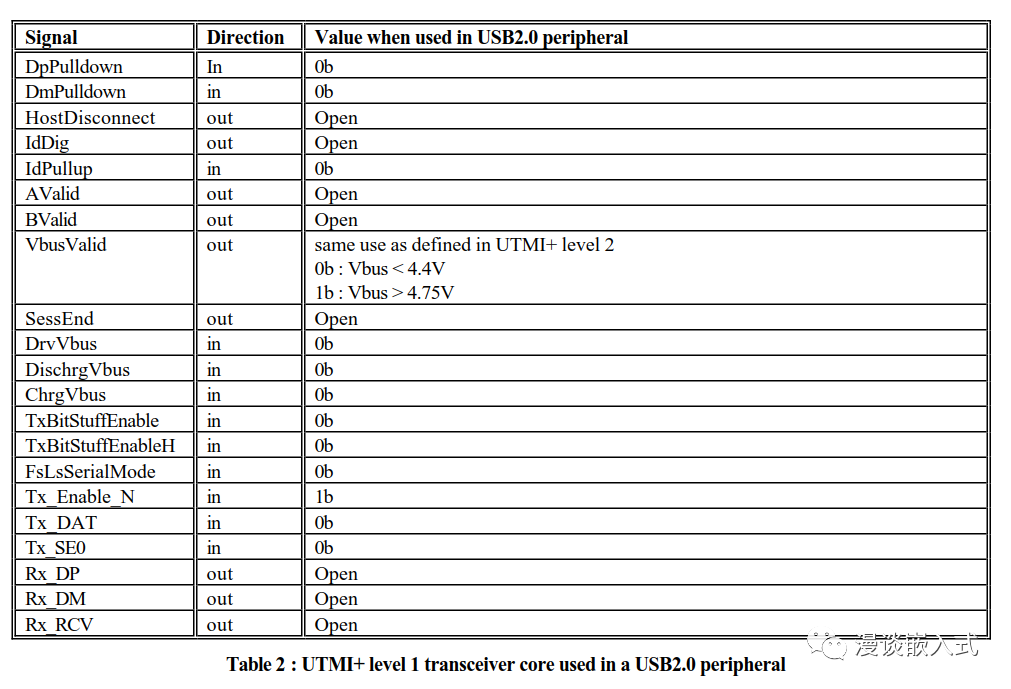

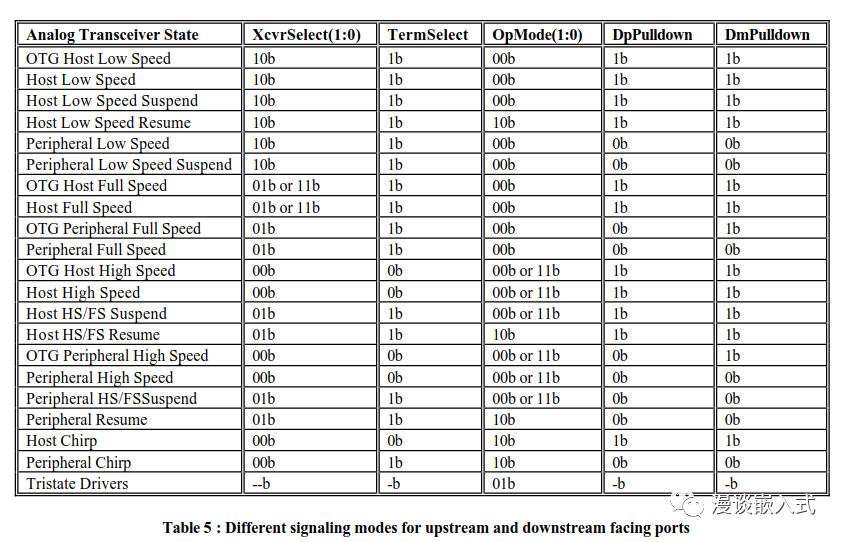

usb 2.0 设备 默认信号:

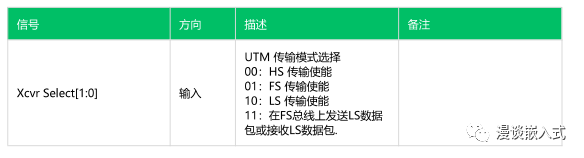

与UTMI+1相比,增加1bit的XcvrSelect信号来控制LS选择。另外需要注意linestate等信号在LS时也要表示不一样状态。

新增接口:

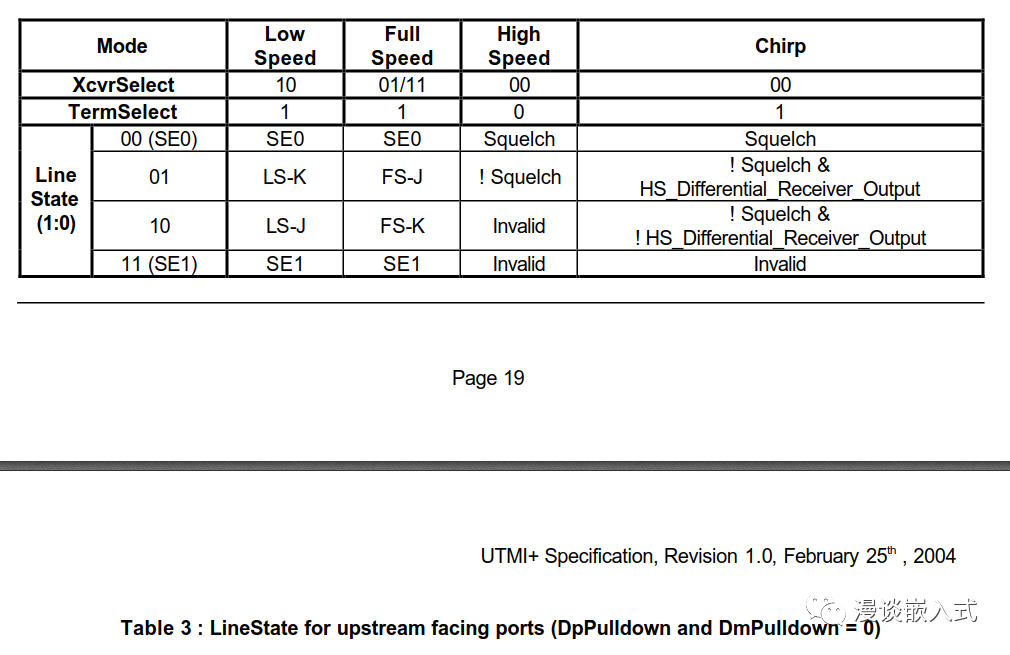

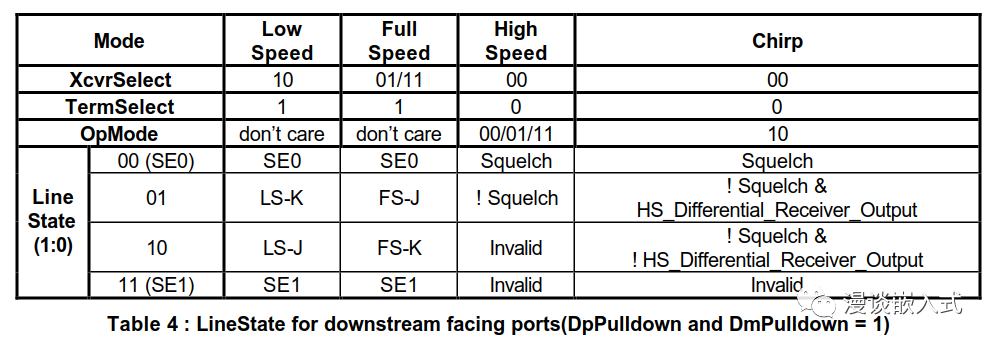

LineStare 状态:

在全速和低速模式下,lineState(0)总是反应DP,而lineState(1)总是反应DM。

下行端口lineState:设备端

上行端口lineState:host 端

修复一个前文错误:

下行端口(downstream):设备到主机行为。

上行端口(upstream):主机到设备行为

与UTMI+2相比,没有增加新的信号。只增加XcvrSelect=2'b11时的功能,该功能定义在UTMI+2中该位是保留的。

这是对level2的进一步增强。在这个级别中,处理必须通过FS集线器从主机发送到LS设备的LS流量是可行的。

在level2中,如果使用并行接口,USB On-the-Go DRD的主机控制器部分只能与直接连接到主机的LS设备进行通信。

如果XcrvSelect是11b,则收发器将在发送LS分组之前在FS处发送 preamble packet。在接收模式下,它将等待在LS收发器启用的情况下接收LS数据包。收发器必须使用FS令牌(快速上升和下降时间以及相反的极性)发送所有数据(FS preamble packet和LS数据)。注意,此时的令牌为特殊令牌PRE(有关PRE,本文不做介绍)。

一句话总结:level2 只能直接和LS 设备通信, level3 可以通过hub 外接LS 设备。

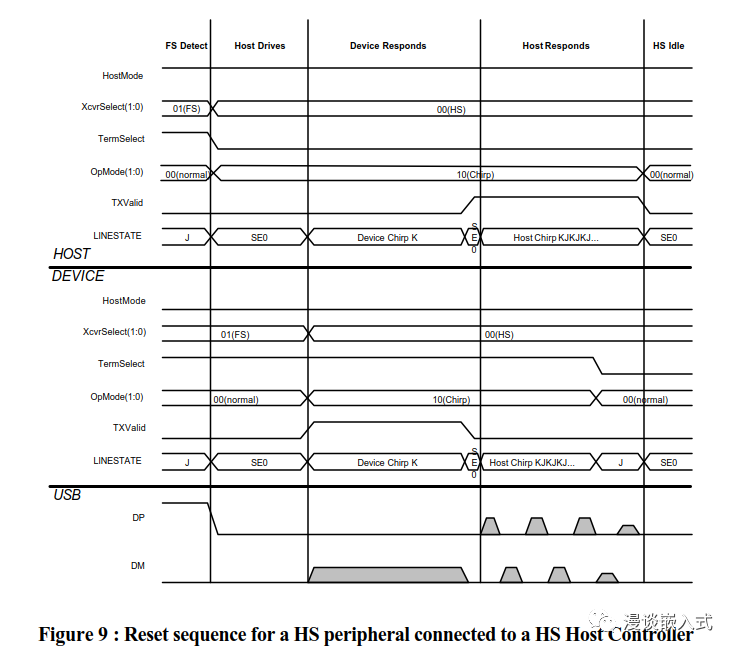

对于高速设备连接到整个usb host 整个时序如图所示:

通常我们关注最多的就是 USB 设备端的这段信号(DP/DM)。对于XcverSelect optmode linestate 等信号,一般对软件层面是隐藏的。一旦这些信号有问题。说明IC 设计有问题,比如信号连接不对,比如控制器输出的信号有问题 。

本文主要介绍了UTMI 及 UTMI+ 接口规范。详细对比了level0/level1/levle2/level3 。对于初学者而言,可以先以level0 为基准学习,后续再逐步深入到其他规范。

本文档适用于哪些人员:IC 设计人员、FPGA 验证人员、USB 底层深入学习人员。

参考文献:《usb2-transceiver-macrocell-interface-specification.pdf》、《TMI-PLUS-SPECIFICATION.pdf》

需要pdf 的 后台回复【UTMI】获取