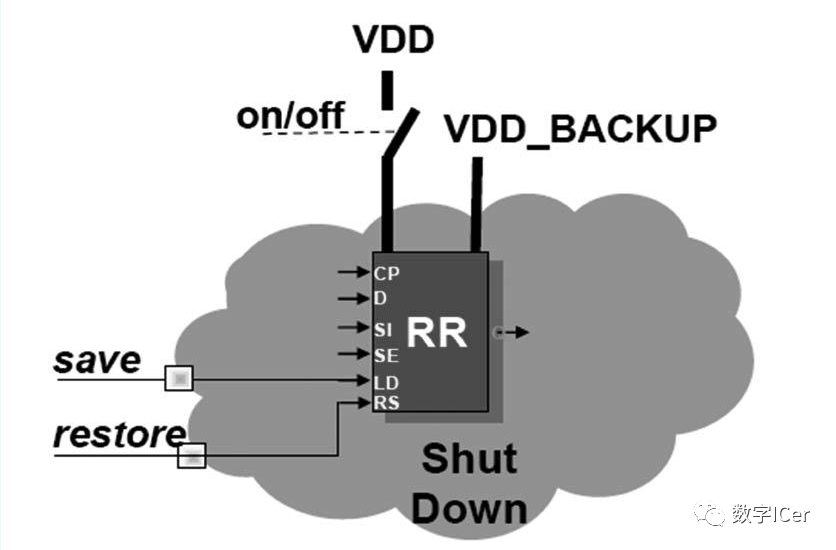

在电源关断模块有可能要求register对关断前的数据进行锁存或者在电源打开后要求对锁存的数据进行恢复,这就需要特殊的单元Retention Register。

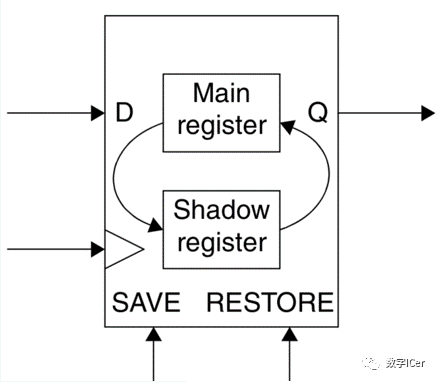

retention reg有两组寄存器,Main Register和shadow寄存器,其中shadow寄存器使用的是always on的电源;

它有两个电源,一个用于模块电源未关断时的工作用电,一个用于模块电源关断时的用电。它还有两个控制信号save和restore,用于控制是否锁存数据或者恢复数据;

如上图所示,这个寄存器需要有两个电源,一个是常开的VDD_BACKUP,给shadow寄存器用,另一个是可以关断的VDD,给Main Register用。

在需要保留状态时,使能SAVE信号,Main Register的值就被保留到shadow寄存器中,然后即使VDD关闭了,shadow寄存器的值也会保留。当模块/IP再次上电,通过使能RESTORE信号,就可以把shadow寄存器的值写回Main Register中;

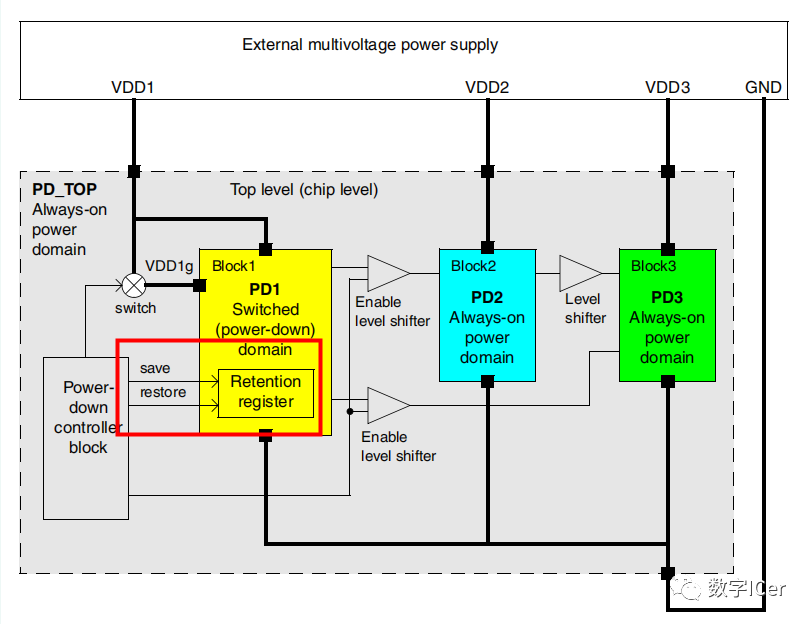

对于可以关断的Power Domain,如下图Block1内的PD1,在关断电源之后,内部数据全部丢失,如果想在断电后仍然保存这些数据有几种方式:

与前面的各种低功耗Cell一样,Retention Register内部的Shadow Register也是Always On Cell,必须有Always On的供电源。Shadow Register连接到always-on电源上以保证其能够正常工作。由于是Always On的,所以为了实现低功耗的目标,内部的器件多用高阈值的MOS管来实现以降低Power Down模式下的Leakage Power。

Retention Register内除了Shadow Register之外,其余的器件均使用可以关断的电源,为了高性能以及快速恢复数据,Main Register可能还会使用低阈值的管子。

Retention Register与常规的寄存器相比,面积更大,一般要比普通寄存器面积大约20%,如果设计的鲁棒性好一些,甚至会大超过50%。 但是与其他方案相比,上电后数据恢复的速度非常快,且操作也简单。因此,使用retention register需要特别注意它带来的额外的面积和功耗。当需要断电保存的数据过多时,retention cell带来的功耗可能会使整体的low power效果打折扣。

在低功耗设计中retention register,这个寄存器其实包含两个寄存器,一个叫shadow register的寄存器用always on电源,用于寄存器值的恢复,那么为什么不直接一个普通的寄存器用always on电源呢?这样不是可以省下一个寄存器吗?

理论上说可以用普通的register来做,但是实际中需要考虑ISO,仅仅clock,data,reset就需要3个isolation cell。功耗比较高,另外对timing也有影响。

而retention register内部就考虑了这些,只要保证进ret的信号是always on就可以,而且进出ret的速度都非常慢,所以对timing 不会有影响。

retention registers指的是什么寄存器?它与一般的寄存器有什么不同,主要的功能是什么?

retention reg有两组寄存器,其中一个是shadow寄存器使用的是always on的电源。当power down之前,把主reg的值load到shadow reg,当power up之后,从shadow reg把值load到主reg。因为shadow寄存器只是用来存储数据,所以可以做得比较小,功耗比较低。

使用retention registers会增加额外的leakage,需要配合系统的省电方案使用,同时也会增加额外的面积;

retention registers看起来多了一个shadow寄存器,似乎费电更多才是,那怎么做到省电的呢?

关键就在于,retention registers中的shadow寄存器只消耗很少的电来保存信息,从而使得主寄存器可以完全掉电,从而省电;

retention registers中主从寄存器两者的区别?

主寄存器面积大,工作电压高,采用的晶体管阈值电压也低,工作电流大,这样可以保证该寄存器在正常工作时速度快,负载能力强。

从shadow寄存器,面积相对小一些,采用阈值电压高的晶体管,其驱动电压也会更低。因此,消耗的电量很少。

retention registers的lib描述指定了控制数据保存和恢复的电源引脚和输入信号。

指定了哪些电源引脚是正常的并且可以掉电,哪些是用于在掉电期间保持数据的常开引脚。

cell(RETENTION_DFF) {

retention_cell:"ret_dff";

area : 1.0;

...

pg_pin(VDDB) {

voltage_name : VDDB;

pg_type : backup_power;

}

...

pin(RETN) {

direction : input;

capacitance : 1.0;

nextstate_type : data ;

related_power_pin :VDDB;

related_ground_pin:VSSG;

retention_pin (save_restore, "1" );

}

pin(Q) {

power_down_function:"!VDD+VSS";

related_power_pin : VDD ;

related_ground_pin : VSS;

direction : output;

...