天分享英飞凌和意法半导体针对新一代面向域控架构的高性能MCU分析:

Aurix 第三代TC4X和Stellar G(本文简称Stellar)

本文目录:

TC4X和Stellar G概览

内核和存储单元

安全性

通信外设

虚拟机支持

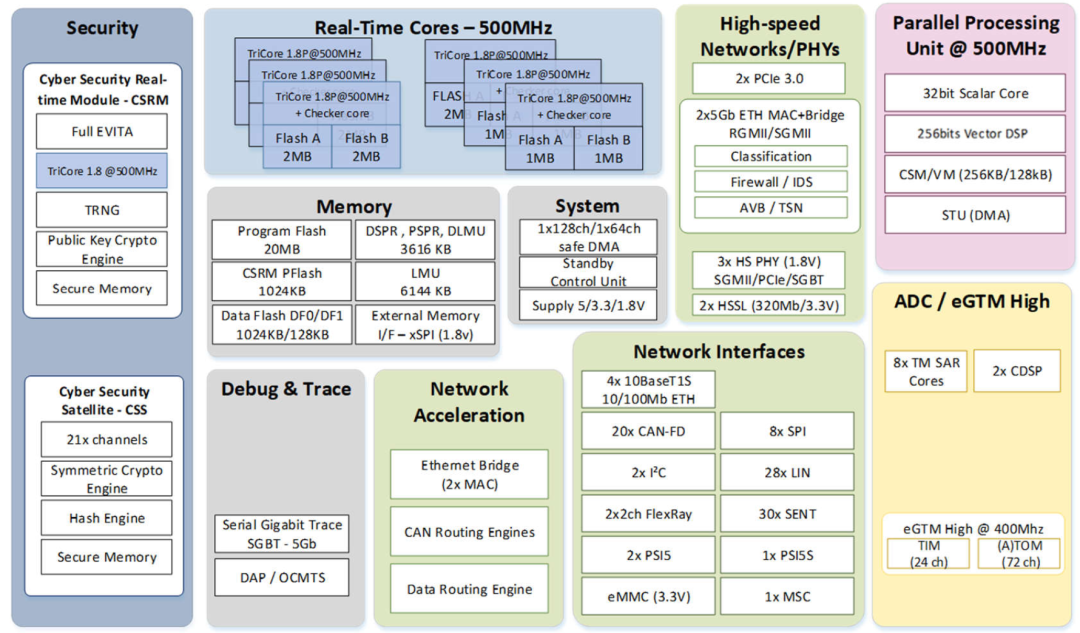

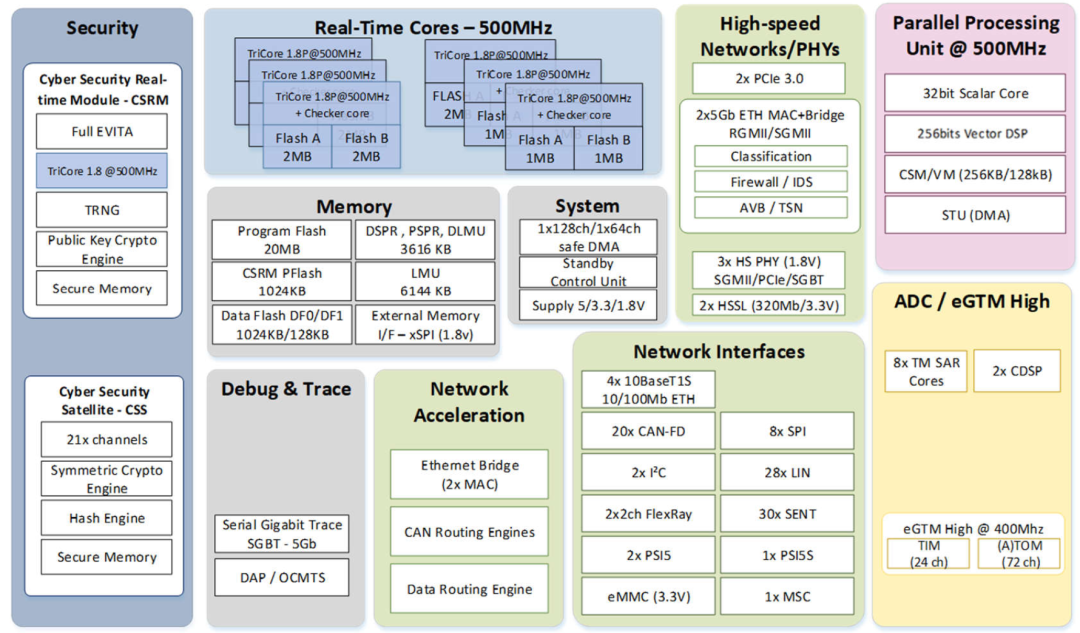

时间维度,TC4X和Stellar系列的启动时间应该相差不大,预计是2017~2018年之间;TC4X采用了22nm工艺,Stellar基于28nm工艺,均定位在下一代汽车E/E架构中域控制器的主控MCU核心是:更高的算力,更高的安全,更丰富的资源,更快的通信外设; TC4X框图

TC4X框图 Stellar G系列框图

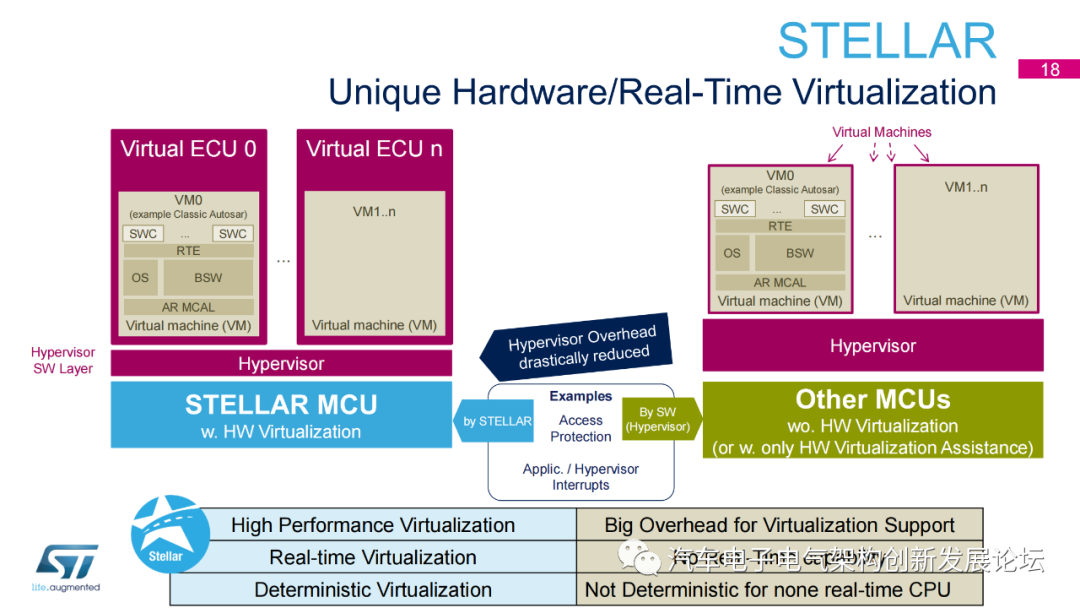

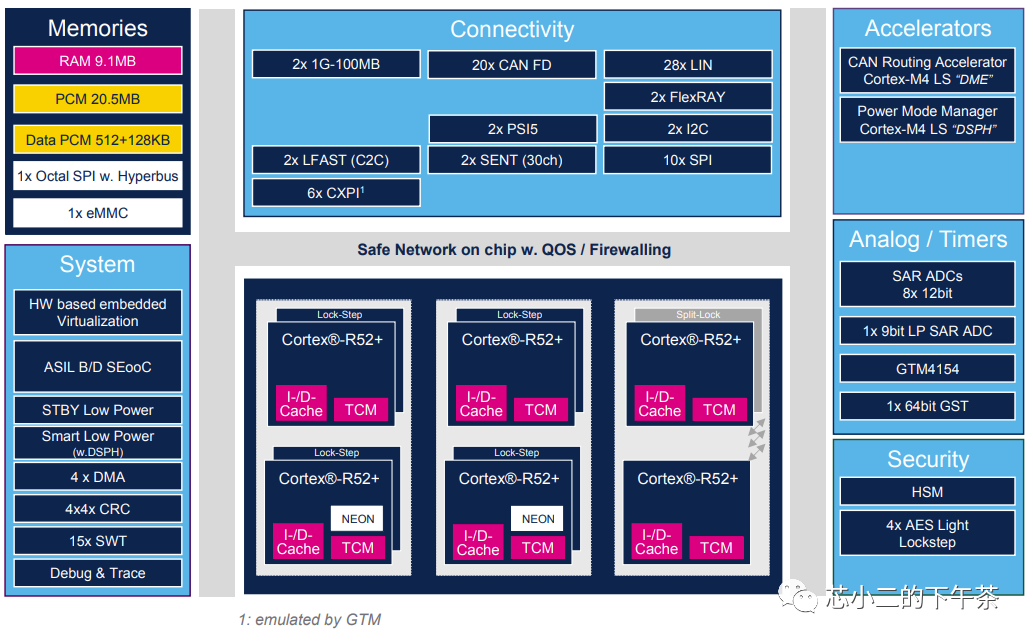

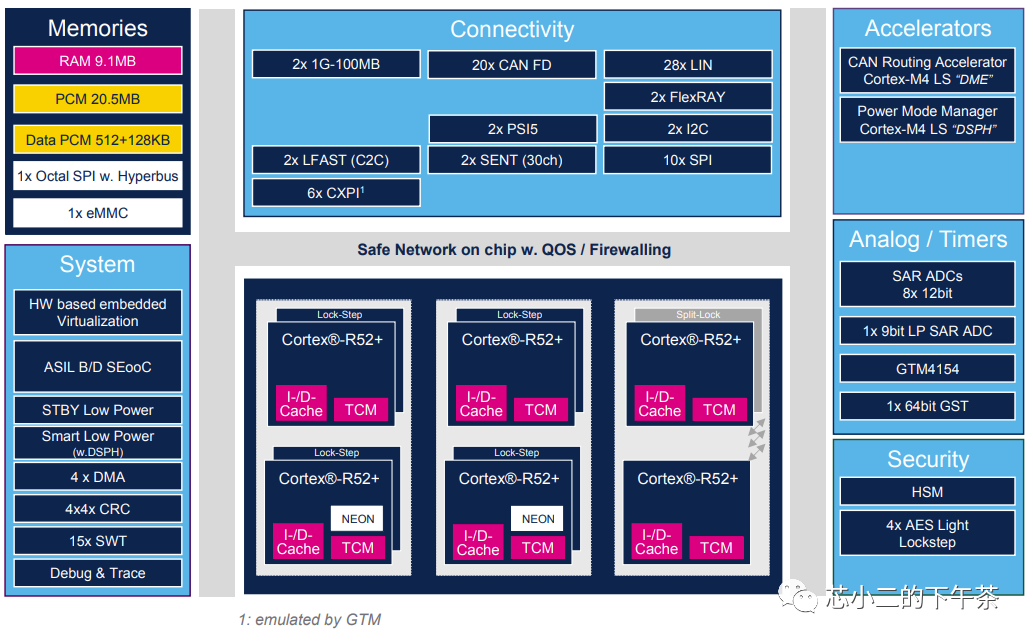

Stellar G系列框图

TC4X沿用了其自研的TriCore CPU内核,采用了更新的1.8版本,基于22nm工艺的主频在500MHz,最高支持6个内核,由TriCore可实现的算力达到了8000DMIPSStellar采用了ARM当前主流的Cortex-R52+内核,基于28nm工艺的主频,预计主频在400MHz,最高也是6个内核TC4X的HSM内的核用的也是TriCore 1.8 (TC3X用的是Cortex-M3),Stellar没有说明,可能是Cortex-M4F也可能是Cortex-R52TC4X最高20MB PFlash,1024+128KB DFlash,3166+6144KB的SRAM,支持外扩xSPI的FlashStellar内置20.5 PCM Flash(1MB For HSM),640KB DFlash (128KB For HSM),9280KB SRAM;TC4X和Stellar均支持2个BANK,可同时读写的Flash,方便满足未来汽车OTA的需求为了实现计算加速,TC4X内置了一个PPU(基于Scalar Core,支持向量运算),Stellar则增加了2个Cortex-M4F的内核,用于数据加速传输及预处理 (不是一个目的的加速,TC4X是为了AI,Stellar则是为了提升数据处理效率)

TC4X和Stellar均可支持功能安全ASIL-D级别,支持HSM Evita Full,支持MPU进行存储访问权限的配置TC4X每个外设通道都有访问保护(Access Protection),其实现的原理是给每个SRI总线master分配一个master tag ID, 每个外设通道都可以设置允许哪些master可以访问该通道。TC4X在通信外设方面,支持2个5Gbps的以太网+4个10/100MHz的以太网;另外,为了加速外设之间的数据吞吐,TC4X 增加了CRE/DRE,CAN到Ethernet的转发延时最少可以到15us,CAN到CAN的转发延时最少可以到5usStellar通信外设方面,支持2路10/100/1000Mhz Ethernet;

| TC4X

| Stellar |

FlexRAY

| 2 | 2

|

CAN-FD

| 20

| 20

|

LIN

| 28

| 28(UART复用)

|

| SPI | 8

| 10

|

UART

| 28(推测)

| 28 (LIN复用)

|

I2C

| 2 | 2

|

PSI(PSI5)

| 2+1

| 2x2

|

MSC

| 1

| N/A

|

SENT

| 30

| 2x15 |

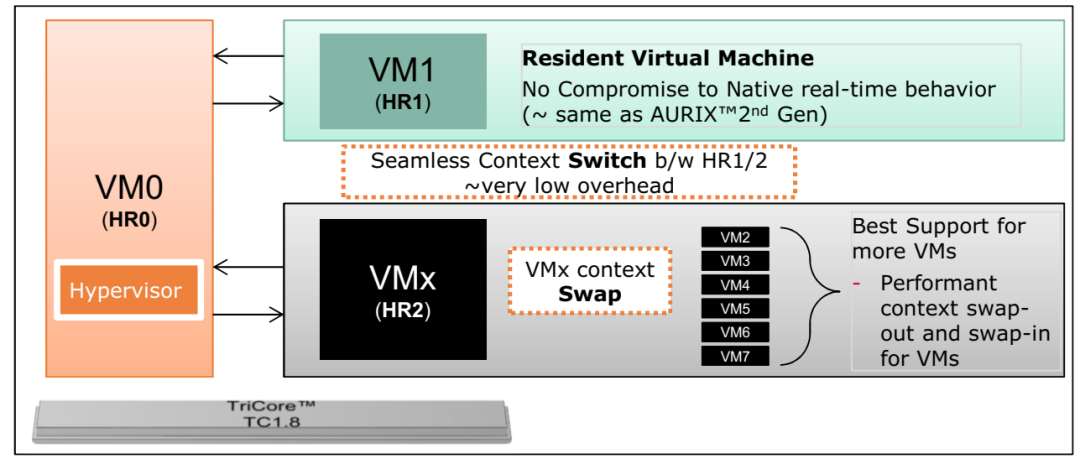

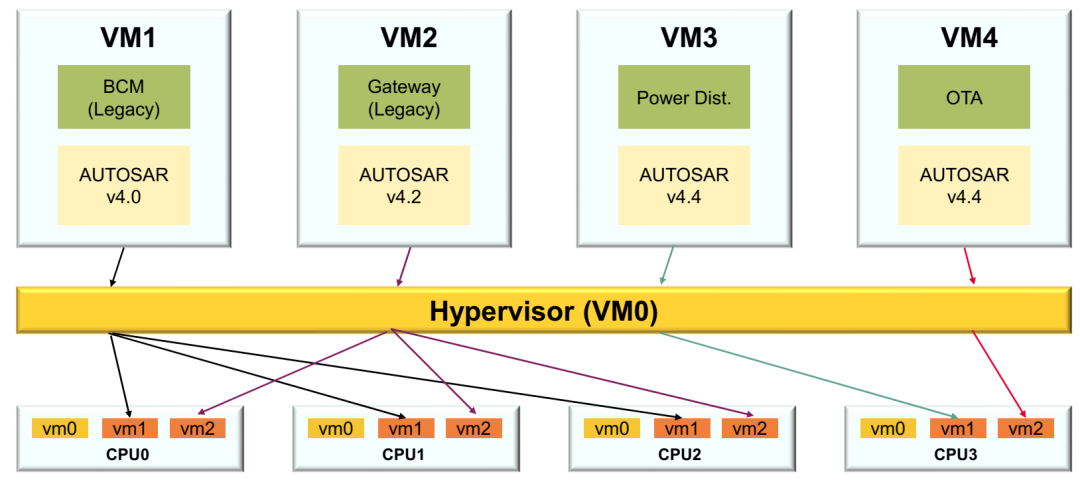

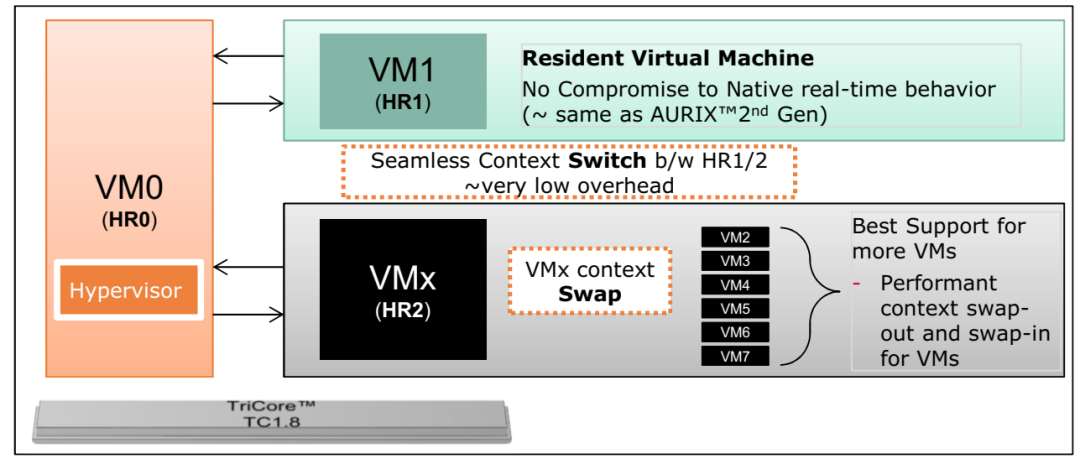

TC4X和Stellar均支持虚拟机和HypervisorHypervisor是一个中间软件层,用于在虚拟机之间划分处理、内存和通信资源,并将同时运行的虚拟机调度和迁移到不同的资源上。

虚拟化的一个主要用途是整合需要不同操作系统,以及相同操作系统的不同版本的ECU功能。

TC4X Hypervisor

TC4X Hypervisor

因为每篇文章会有涉及到内容引用,部分内容不知来源,如果发现有侵权,请后台告知感谢;

6月10日的侯哥新书发布会,有兴趣的朋友可以收看!

TC4X框图

TC4X框图 Stellar G系列框图

Stellar G系列框图

TC4X Hypervisor

TC4X Hypervisor