公众号:高速先生

B站:一博科技(短视频分享技术干货)

作者:黄刚

原理图上看似轻描淡写,PCB设计加班到半夜。随着信号速率越来越高,原理图的内容在PCB设计上去实现变得越来越难,图纸上任意的一根理想连线或者器件到了PCB工程师这里可能也无从下手。不信?那就接着往下看呗!

随着速率越来越高,原理图上的一根连接线在PCB设计上就包括了阻抗匹配,长度约束,加工偏差,板材选型,等长设计,过孔设计等内容。那么广大硬件工程师可能会不服气了:那就不说线,说下元器件,这一块是我们的强项了吧!我们在器件选型上也花了很多时间,而且也要很熟悉硬件原理的,然后你们在PCB上把封装建出来然后放到PCB板就可以了嘛。乍一听,好像硬件工程师们扳回一局了,但是高速先生依然要和你们“争执”下去,我们要说的是,即使是一个简单的电容,其实在PCB设计也是很有学问的哦,你们确定了解吗?

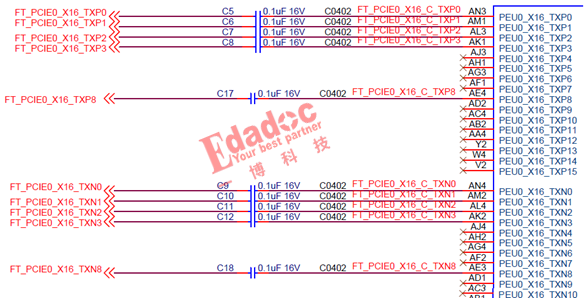

今天我们来讲一下高速串行信号中非常常见的AC耦合电容。对!就是下面原理图里面的这个玩意。我们今天就来研究一下它对高速信号的影响。

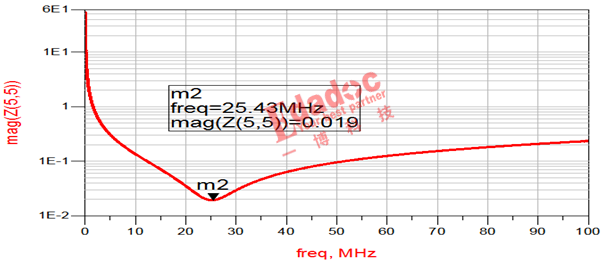

作为一个电容,可能更多的粉丝会在电源网络中见到过它们。一般来说,电容用在电源网络中起到去耦的作用,也就是抑制高频噪声的作用。一般来说,我们加入了不同容值的电容,就能够起到降低某些频段的PDN阻抗的作用。如下所示,我们加入了一个在高速链路中常有的0.1uF电容,也能够压低10M到25MHz频段的阻抗。为什么是这个频段,为什么不能压掉全频段的阻抗,这个高速先生也提过很多次了,今天它不是主角,就不再重复了。

那么如果同样的电容放在了高速串行链路中后,它对高速信号的性能有什么影响呢?为了公平起见,我们还是从原理上和PCB设计这两点去分析哈。

首先从原理上而言,当然大家都知道AC耦合电容是用于隔直流,也就是把共模信号隔掉。从这一点来看,貌似就是一个很简单的原理。但是我们需要知道,电容本身其实就不是理想的东西,即使它不焊接到PCB上面去,它也是由下面的等效参数来组成一个电容,我们把这些参数叫做电容的寄生参数。

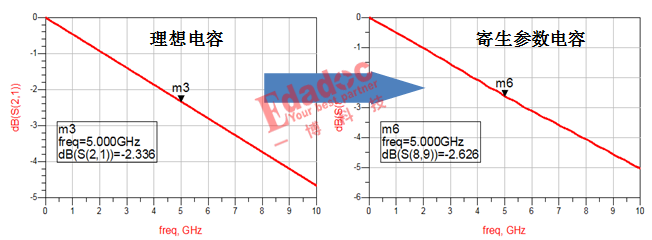

所以从仿真中就能看到,一段若干长度的传输线加上一个0402的电容的情况下,电容本身带入的寄生参数会增加一定的损耗。

其实这个时候大家就会惊讶的发现,同样的0.1uF电容,如果采用不同的封装大小时,结果肯定会有所不同。

因为封装越大的电容,它本身的寄生参数也就越大,因此寄生电感带来的损耗会更大。所以单从这个器件选型的角度看,选择封装越小的电容影响也是越小的。

另外扩展一下哈,对于如何去查看PCB走线的寄生电感,寄生电容等设计小技巧,可以去观看高速先生队长亲自拍摄的视频。

当然从上面的内容看,从0201到0603的电容选型,仿佛觉得对损耗的影响也不是很大嘛,再说如果选择0201的话,其实基本就没有影响了呗。恩!这个观点高速先生其实勉强算同意吧,那么我们再来看看如果把这个电容加到PCB板上之后会怎么样呢?

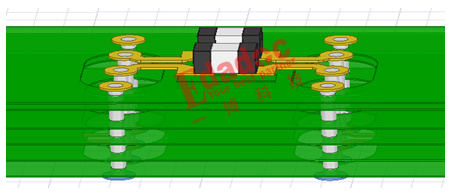

高速先生大概做了一个3D的模型,可以用来分析下一个0402的电容放在PCB焊盘上到底对信号质量有什么影响。

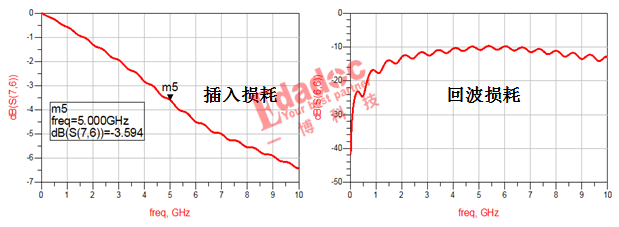

这个时候你们就会发现,影响到信号性能的因素就不仅仅是电容本身的寄生参数了,反而是变成了如何去优化电容体+焊盘的阻抗了。阻抗如果不匹配的话,它对回波损耗和插入损耗的因素是非常大的。有多大呢?高速先生列出我们仿真的数据如下,一个未经过仿真优化的电容结构带来的插入损耗和回波损耗的结果如下:

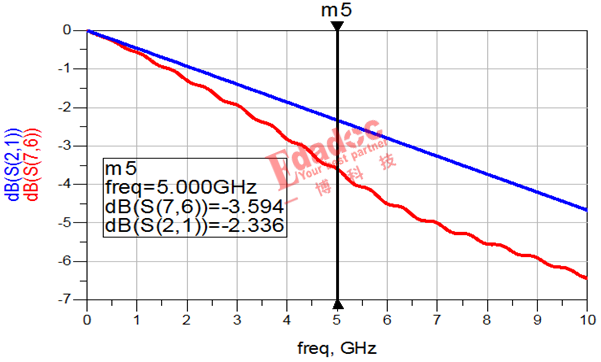

这个时候我们再来对比下理想的电容和放到PCB上未优化的电容对于损耗的对比。

这个时候你们就能明显看到差别了吧。这其实也说明了仿真对电容优化的重要性,电容绝不只是摆到PCB焊盘上面就OK了哈。

当然时间关系,其实还有很多关于电容在PCB上要注意的点来不及说哈,例如不同封装大小的电容的优化方向,电容在高速链路中不同位置的区别等等,有机会高速先生再和大家一起分享吧!

— end —

本期提问

关于电容在高速串行链路的位置,你们会把它摆在哪里呢,原因是什么?

高速先生精选

觉得内容还不错的话,点个“在看”呗