本文来自“PCI Express一致性测试方法”,PCI EXPRESS 技术简介、N5393C一致性测试软件操作方法、SigTest软件测试方法、电缆校准和De-Skew的方法。1、PCI Express一致性测试方法

2、5G IC高速接口设计与测试挑战

3、MIPI D-PHY一致性测试方法

4、MIPI C-PHY一致性测试方法

5、HDMI 1.4_2.0物理层一致性测试方法7、DDR一致性测试方法

8、DDR技术演进与测量挑战

9、SATA一致性测试原理与方法

10、USB2.0/USB3.1一致性测试方法

11、高速数字接口测量的去嵌入和均衡软件使用方法1、PCI Express 3.0 and 4.0测试挑战

2、PCI Express一致性测试方法1、USB 2.0一致性测试方法

2、USB2.0/USB3.1一致性测试方法

3、USB 3.1 Gen2 10G -Gen1 5G Receiver测试《56份GPU技术及白皮书汇总》

《集成电路及芯片知识汇总(1)》

多模态AI研究框架(2023)

大模型算力需求驱动AI服务器行业高景气(2023)

“机器人+” 系列:机器人研究框架(2023)

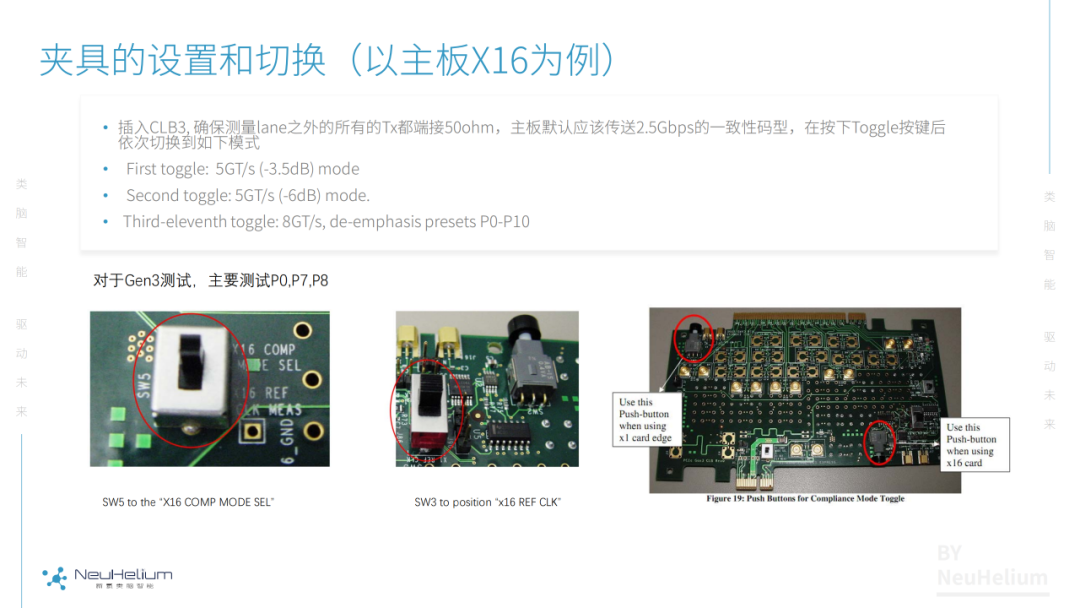

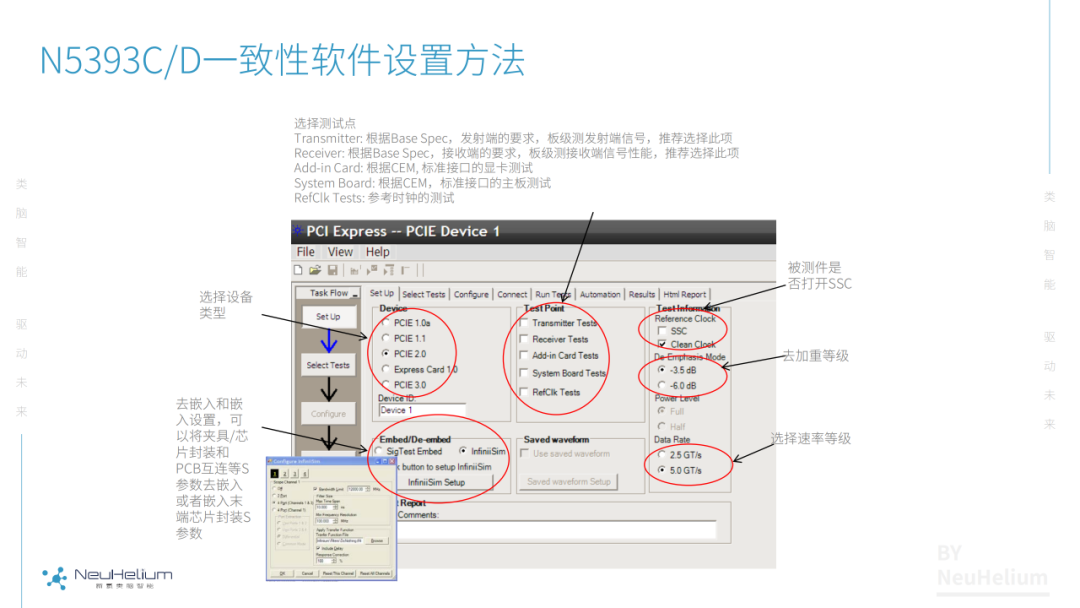

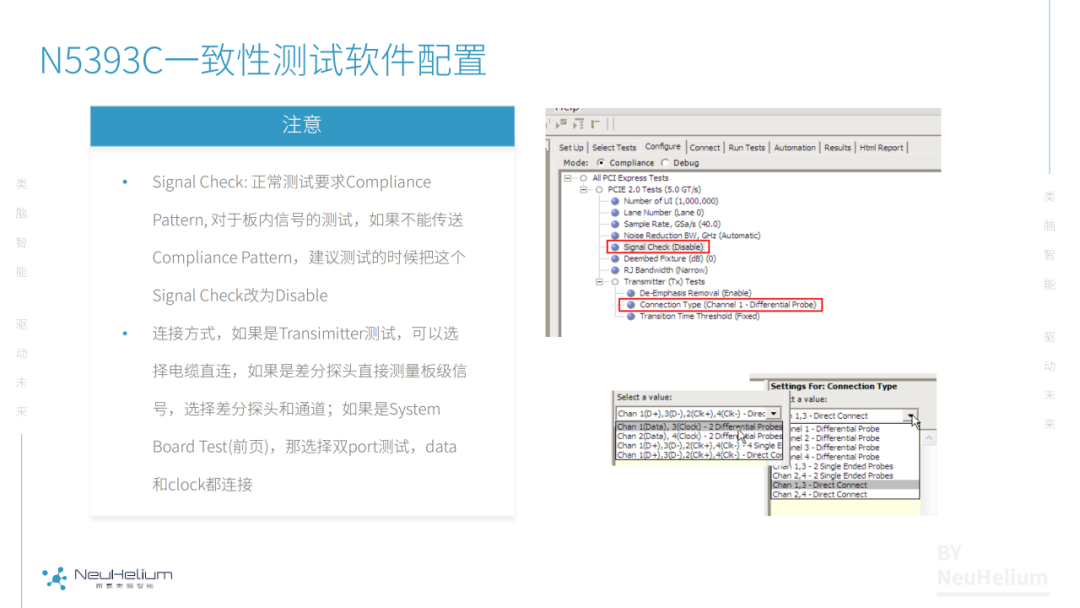

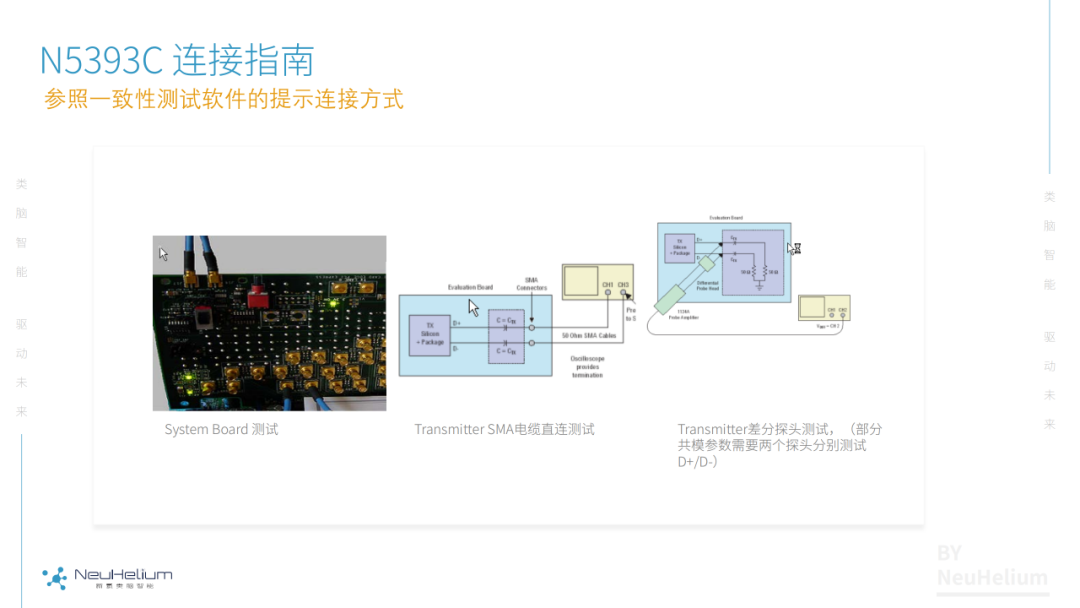

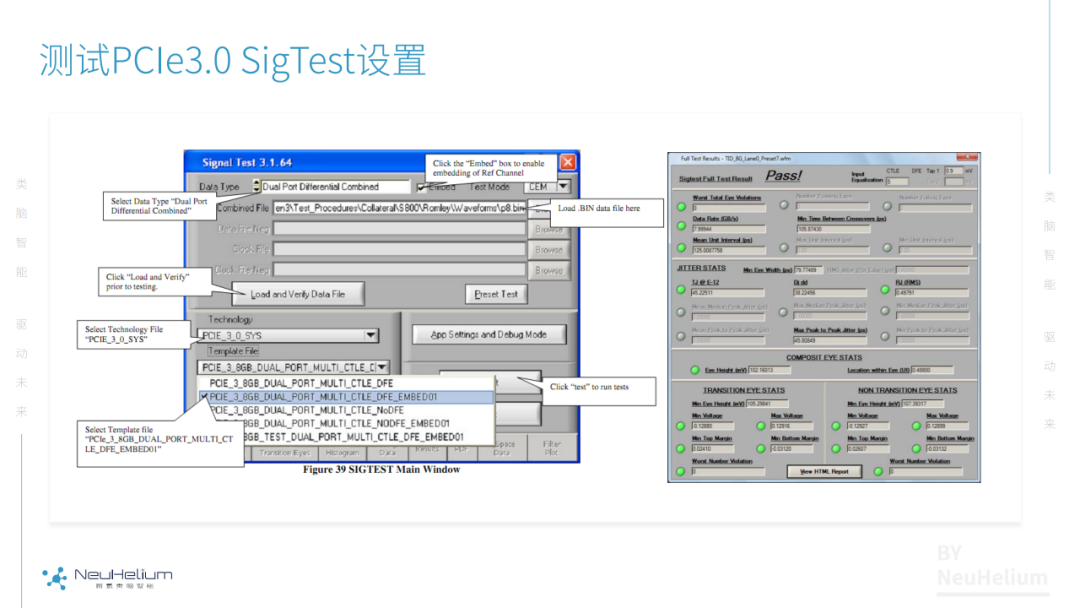

PCI Express 标准是由 PCI-SIG 组织制定,是一种点到点的串行差分结构,规范最新发展到4.0标准,总线速率为16GT/s,3.0/2.0/1.1标准的总线速率分别为8Gbps,5Gbpss和2.5Gbps。PCI Express规范包括Base Specification 和CEM(Card Electromechanical Specification),前者定义了芯片的电气参数及其规范,后者定义了包含卡接口和互联的系统级规范。对于芯片的验证及没有标准PCI Express接口,通常参考Base Spec对Tx端或Rx端的电气特性要求进行测量;对于系统级的测试比如有标准的PCI Express接口的主板和显卡,主要遵循CEM标准。1、PCI Express一致性测试方法

2、5G IC高速接口设计与测试挑战

3、MIPI D-PHY一致性测试方法

4、MIPI C-PHY一致性测试方法

5、HDMI 1.4_2.0物理层一致性测试方法7、DDR一致性测试方法

8、DDR技术演进与测量挑战

9、SATA一致性测试原理与方法

10、USB2.0/USB3.1一致性测试方法

11、高速数字接口测量的去嵌入和均衡软件使用方法1、PCI Express 3.0 and 4.0测试挑战

2、PCI Express一致性测试方法1、USB 2.0一致性测试方法

2、USB2.0/USB3.1一致性测试方法

3、USB 3.1 Gen2 10G -Gen1 5G Receiver测试9、芯片和芯片设计——集成电路设计科普

10、集成电路EDA设计概述

11、超大规模集成电路设计

12、常用半导体器件讲解

13、半导体制程简介

14、SOC芯片设计

15、ASIC芯片设计生产流程

16、CAN总线详细讲解1、集成电路技术简介

2、芯片设计实现介绍

3、集成电路芯片设计

4、芯片规划与设计

5、数字IC芯片设计

6、集成电路设计的现状与未来

7、集成电路基础知识

8、集成电路版图设计本号资料全部上传至知识星球,更多内容请登录智能计算芯知识(知识星球)星球下载全部资料。

免责申明:本号聚焦相关技术分享,内容观点不代表本号立场,可追溯内容均注明来源,发布文章若存在版权等问题,请留言联系删除,谢谢。

温馨提示:

请搜索“AI_Architect”或“扫码”关注公众号实时掌握深度技术分享,点击“阅读原文”获取更多原创技术干货。