大侠好,欢迎来到FPGA技术江湖。本系列将带来FPGA的系统性学习,从最基本的数字电路基础开始,最详细操作步骤,最直白的言语描述,手把手的“傻瓜式”讲解,让电子、信息、通信类专业学生、初入职场小白及打算进阶提升的职业开发者都可以有系统性学习的机会。

系统性的掌握技术开发以及相关要求,对个人就业以及职业发展都有着潜在的帮助,希望对大家有所帮助。本次带来Vivado系列,锁相环使用教程。话不多说,上货。

锁相环使用教程

作者:李西锐 校对:陆辉

锁相环是我们比较常用的IP核之一。PLL的英文全称是Phase locked loop即锁相环,是一种反馈电路。具有分频、倍频、相位偏移和占空比可调的功能。在XILINX 7系列芯片中时钟资源包含了时钟管理单元CMT,每一个CMT都是由一个MMCM和一个PLL组成。对于使用者来说,当我们实现简单的分频时,设计者可以通过写代码的方式来进行分频,但是对于复杂的设计,比如倍频、相位偏移等设计时,写代码的方式就显得力不从心。此时就体现了学习锁相环的必要性。接下来我们一起了解一下锁相环的使用。

PLL锁相环由以下几部分组成:前置分频计数器、相位频率检测器电路、电荷泵、环路滤波器、压控振荡器、反馈乘法器计数器和后置分频计数器。在工作室,相位频率检测器检测其参考频率和反馈信号之间的相位差和频率差,控制电荷泵和环路滤波器将相位差转换为控制电压,压控振荡器根据不同的控制电压产生不同的振荡频率从而影响反馈信号的相位和频率。在参考频率和反馈信号具有相同的频率和相位后,就认为PLL处于锁相的状态。

本次实验我们将输出四个不同的频率波形,其中有两个相位相差180°。其中四个频率分别为100MHZ,30MHZ,10MHZ,10MHZ_180。

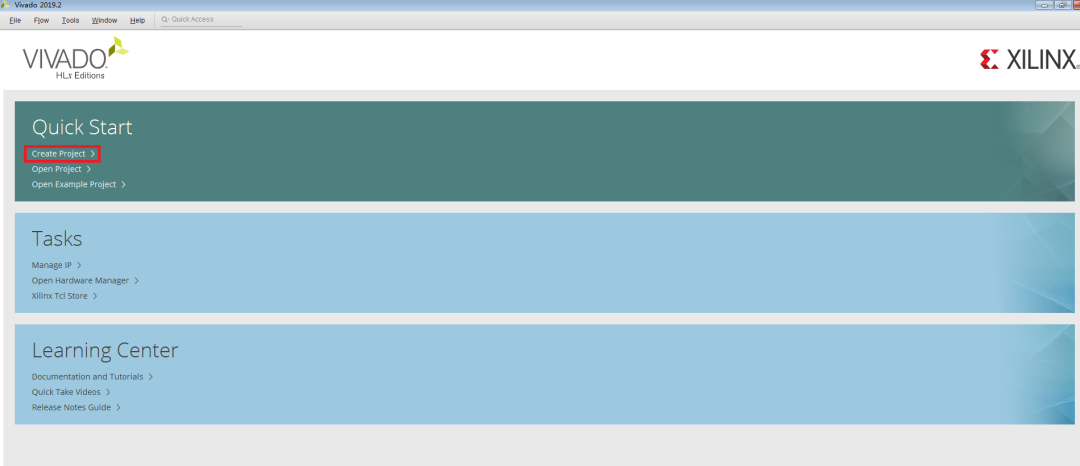

接下来我们首先先新建一个工程:

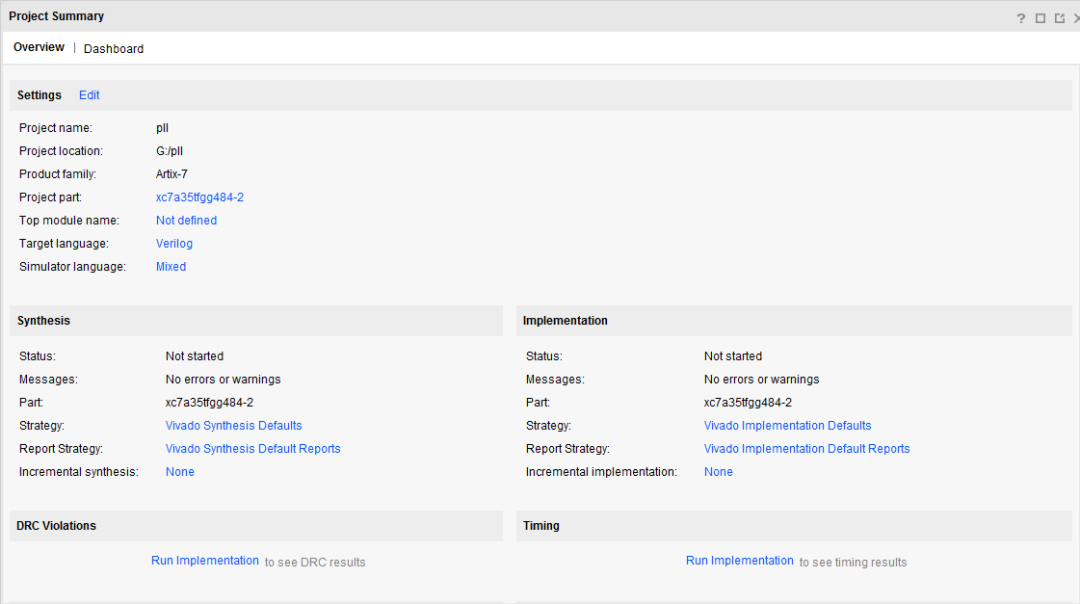

首先选择新建工程,在此之前,新建工程的介绍已经给大家详细介绍过了,在此就不在重复介绍,新建好之后,如下图:

大家可以在工程总览中看到工程的信息。

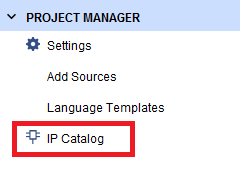

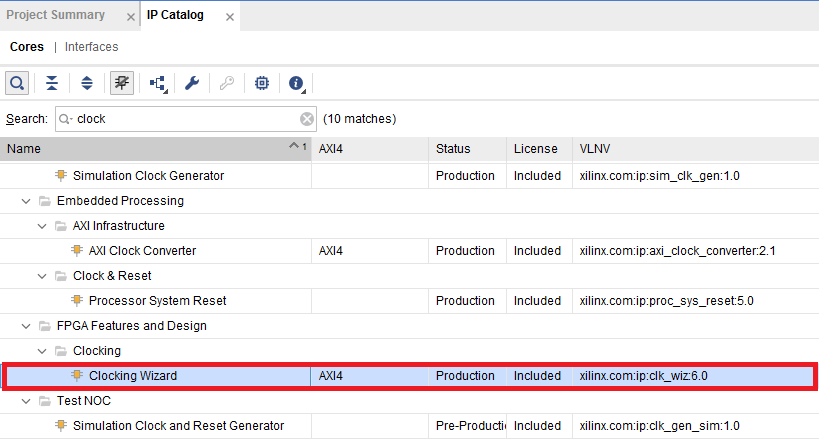

我们在左侧菜单栏里面选中IP Catalog

打开之后搜索clock,如下图:

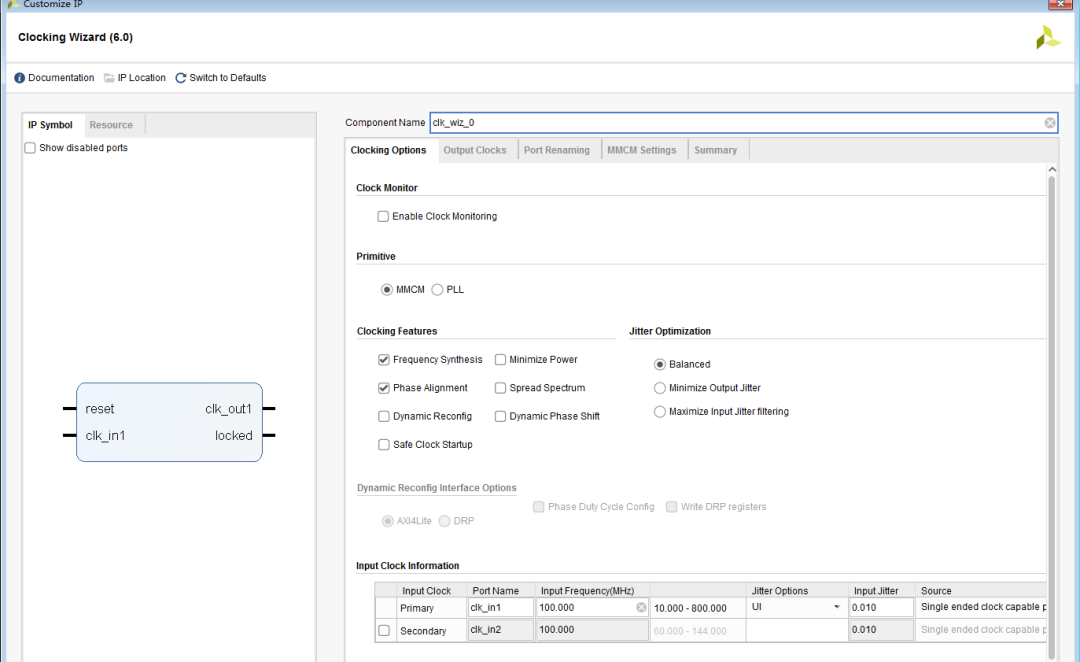

双击打开此选项,弹出如图界面:

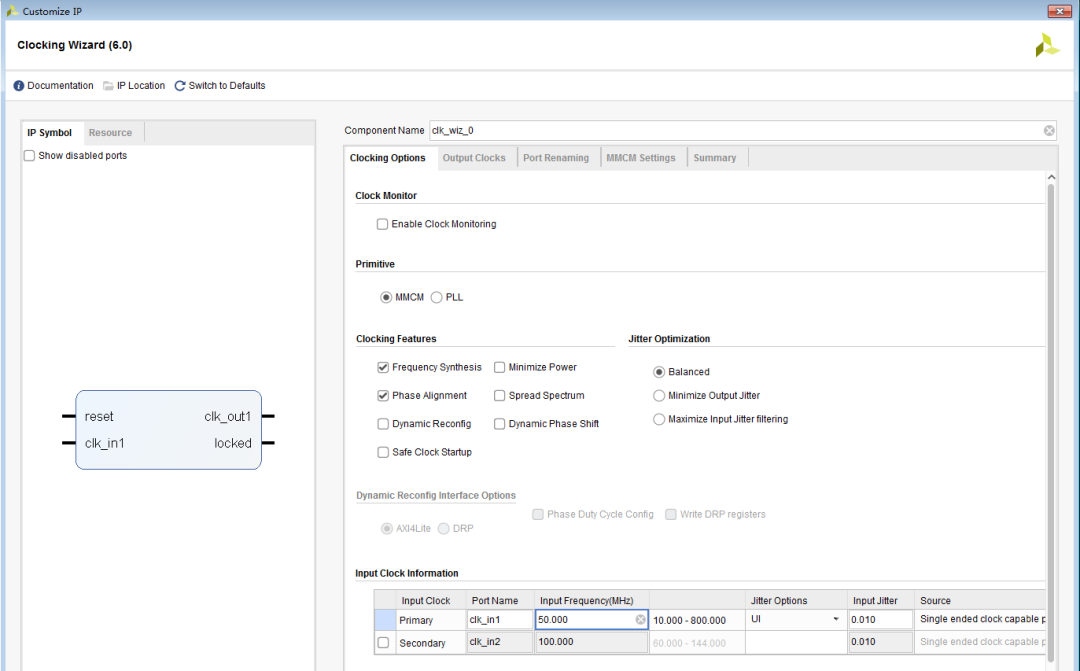

我们需要在此界面做一些配置,IP核的名字我们可以修改,但是要符合起名字的规则,当然也可以不做修改。在时钟特征里面,我们保持默认选项即可。输入时钟我们需要修改,我们开发板的晶振是50MHz,所以此处频率我们改为50MHz。

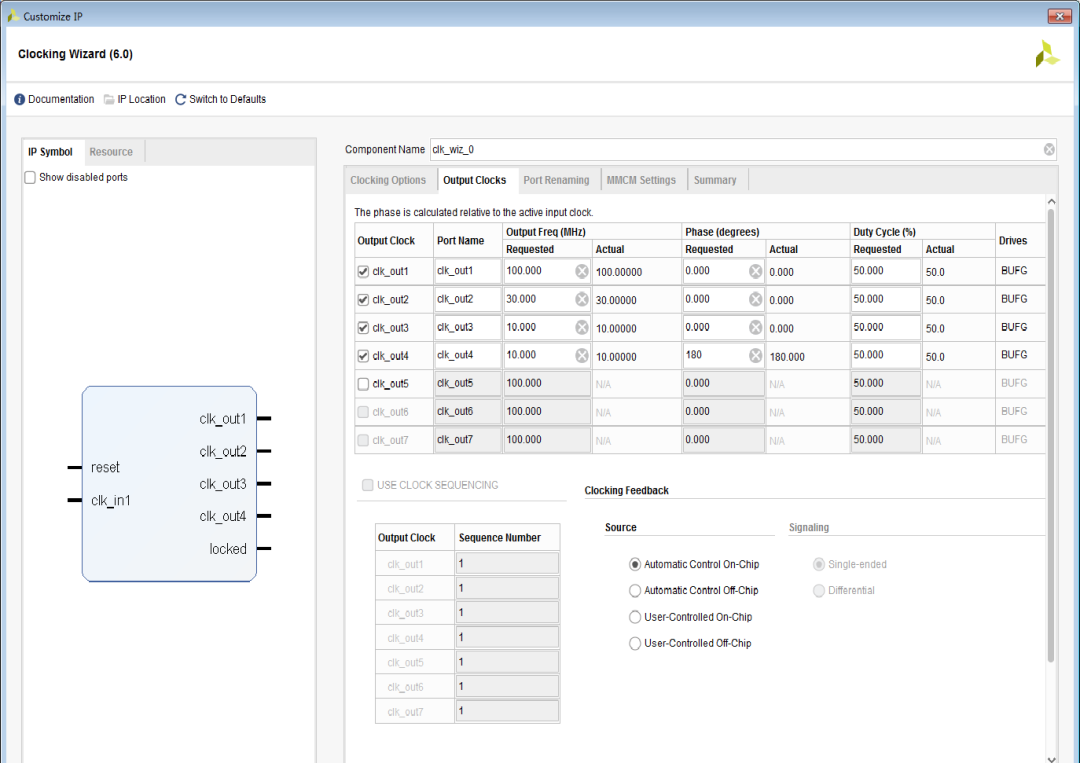

输入时钟设置好之后,我们设置第二个配置界面。按照我们提前规定好的输出频率去设置。

需要添加额外的时钟的时候,在对应的选项前面勾选上,设置好对应的输出。clk_out4是10MHz偏移180度的波形,所以在相位偏移选项里面设置成180度。

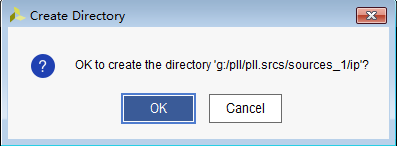

其他界面没有需要设置的内容,我们直接点击OK即可。然后会弹出提示框。这个提示框是确认是否给IP核新建路径,在此我们点击OK。

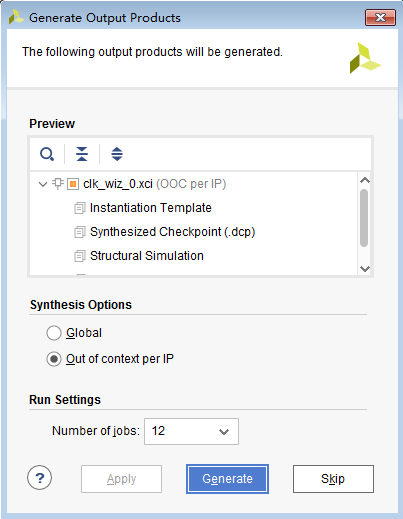

此处我们也保持默认然后点击Generate。

生成好之后,在源文件界面会看到我们生成的IP核。

接下来我们写个顶层文件,调用一下我们的IP核,然后做个仿真看一下我们的输出波形。

顶层代码如下:

1 module pll(23 input wire clk,4 input wire rst_n,5 output wire clk_100m,6 output wire clk_30m,7 output wire clk_10m,8 output wire clk_10m_180,9 output wire locked10 );1112 clk_wiz_0 clk_wiz_0_inst13 (14 // Clock out ports15 .clk_out1(clk_100m), // output clk_out116 .clk_out2(clk_30m), // output clk_out217 .clk_out3(clk_10m), // output clk_out318 .clk_out4(clk_10m_180), // output clk_out419 // Status and control signals20 .reset(~rst_n), // input reset21 .locked(locked), // output locked22 // Clock in ports23 .clk_in1(clk)); // input clk_in12425 endmodule

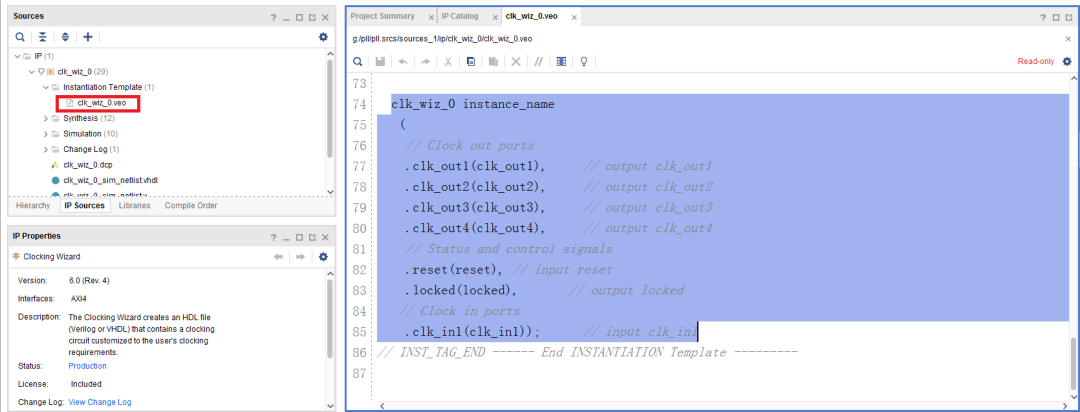

在顶层文件当中,我们需要例化我们的IP核,那么我们需要先打开IP Sources,我们会看到我们新建的IP,然后点开之后会看到第一个选项Instantiation template,打开之后又会看到一个.veo文件,双击打开就可以看到我们ip核的例化头文件。如图所示:

我们将头文件直接复制粘贴到我们的顶层文件当中,然后修改括号里面的端口名。修改好之后就是我们顶层文件的样子。

接下来是我们的仿真文件,代码如下:

1 `timescale 1ns / 1ps23 module pll_tb;45 reg clk;6 reg rst_n;7 wire clk_100m;8 wire clk_30m;9 wire clk_10m;10 wire clk_10m_180;11 wire locked;1213 initial begin14 rst_n = 0;15 clk = 0;16 #105;17 rst_n = 1;18 #10000;19 $stop;20 end2122 always #10 clk = ~clk;2324 pll pll_inst(2526 .clk (clk ),27 .rst_n (rst_n ),28 .clk_100m (clk_100m ),29 .clk_30m (clk_30m ),30 .clk_10m (clk_10m ),31 .clk_10m_180 (clk_10m_180),32 .locked (locked )33 );3435 endmodule

代码编译没有问题之后,我们打开仿真波形观察现象:

观察波形可以看出,在复位结束之后的一段时间内,输出是没有波形的,在这段时间,IP核的输出还不稳定,所以看不到波形,在黄色光标处,locked信号拉高,此时表明输出稳定,我们观察后续波形的周期,跟我们定义的频率正好对应。

- End -

FPGA技术江湖广发江湖帖

无广告纯净模式,给技术交流一片净土,从初学小白到行业精英业界大佬等,从军工领域到民用企业等,从通信、图像处理到人工智能等各个方向应有尽有,QQ微信双选,FPGA技术江湖打造最纯净最专业的技术交流学习平台。

FPGA技术江湖微信交流群

加群主微信,备注姓名+公司/学校+岗位/专业进群

FPGA技术江湖QQ交流群

备注姓名+公司/学校+岗位/专业进群