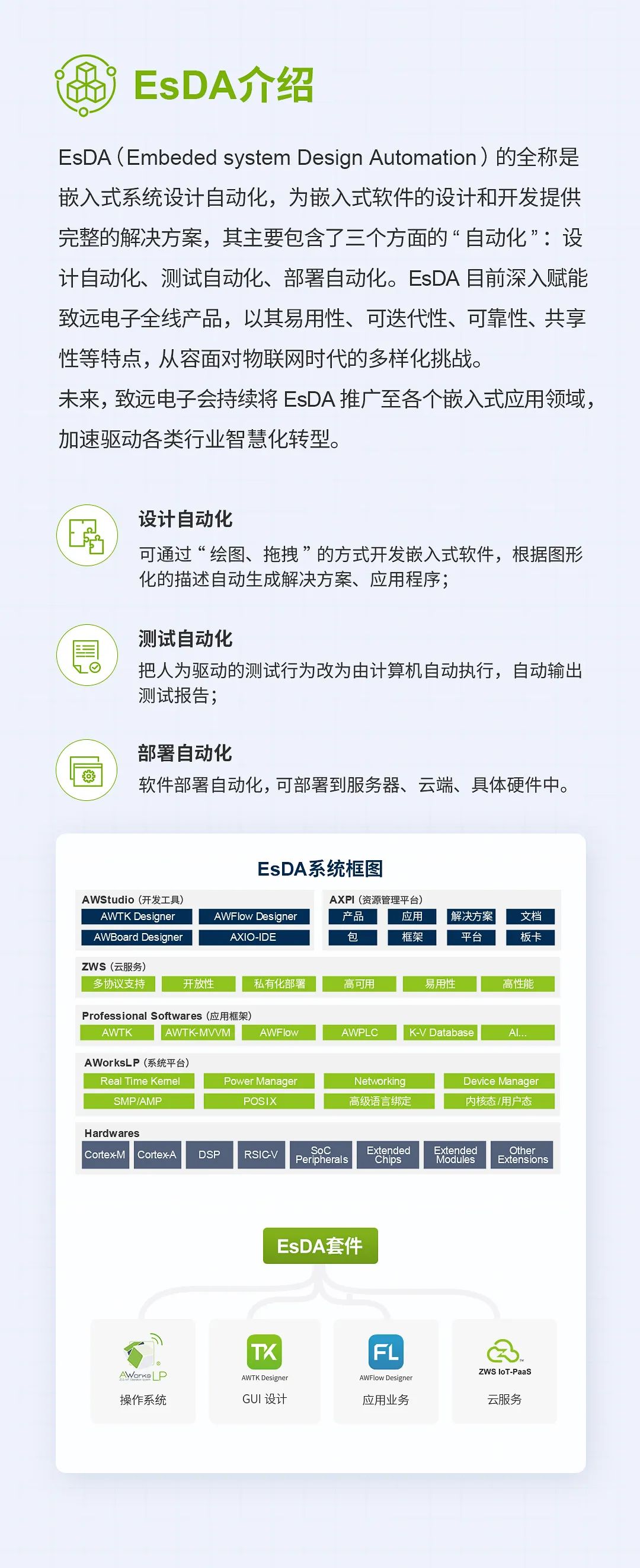

通信接口了解

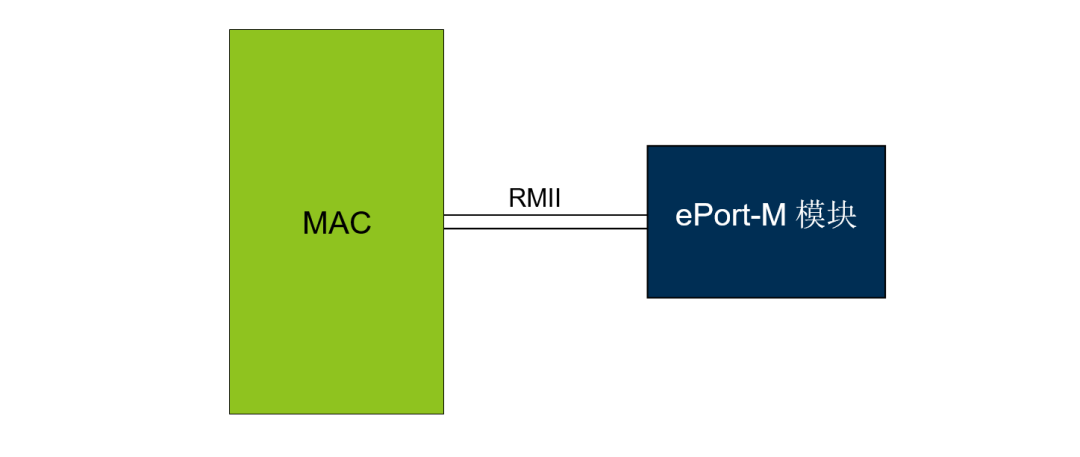

通信接口了解ePort-M百兆以太网模块采用了RMII接口(精简的独立于介质接口),相比较于MII接口(媒体独立接口),RMII通信所需要的引脚数更少,根据IEEE802.3标准,MII接口需要16个信号引脚,RMII接口则只需要7个信号引脚,此时ePort-M模块的时钟信号频率为50MHz,该时钟信号由MAC端提供或外部时钟源提供。

ePort-M模块简单易用,然而应用到产品时,如何保证模块的正常通信,提高模块的的通信质量呢?下面介绍如何进行ePort-M模块的原理图设计以及PCB设计。

原理图设计

原理图设计

PCB设计

PCB设计

1、ePort-M模块PCB布线时,发送信号RMII_TXEN、RMII_TXD0、RMII_TXD1串联的22Ω电阻需要靠近MCU放置;

2、以太网的信号线需要控制单端50Ω阻抗匹配,避免信号传输过程出现反射以及过冲;

3、PCB走线保证TXD组内100mil等长,RXD组内100mil等长处理,模块内部TXD/RXD组已做等长处理,因此在处理等长时,无需考虑ePort-M模块内部的走线长度;

4、以太网复位信号是敏感信号,PCB走线距离MCU应尽量短,并且远离其他高速信号;

5、在条件允许的情况下,以太网时钟信号线两侧需要进行包地处理,包地线应该尽量粗,同时包地线上应该多打地孔,以减少时钟信号线与其他信号线之间的串扰。

关联产品

关联产品

更多往期文章,请点击“ 阅读原文 ”。