一、引言

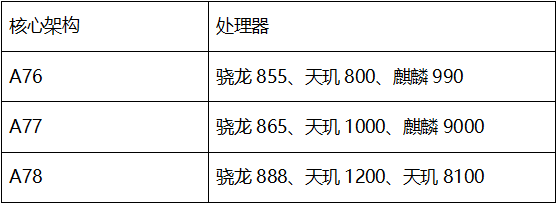

伴随智能手机的高速发展,移动处理器架构设计厂商ARM公司几乎每年都更新CPU的核心架构。从2018至2020年,ARM公司基于ARMv8架构推出了三代Cortex-A76、Cortex-A77、Cortex-A78经典CPU核心架构。基于这几代CPU架构,芯片设计厂商也设计了多款性能优秀的处理器产品。本文从A76微架构开始学习,通过对比每一代的变化,让读者了解处理器微架构关键知识。下表给出了一些基于这三代ARM处理器架构的典型处理器产品。

二、从A76开始了解ARM微架构

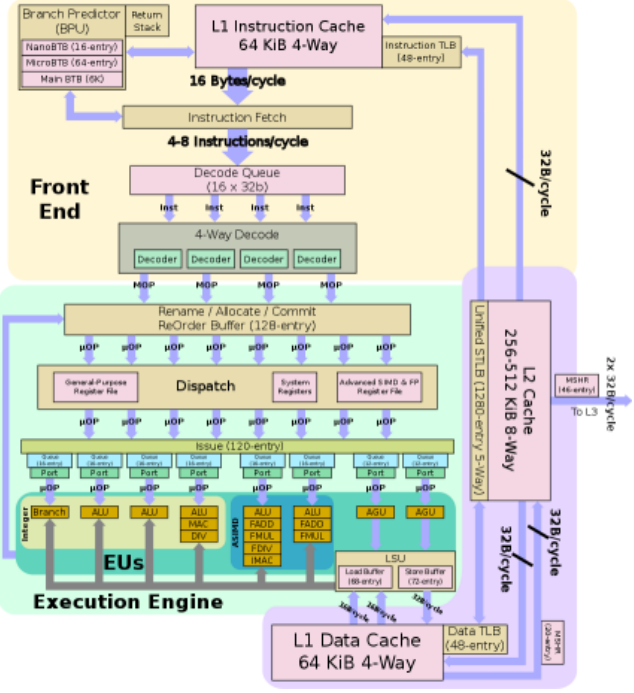

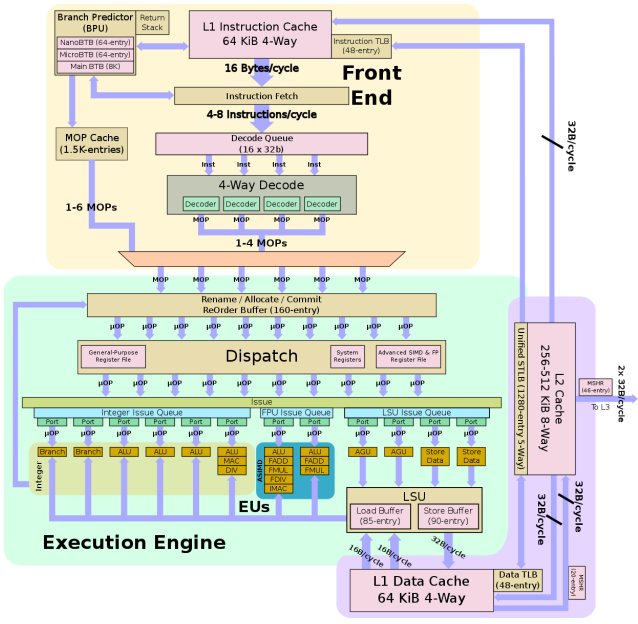

从ARM的A76开始,网络上可以查询到较多资料,例如我们可以从wikichip网站(en.wikichip.org)获取到A76的完整微架构框图。

1. DSU(DynamIQ Shared Unit)

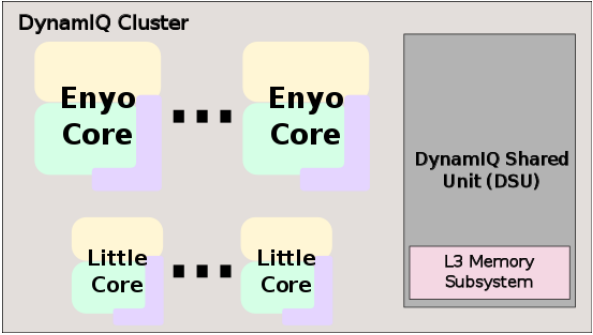

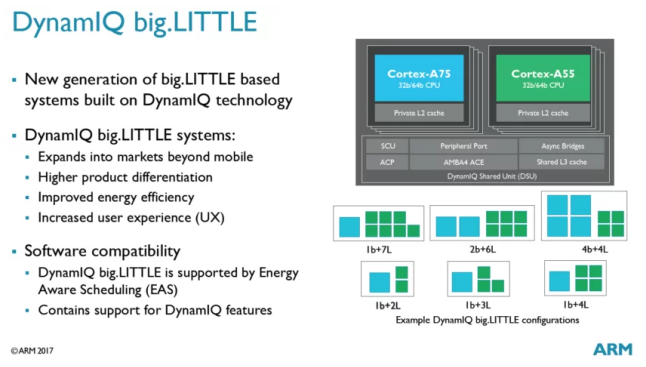

从A75开始,ARM提出了一个新的多核心管理系统单元,叫做DSU。通过DSU模块,CPU设计者可以随意摆放不同架构的核心并共享L3缓存,减少不同架构核心直接传递数据损耗。在DSU架构之前,每个Cluster需要摆放同架构CPU,如将4个A73处理器放在一个Cluster中,将4个A53放在另外一个Cluster中,这两个Cluster的数据相互访问会有一定的连接损耗。

利用DSU模块,开发者可以随意设计CPU的组合,例如图中1大+7小,2大+6小,4大+4小,1大+2小,1大+3小,1大+4小等等组合。

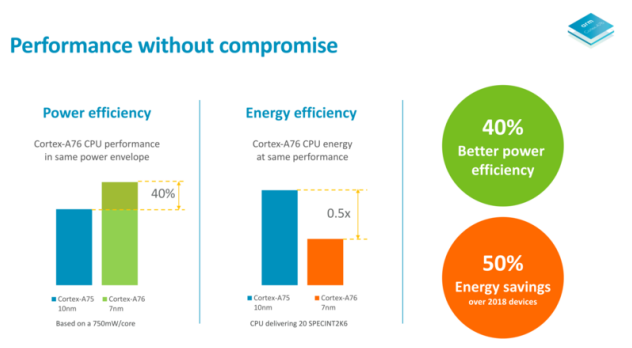

2. 性能功耗优化

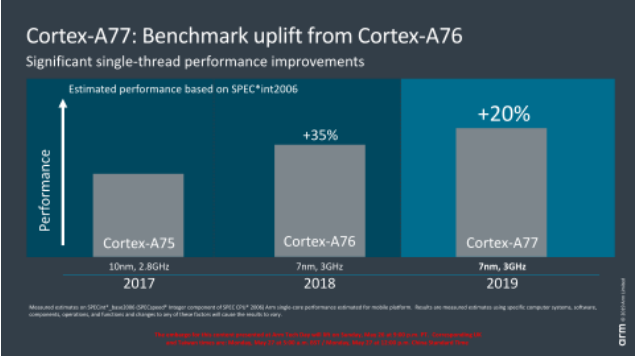

架构和工艺具有一定的关联性,如A76架构设计可采用7nm工艺,根据ARM数据,基于7nm的A76比基于10nm工艺的A75,性能可提升40%,或同性能下能耗降低50%。可见A76相比上一代的A75的提升较大,后面我们会详细了解架构上差异点。

3. 三级缓存设计

A76采用三级缓存机制,其中:

L1是核心独有缓存,具有独立的64KB指令Cache(ICache)和64KB数据Cache(DCache);

L2是核心独有缓存,可以配置成256KB或者512KB(加钱);

L3是核间共享缓存,在DSU内部,可以配置成2MB或者4MB。

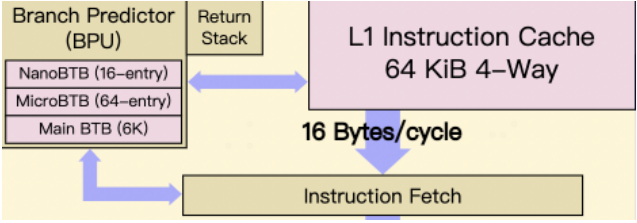

多级流水线系统中,在执行分支判断指令时,系统如果不知道下面走哪一条分支,需要等到分支执行出结果才可以再获取正确的指令。为了提升流水线性能,现代处理器中提供了一个分支预测单元(BPU),用来预测常用路径,并提前进行指令预取,确保流水线被填充完整。

A76的BPU和指令Fetch单元独立,BPU可以同时和Fetch单元工作,提前推测并获取分支后指令,降低分支预测的延迟。

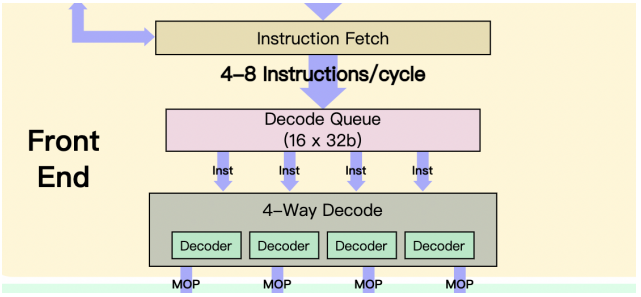

5. 前端设计(Front-end)

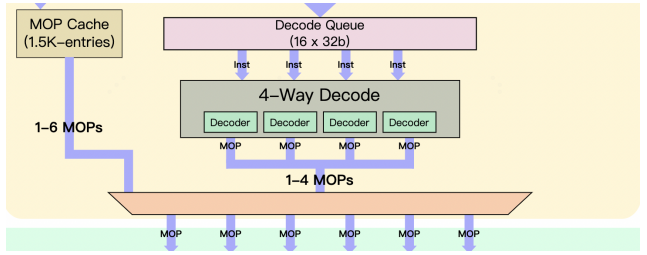

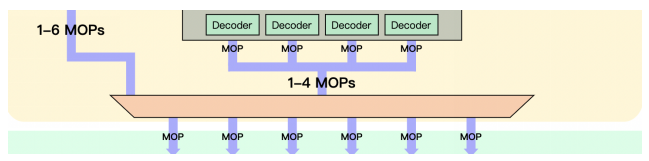

指令预取后进入一个解码队列,A76提供了4路decoder,相比A75增加了一路decoder单元,这是性能提升的一个要素。

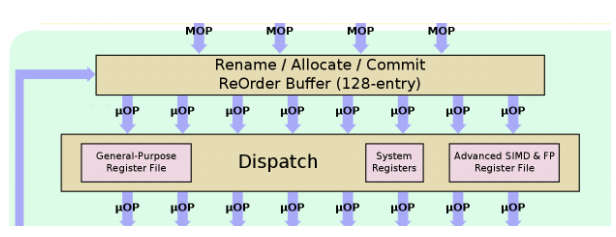

6. ROB模块设计

经过译码的指令叫做MOP(Macro-Operation),MOP不是实际执行的指令,最终送到执行单元的指令叫做uOP(Micro-Operation)。MOP比uOP稍微复杂一些,可能是多条uOP的组合指令,通过后端单元的拆解,可以把MOP分解成处理器可以执行的最基础指令uOP,uOP的指令数量约比MOP多20%。

ROB(ReOrder-Buffer)模块提供了128个entry,用来将指令进行重新排序,尽可能填充流水线,这里可以看到A76设计的输入是4路MOP,输出是8路uOP。

7. 执行单元 (Execution Engine)

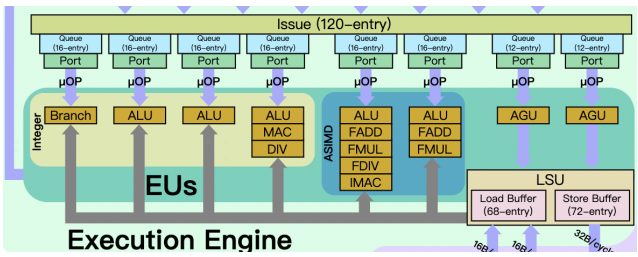

Dispatch单元将uOP指令发射到执行单元(Issue),执行单元提供了120个entry,分成三类:整型、浮点和读写,整型部分包括了1个分支单元,2个基础ALU单元,1个复合ALU单元;浮点部分提供了2个128bit的高级SIMD指令单元;读写部分则提供了2个AGU(Adress Generation Unit)地址单元。

8. LSU(Load Store Unit)设计

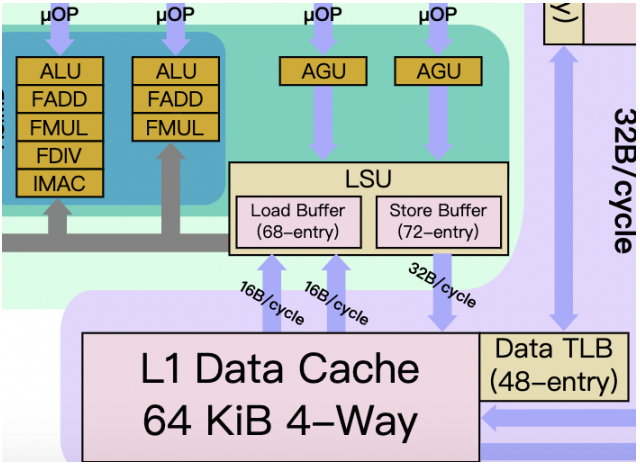

LSU模块和执行单元的2个AGU相连接,同时连接64KB的L1数据缓存(DCache),并提供2个16B/cycle的load端口和1个32B/cycle的store端口。

9. 小结

至此,我们从取指、译码、指令分派、指令发射、指令执行到数据读写,简略了解了A76处理器的微架构,下一节我们通过对比A77和A76架构的差异,进一步了解ARM微架构设计的步伐。

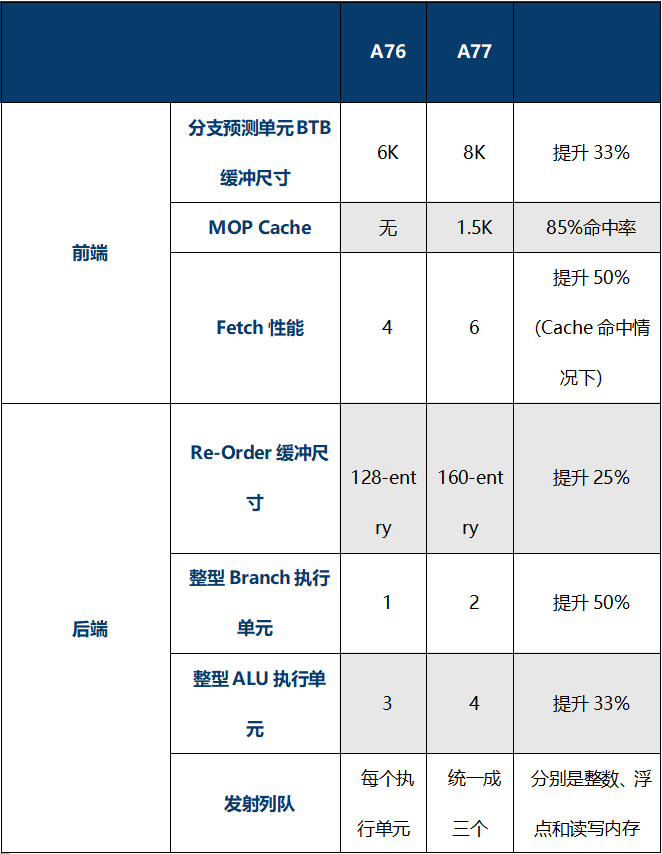

三、A77微架构和A76对比

A77微架构图,大家且看且珍惜,因为自A77之后的产品在网络上很难找到完整的微架构图了。

1. 性能提升

2. L0缓存(MOP Cache)

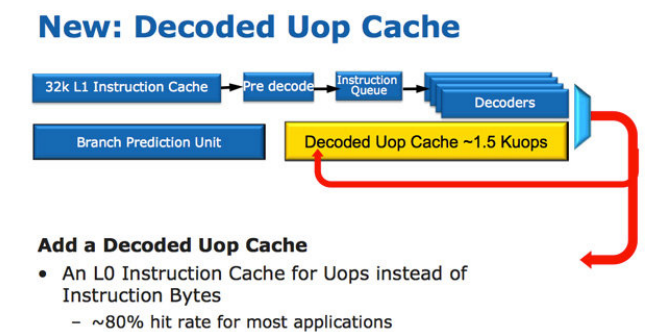

A77新引入了MOP Cache模块,这个模块并不是ARM的创新设计,在PC处理器上已经有了,例如Intel在早期的酷睿Sandy Bridge处理器中就加入了uOP Cache模块。

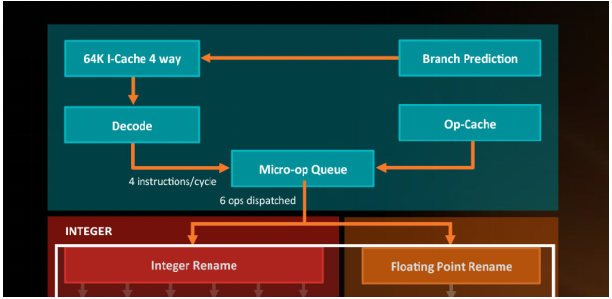

此外AMD的Zen架构也有MOP缓存模块。

MOP Cache主要用做L0级别缓存,存储译码过的MOP指令。MOP Cache的好处是如果在里面找到需要的指令,前面的电路模块都可以暂时由MOP Cache来替代,可以节省功耗提升性能。ARM数据显示这个MOP Cache的命中率有85%,可见是A77的一个非常大的改进。

继续看下MOP Cache的尺寸,ARM给的尺寸数据是1.5K而不是1.5KB,单位不是Byte而是条,考虑到ARM常规decoded出的机器码是32位宽(Aarch64也是32位宽,当然也有个别64位宽指令),推测这个L0 Cache的大小应该是6KB左右(和Intel的sandy bridge时一样)。

移动处理器领域引入L0,ARM并不是首家,早在高通的Snapdragon S4时代就在Krait核心中引入了L0 cache。根据数据显示1.5K的Cache就可以达到80-85%的命中率,再增加Cache,提升命中率的边际效应会越来越明显。

3. 前端设计(Front-End)

A77相对于A76的另一个重要变化是产生MOP指令的能力从原来的每周期4个提升到最多6个,但是decode的能力还是保持4个没有变化。可以对比下整体上fetch和decode的基本架构和A76没有太大变化,MOP提升的主要原因是新加入的MOP Cache提供的。如果MOP Cache命中,可以绕过decode模块最多一次取6条MOP指令,如果不命中回到decode模块还是一次4条,L0 Cache和Decode进行了很好的补充,让一周期可以提供更多的MOP指令。

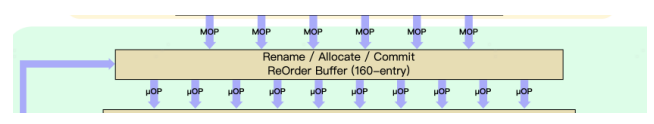

4. ROB模块设计

A77相对A76在执行单元上提升了重排序缓冲的大小(ReOrder-Buffer),还记得A76是128-entry,A77提升了25%到160-entry。

另外可以看到输入是6条MOP,输出提升到了10条uOP,对比A76则是8条。据说其他厂商基于ARM定制内核时会修改这个部分,随着ARM内核逐步吸收这些优秀的设计,定制ARM内核的空间和收益会越来越小 。

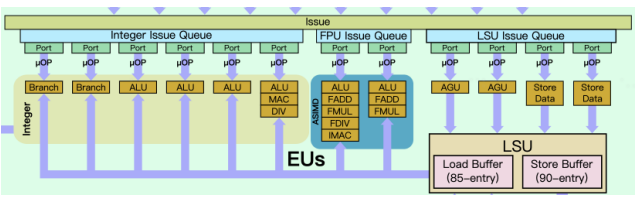

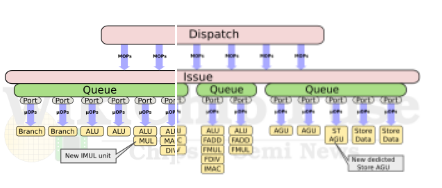

5. 执行单元

A77相比A76在执行单元也有比较大的改变:新增加了一路分支单元,将分支预测的带宽提升了一倍;新增了第四个基础整型ALU单元,这个单元可以用一个周期执行简单的算术运算或二个周期执行更复杂运算。A77一共4个整型ALU,其中3个是基础整型ALU单元,还有一个是复杂整型ALU单元,可以执行更复杂的计算(例如MAC乘加,DIV除法),A76也有这个复杂ALU单元。在整型执行单元上,A77相对A76提升是比较大的,从4个提升到6个,有50%的提升。

此外,还A76的每个执行单元都有独立的发射列队,A77则进行了一定程度的优化,将发射列队(issue queue)统一成三个,整型、浮点和读写发射列队,由于A77的执行单元多,将发射列队统一进行管理和分配,可以进一步提升执行效率。

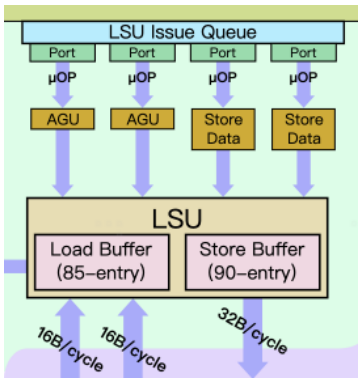

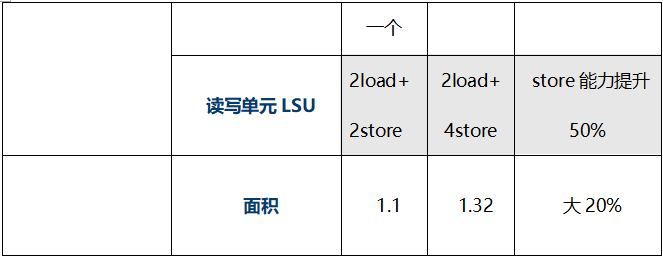

6. LSU设计

A77在Load\Store单元上有两个独立的地址生成单元AGU,这和A76是一样的。不同的地方是A77额外增加了两路Store端口,等于将Store的带宽增加了一倍。同时这四路LSU单元也共享一个发射队列,ARM宣称这样可以提升25%的内存并发读写性能。

再来看一下LSU单元,更宽的执行单元需要有更宽的LSU支持,A77增大了LSU的load和store buffer,同时可以支持85级深度load 操作和90级深度store操作,总共支持同时175个内存操作,稍高于指令操作的宽度160,相比A76的LSU深度140,提升了25%。

7. 小结

最后整理了一个更详细的表格来对比A77和A76,A77是ARMv8系列中非常成功的一代,基于A77,产生了如麒麟9000、骁龙865这样经典的产品。

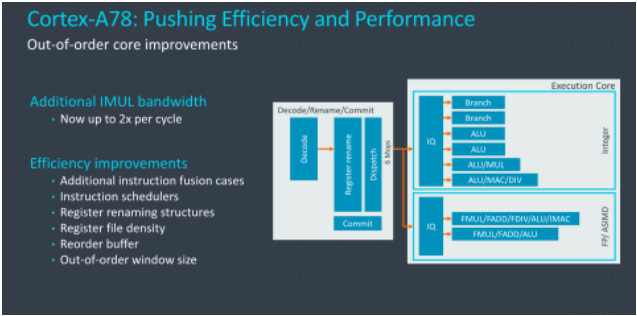

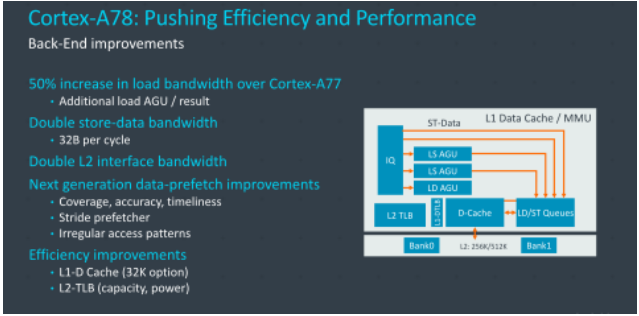

四、A78微架构和A77对比

1. 性能功耗优化

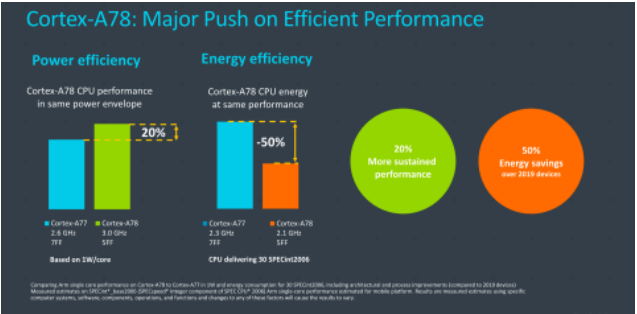

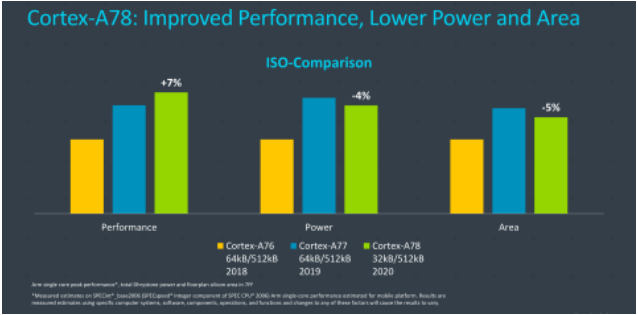

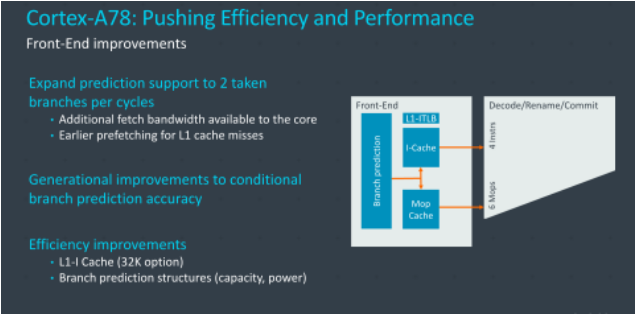

2020年,ARM更新了代号Hercules的A78新架构,也是ARMv8体系中最后一代中核架构。ARM宣传这一代是“持续的性能功耗领先”,图中看到性能提升了20%,工艺从7nm提升到5nm,注意性能提升包含了频率的15%提升,架构的性能提升ARM估计在7%左右。得益于工艺进化到5nm,同样性能,功耗可以比A77降低50%(2.1GHz相当于A77的2.3GHz)。从第二张图可以看出,A78这一代的主要设计目标是小幅度提升性能,提升能效并减少芯片面积。

2. A78微架构的一些特点

1、L1缓存:ARM提供了32KB缓存的选择,让一些注重成本和芯片面积的厂商可以选择更低的数据和指令缓存,默认是64KB。

2、分支预测:分支预测的带宽相对A77提升了1倍。

3、执行单元:增加了一个MUL单元,允许一个周期进行2个整型的乘法运算(A77是一周期1个)。增加了一个用于Store的AGU单元,Store的能力从16B/cycle提升到32B/cycle。

A78是ARMv8架构最后一代产品,主要是对前面几代微架构的优化,可谓ARMv8架构的守门员了。

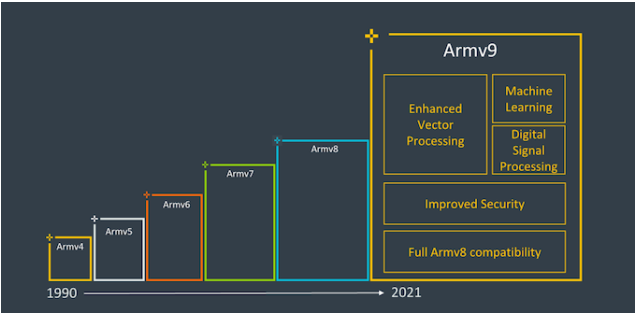

五、总结

A78是ARMv8架构的最后一代产品,智能手机依然在高速发展并快速更新产品,ARM处理器的架构也在持续迭代和更新。2020年,ARM公司提出了对厂商定制高性能核心的计划,并推出了面积更大性能更强的Cortex-X系列核心。2021年,ARM公司推出了全新的ARMv9架构,目前已经有A710、A715等产品接替A78的路线。限于篇幅限制,后续我会和大家一起继续学习X系列和ARMv9架构的相关内容。

摘要

1、DSU介绍 https://www.androidauthority.com/arm-dynamiq-need-to-know-770349/

2、A76 wikichip https://en.wikichip.org/wiki/arm_holdings/microarchitectures/cortex-a76

3、A77 wikichip https://en.wikichip.org/wiki/arm_holdings/microarchitectures/cortex-a77

4、A77介绍 https://www.anandtech.com/show/14384/arm-announces-cortexa77-cpu-ip

5、Intel's Sandy Bridge Architecture Exposed https://www.anandtech.com/show/3922/intels-sandy-bridge-architecture-exposed/2

6、AMD Zen Microarchitecture https://www.anandtech.com/show/10578/amd-zen-microarchitecture-dual-schedulers-micro-op-cache-memory-hierarchy-revealed

7、A78介绍 https://www.anandtech.com/show/15813/arm-cortex-a78-cortex-x1-cpu-ip-diverging

8、A78 wikichip https://en.wikichip.org/wiki/arm_holdings/microarchitectures/cortex-a78

9、A78介绍 https://fuse.wikichip.org/news/3536/arm-unveils-the-cortex-a78-when-less-is-more/

10、ARMv9介绍 https://www.anandtech.com/show/16584/arm-announces-armv9-architecture