通过湿法转移二维材料与半导体衬底形成异质结是一种常见的制备异质结光电探测器的方法。在湿法转移制备异质结的过程中,不同的制备工艺细节对二维材料与半导体形成的异质结的性能有显著影响。

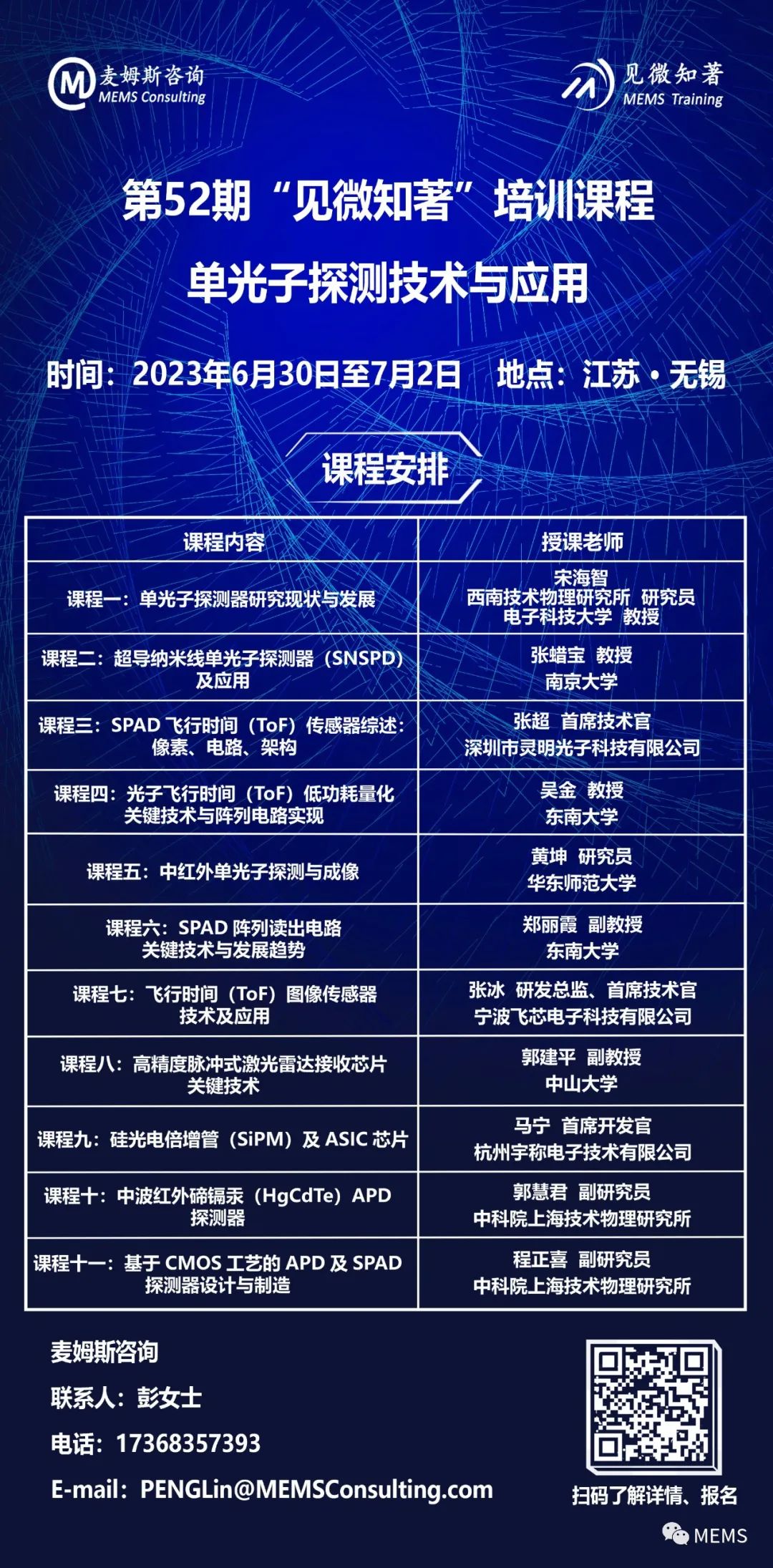

据麦姆斯咨询报道,近期,西安工程大学理学院的科研团队在《中国光学(中英文)》期刊上发表了以“石墨烯/硅异质结光电探测器的制备工艺与其伏安特性的关系”为主题的文章。该文章第一作者为杨亚贤,主要从事新型光电探测器工艺制备及其应用的研究工作;通讯作者为张国青教授,主要从事新型光电子器件方面的研究工作,重点为单光子响应探测器件的研制。

本文以典型的二维材料石墨烯(Gr)为例,采用湿法转移制备了一系列相同的Gr/Si异质结光电探测器,对其制备工艺与伏安特性的关系进行了详细研究。

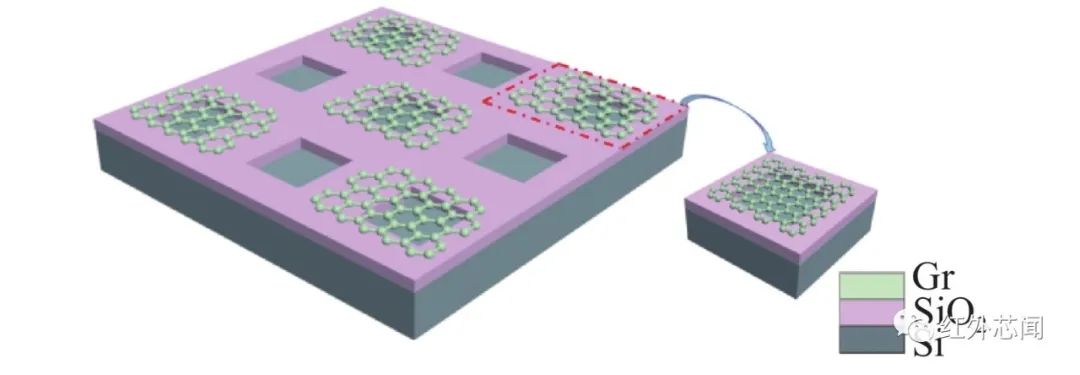

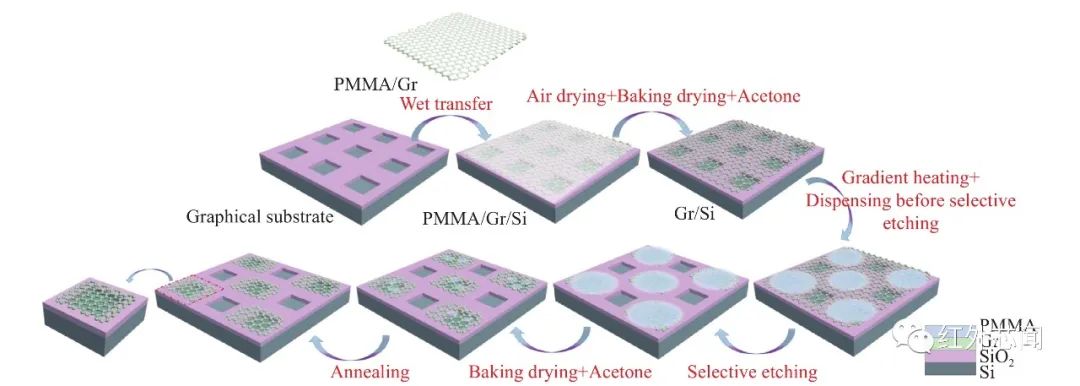

图1为Gr/硅异质结光电探测器的结构示意图,其制备工艺流程图见图2所示,主要步骤如下:

(1)在外延了50微米厚N-型外延层(电阻率约16 ohm-cm)的<100>晶向的低电阻率N型区熔硅衬底上,采用湿法氧化3000埃的二氧化硅薄膜。通过光刻与刻蚀技术,在二氧化硅薄膜上开1 mm见方的硅窗口,裸露出硅衬底,用以与石墨烯形成范德华异质结。

(2)Gr转移至衬底。首先对Si衬底进行超声清洗,准备Gr,本文中使用的Gr为ACS(先进化学供应公司)一步转移式Gr,无需再次旋涂PMMA,将Gr转移至带有硅窗口的衬底上。在转移过程中,要尽量减少Gr在水中漂浮的过程中下层气泡的产生,使用载玻片将气泡逐渐去掉,直到气泡几乎无法被观察到为止。将衬底斜入水中,缓缓将Gr捞起,使得Gr居于衬底中部,此时将转移好的样品进行自然风干,将样片放置在滤纸上,用培养皿覆盖避免灰尘落入,静置1 h。

(3)异质结样片烘干。将样片放置在预热好的热板上,采用梯度式升温,避免升温蒸发过快,造成Gr被气泡顶破。整个烘干过程完成后,将样片自然冷却至室温,在洁净的培养皿中倒入一定量丙酮,将样片浸泡在丙酮中除胶,热板预热45 °C,加热丙酮 2 h,加速PMMA溶解,更换丙酮浸泡12 h,使用另一洁净培养皿盖住,减少丙酮挥发同时避免灰尘进入。除胶进程结束后,使用无水乙醇对残留在样品表面的丙酮溶液进行清洗,使用洗耳球将乙醇吹干,样片置于滤纸上,盖上培养皿静置待乙醇挥发完全,将其置于提前预热好的热板上恒温(50 °C)烘干。

(4)石墨烯选择性刻蚀,用以将不同的异质结器件隔离开来,同时刻蚀掉大部分非光敏区的石墨烯。将PMMA点在氧化硅窗口上方的Gr层上保护局部的Gr。点胶时为避免点与点间的PMMA晕开粘连,提前将其放置在预热好的热板上60 °C加热点胶,这样既加速了PMMA的凝固,也保证PMMA点胶的均匀性。整个点胶过程完成后,将热板升温至85 °C,凝固PMMA 15 min, 将样片置入氧等离子体清洗机腔体内,进行氧等离子体干法刻蚀,射频功率为70 W,氧气流量为40 mL/min,刻蚀时长2.5 min。然后对刻蚀后的样片进行除胶,此处除胶步骤与转移烘干后的除胶步骤一致,但是由于点胶PMMA层厚度较大,因此水浴加热丙酮的过程所需时间略长,除胶步骤完成后对其进行170 °C烘干40 min。

(5)退火。最后对整个样片进行退火处理,将样片放入CVD退火炉中进行退火处理。退火时为Ar气氛围保护,400 °C退火2 h。退火处理一方面是为了将转移前的Gr外表面的PMMA与刻蚀时的PMMA进一步驱除,另一方面溶液转移过程中残留的可挥发的杂质也会由于在CVD中退火被带走,同时夹层中可能依然残余的水分,也会被带走。经上述制备流程,即可得到Gr/硅异质结。

图1 Gr/硅异质结光电探测器结构示意图

图2 Gr/硅异质结光电探测器制备工艺流程图

制备好的Gr/硅异质结首先进行了表面形貌和拉曼光谱表征,然后进行了光电特性参数表征。表面形貌观察使用了金相显微镜,硅表面石墨烯的拉曼光谱测试使用的是英国雷尼绍(Renishaw)公司制造的显微共聚焦激光拉曼光谱仪。Gr/硅异质结光电探测器电学特性测试使用的是手动探针台,利用半导体参数测试仪给异质结施加不同偏压,同时测量对应的电流,电流随偏压的变化曲线即为伏安特性曲线。将伏安特性曲线数据,按照欧姆定律计算即可得到异质结光电探测器件的静态电阻随偏压的变化。在黑暗条件下,给Gr/硅异质结光电探测器加反向偏压,测量得到的电流为暗电流ID。在本文中使用可调激光光源(波长525 nm,入射光斑面积为5.15 mm²功率调节范围0~0.7 W,AC90,北京宏蓝光电)给Gr/硅异质结器件照射光,测量得到的电流Itot即为光电流Iph与暗电流ID之和。

Gr/硅异质结器件的基本表征

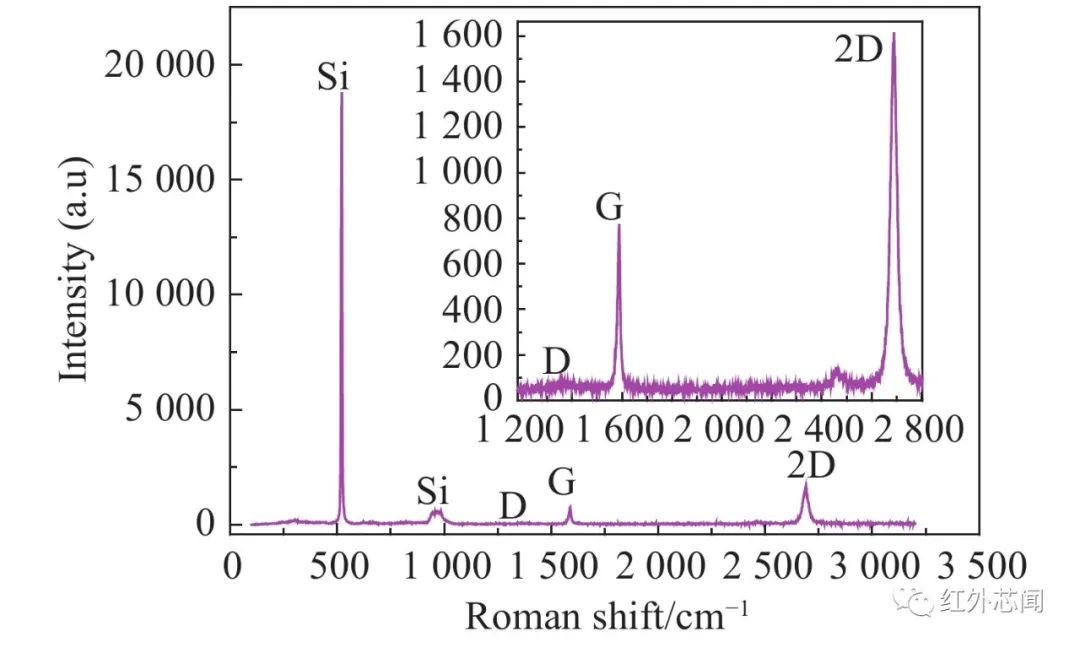

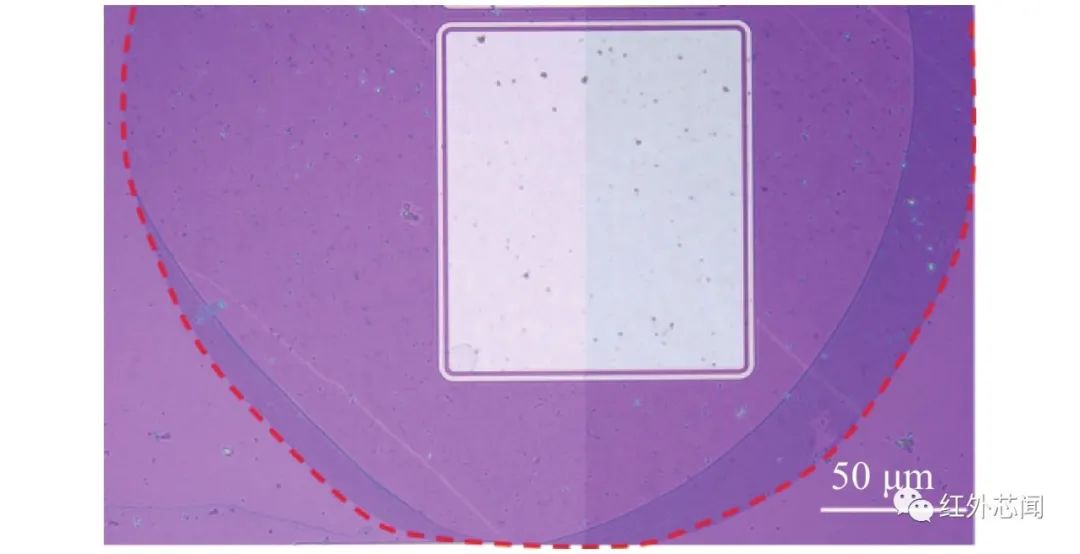

图3为Gr/硅异质结表面Gr的拉曼光谱图,与缺陷相关的D峰(1350 cm⁻¹)较弱,表明石墨烯材料缺陷较少,根据G峰和2D峰的强度比例大于2,可以判断出Gr的层数为单层。图4为选择性刻蚀后的Gr/Si异质结金相显微图。从图中可以看出Gr被PMMA保护得较为完整,连接性良好,未看到明显破损。图中白色图形区域为Si衬底表面无300 nm的SiO₂的区域。白色图形区域内、外可见的斑点是湿法转移过程中的杂质或PMMA胶的残留。

图3 转移到图形化Si衬底表面的Gr拉曼谱图

图4 选择性刻蚀退火后的Gr/Si异质结整体金相显微图(石墨烯边界沿着红色虚线圆圈)

烘干工艺对Gr/硅异质结暗电流的影响

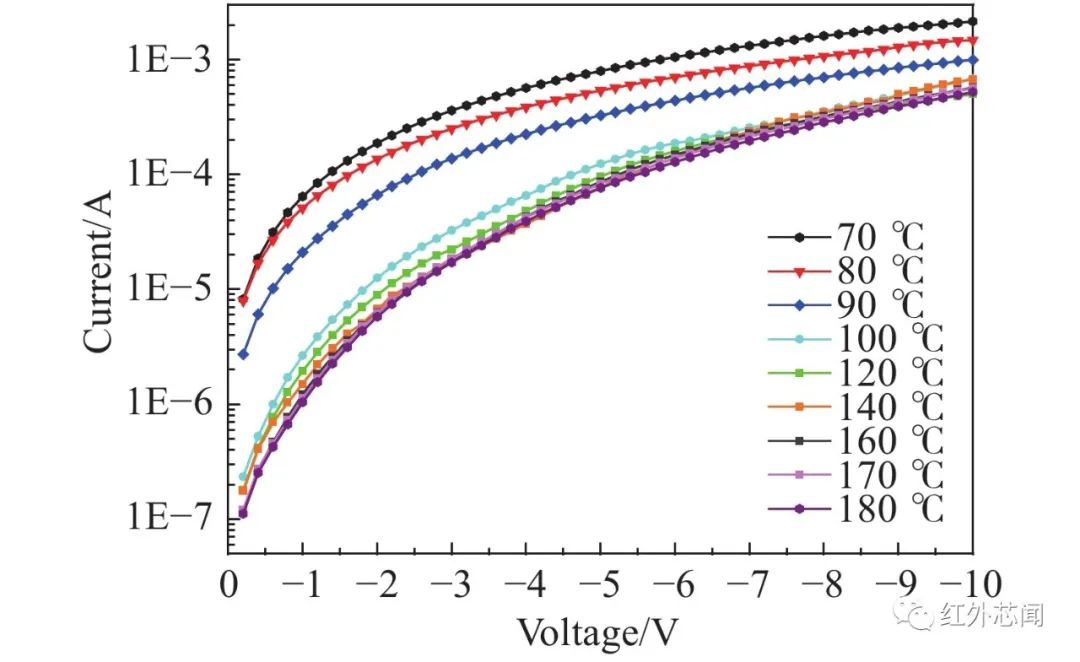

图5为在黑暗环境测得的不同烘干温度条件下Gr/硅异质结的反向I-V曲线(烘干时间均为60 min)。从图中容易看出随着烘干温度的增加,暗电流下降明显,说明高温烘干处理有利于减小异质结器件的暗电流。进一步观察可以看出,100 °C及以上的烘干温度条件下,暗电流明显减小。反向偏压为−2 V时,100 °C烘干温度条件下的暗电流比90 °C烘干温度下减小了将近1个量级。我们认为之所以出现这种现象,是因为Gr/硅异质结在湿法转移制备过程中,Gr/硅的夹层中残存有水分,烘干处理有利于驱赶夹层中残存的水分;高于100 °C的烘干处理,暗电流下降明显是因为烘干温度已达到或高于水的沸点,夹层中的水分彻底汽化,从石墨烯边界或破损处排出,从而减小了异质结的暗电流。从图中还可以看出,烘干温度高于170 °C时,I-V曲线几乎不再变化,因此,可以认为最佳的烘干温度为170 °C。在实验过程中,我们还发现如果直接将样品放到超过100 °C的热板上,在显微镜下观察硅衬底表面的Gr层会看到破损和褶皱,I-V曲线测试发现该类样品几乎不导通,少数导通的漏电也很大。经分析认为这是由于Gr/硅异质结夹层中残留的水分快速地沸腾蒸发、鼓泡造成了Gr的破损和褶皱,使得Gr的连通性下降,进而造成异质结电学性能下降甚至损坏。

图5 不同烘干温度条件下选择性刻蚀前大面积Gr/Si异质结的反向伏安特性曲线对比(黑暗遮光条件下测试)

从图5中还可以观察到烘干工艺虽然能减小异质结的暗电流,但暗电流的绝对值相比于硅同质结依然较大,而且看不到击穿拐点,这可能是由于Gr/硅异质结存在较高密度的表面态,导致异质结处的产生复合电流较大,从而产生较大的暗电流。为了进一步减小Gr/硅异质结的暗电流,我们对大面积Gr/硅异质结进行了选择性刻蚀处理,使多个Gr/硅异质结独立,并且刻蚀掉了大部分未与硅接触的Gr。

刻蚀、退火工艺对Gr/硅异质结暗电流的影响

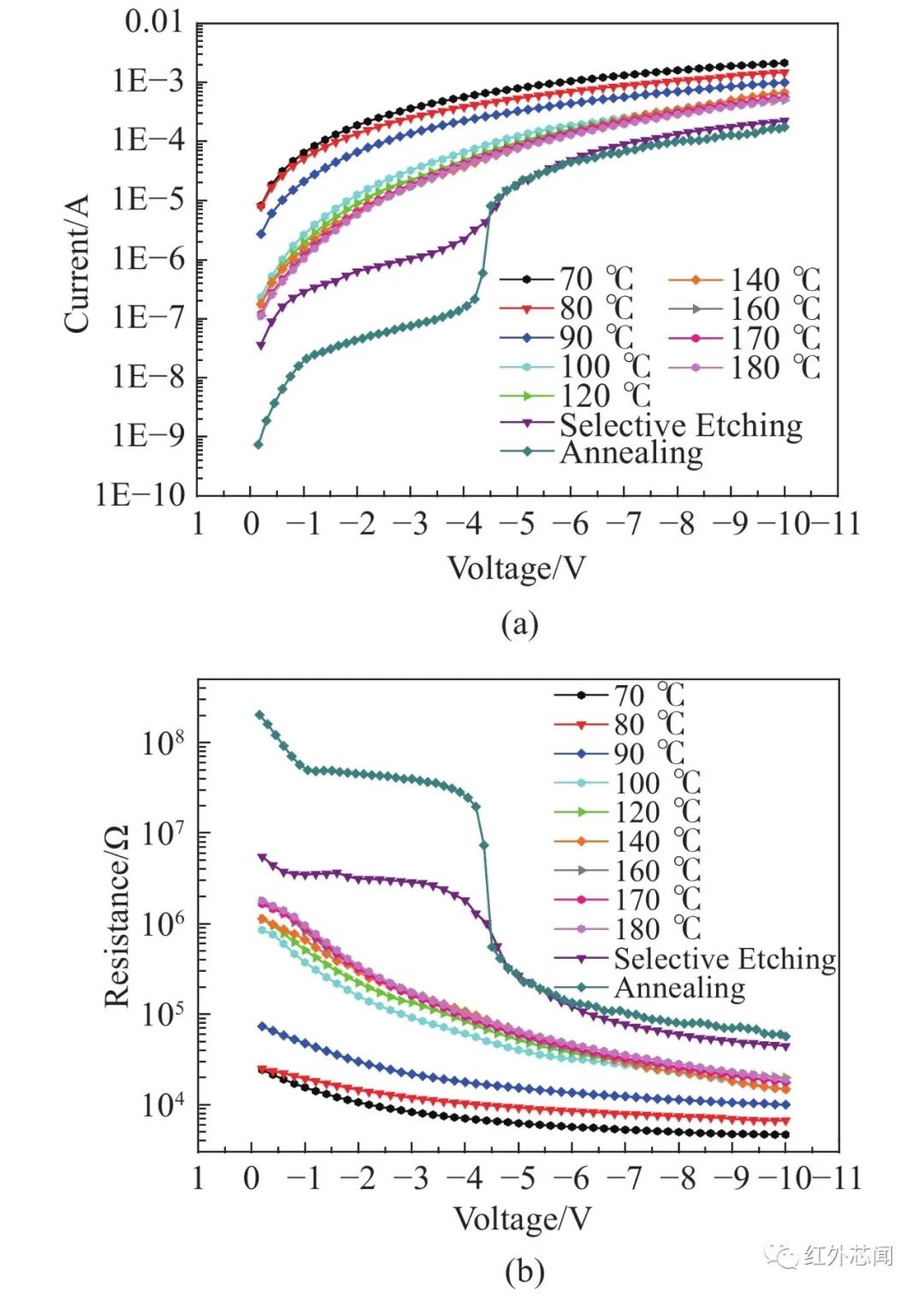

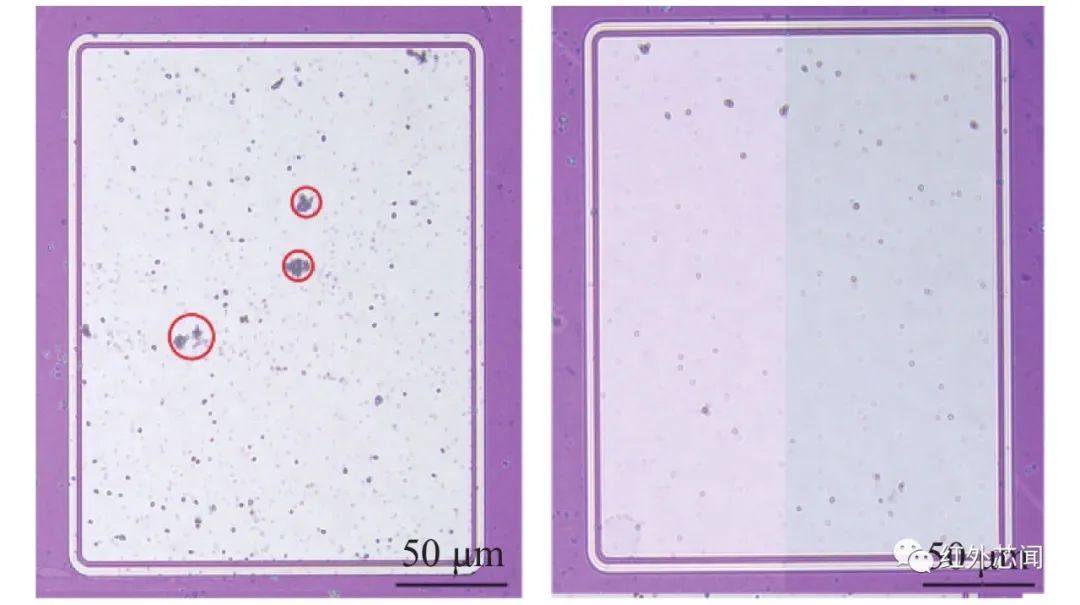

图6(a)为不同烘干、刻蚀、退火工艺条件下Gr/Si异质结的反向I-V曲线对比。根据前面3.3部分讨论的最佳烘干温度,这里选择性刻蚀后的烘干温度定为170 °C。从图6(a)中可以明显看到,与仅仅烘干后的样品的I-V曲线对比,选择性刻蚀后漏电流进一步降低,降低了大约1个量级,并且可以看到Gr/Si异质结的击穿拐点(击穿电压约−4.5 V)。图6(b)为不同烘干、刻蚀、退火工艺条件下Gr/Si异质反偏结的电阻随偏压变化曲线对比。从图中可以看到选择性刻蚀后及退火后电阻进一步增大,在反向偏压较低时,可以达到100 MΩ以上。值得关注的是,通过将退火后异质结的反向I-V曲线与选择性刻蚀后的对比观察,可以看出在−4 V反向偏压下,漏电流又降低了约1个量级。我们认为这是由于高温退火减少了Gr/Si异质结中的可挥发性杂质和可能残留的PMMA胶,从而进一步降低了异质结的漏电流。这个观点可以在图7中得到佐证。图7为选择性刻蚀后、退火后的金相显微图,从图7中两幅子图对比可以看出,在刻蚀与退火后,表面的杂质及可能残留的PMMA胶明显减少。

图6 (a)不同烘干温度、刻蚀、退火工艺条件下Gr/Si异质结的反向I-V曲线对比;(b)不同烘干温度、刻蚀、退火工艺条件下Gr/Si异质结的电阻随偏压变化曲线对比(黑暗条件下测试)

图7 选择性刻蚀后与退火后异质结表面金相显微图(左为刻蚀后,右为退火后,红色圆圈内为较明显的可挥发性杂质或可能残留的PMMA胶)

Gr/硅异质结的光响应特性

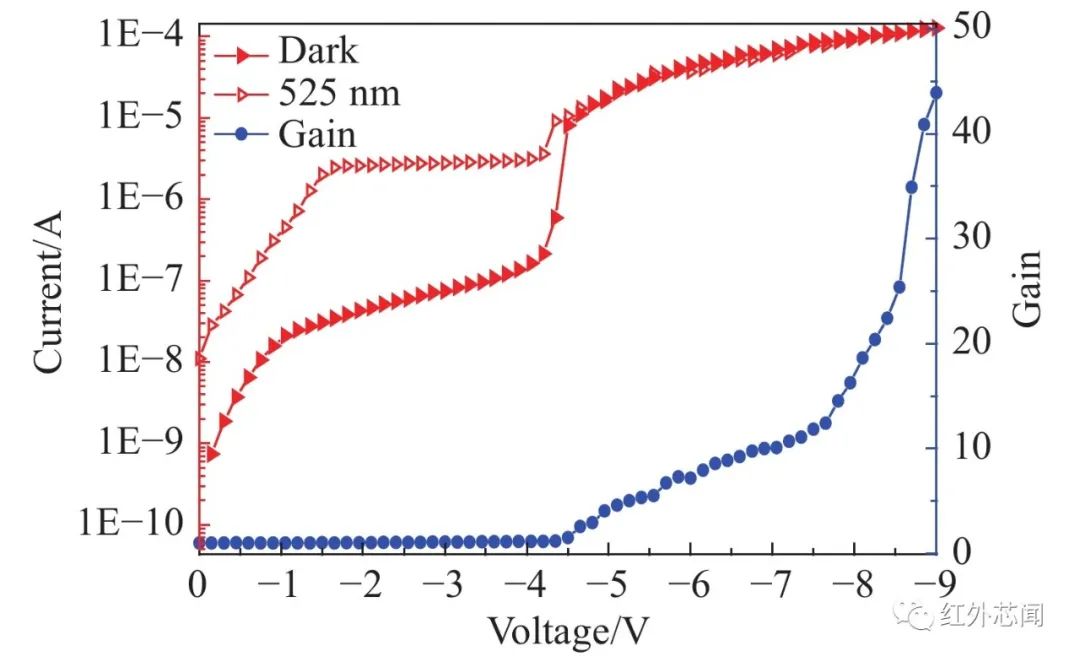

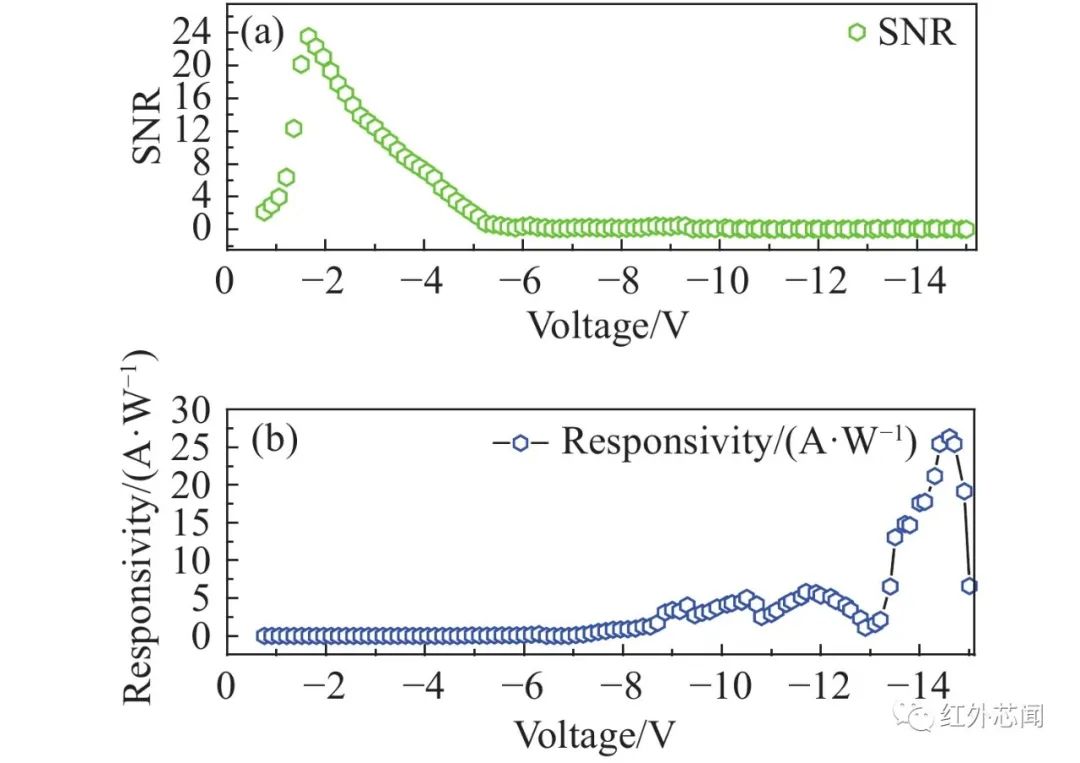

图8中红色空心三角连线和红色实心三角连线分别为加光前后的反向I-V特性曲线,给Gr/Si异质结照射的光功率密度为5.53E-6 W/cm²。可以看到加光后总电流增加了1个量级以上,说明Gr/硅异质结光响应明显。蓝色实心圆连线为Gr/硅异质结的光电流增益随偏压的变化曲线,可以看出偏压超过4.5 V后,增益开始大于1,并且增益随着偏压的增加而增加。偏压−9 V时,增益达到了48。图9为Gr/硅异质结的光响应度(R)和信噪比(SNR)随偏压的变化曲线,可以看到反向偏压在−1.7 V时SNR达到了23.7,光响应度峰值可以达到25.6 A/W,这与文献中报道的1 mm²光敏面积的Gr/Si异质结光电探测器的典型响应度接近,这些结果说明Gr/硅异质结在经过选择性刻蚀、退火工艺处理后,在使漏电水平大幅度降低的同时,还能保证其光电特性不恶化,这些结果为制备高度集成的Gr/硅异质结光电器件工艺提供了一定参考。

图8 选择性刻蚀、退火后Gr/硅异质结的反偏伏安特性与增益曲线

图9 (a)Gr/硅异质结的信噪比(SNR)随偏压的变化曲线(SNR:Signal to Noise Ratio);(b)Gr/硅异质结的光响应度随偏压的变化曲线

梯度式烘干工艺可以显著降低Gr/Si异质结器件的漏电流,最佳的峰值烘干温度为170 °C,170 °C以上漏电流不再有变化。Gr/Si范德华异质结的选择性刻蚀和退火工艺也能够大幅降低漏电流。Gr/Si范德华异质结夹层中的残留水分以及杂质对异质结的漏电流有显著影响。因此,合适的烘干工艺、选择性刻蚀工艺、退火工艺在Gr/Si异质结器件的制备过程中是必要的。这些结论对于使用湿法转移方法制备二维材料异质结器件具有一定的参考价值。

这项研究获得国家自然科学基金(No.11975176)、陕西省自然科学基金(No.2022JQ-660)和人工结构功能材料与器件陕西省重点实验室基础研究基金(No.AFMD-KFJJ-21207)的资助和支持。

DOI: 10.37188/CO.2022-0259