硬件工程师的笔试题中经常会考OC门和OD门,有的放在面试中问,多个OC或者多个OD门能组成线与结构,线与结构考的更频繁,还有一个推挽输出,有一些单片机的GPIO用的就是这种结构,如最常见的STM32。

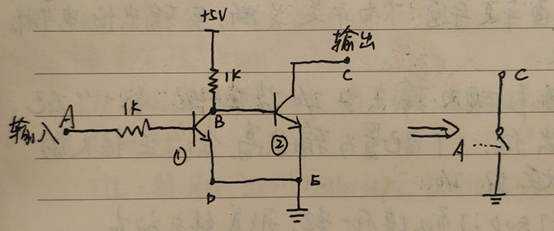

OC门电路

上拉电阻太小,会增大饱和压降,导致输出的低电平很高。

上拉电阻太大,会延缓信号的上升沿。

OC门可以连在一起,做“线与逻辑”。

上拉电压可以根据下一级输入端的电平标准来选择,但也要注意芯片输出端口的电压maximal rating

OD门电路

上拉电阻太小,会导致MOS管②的导通电流过大,烧毁MOS管。

上拉电阻太大,会延缓信号的上升沿。

OD门可以连在一起,做“线与逻辑”。

上拉电压可以根据下一级输入端的电平标准来选择,但也要注意芯片输出端口的电压maximal rating

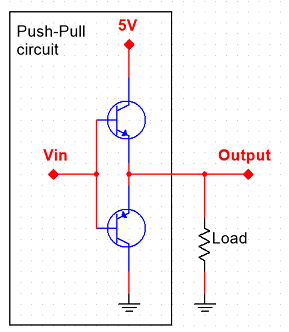

三极管推挽输出

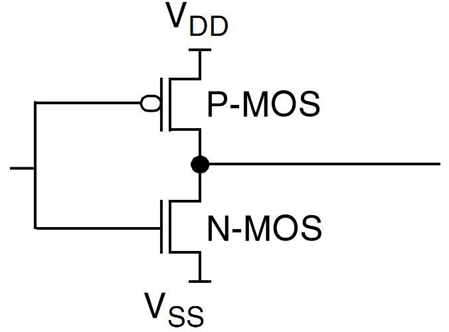

三极管推挽输出input输出高电平时,PMOS截止,NMOS导通,output=0V

input输出低电平时,PMOS导通,NMOS截止,output=VDD

MOS管推挽输出