这两天在思考,写公众号是不是一件有意义的事情。仔细思量后,结论是肯定的。做硬件的少,善于分享的更少,能表达清楚、坚持下来的更是少之又少。受众少,则不会对此有什么商业方面的太多期待。于我而言,更多的是把我的理解,我的经验分享出来。每次写文时候,总是要翻阅大量资料,尽量保证经验不只是经验,也是有迹可循有理可依的实践。往往这时候,我们常见的事情,反而并不容易说清楚。再有,每个人的知识储备有限,还是需要不断吸收学习的。因此每次选定主题就要想很久,再去深入理解,查阅资料。也导致我的更新频率非常缓慢。

尽管如此,我还是很开心可以讲给大家听。不仅是一些硬件的知识,也有自己的经历、体会、心情。毕竟这个公众号的定位是“硬件”和“日常”嘛。所以每次也都有小半个篇幅,再讲一些平日的吐槽、琐事。我也更乐于讲出这些,可能是“把自己讲出来”,比“把硬件讲出来”更加容易一些吧~那我想,公众号的平台,于我而言,也算是一种“甜蜜的负担”吧。

接下来,背景音乐响起来,一首经典儿歌“甜蜜的负担”(实际叫拨浪鼓),送给大家~

新冠在国际上势头正足,国内还好,上一波北京新发地的也被控制住了。然而端午还是怂怂的哪儿都没去,去找了小伙伴胡吃海塞了三天都没敢出门逛街。

最近又开始了各地的防汛工作,尤其是长江流域地区更甚。这里我就又禁不住要大吹特吹三峡大坝的彩虹屁了。假如没有三峡大坝,难以想象今年的洪峰该如何度过,重现98年的场景都未必不能。央视之前拍了个八集纪录片《大三峡》,立体深入地介绍了一下三峡工程。也不懂为什么网上很多无脑喷,这种功在千秋的工程,有什么好异议的?

最近认识个小哥,同是硬件类原创作者,有点惺惺相惜的感觉。他写的文章也都不错,大家可以去储备知识~而且是个高产作者,比我可勤奋多了~下边是他的一篇文章,我今天也正好想写相关内容,就一并看了吧~

去参加应聘,面试官考我OC门、OD门和推挽输出

————————

我们在日常使用芯片的时候,通常会通过平台给出的GPIO结构来实现我们想要的功能。GPIO(General-purpose input/output)通用性输入输出接口。主要为实现功能预留与平台通讯的接口,根据平台需求不同,通常电压定义也不同。在嵌入式手机平台中,通常GPIO电压为1.8V,而也有特殊为3.3V的。

我们在使用GPIO的时候,通常会注意他的一些特性,例如电压域、驱动电流、是否支持休眠唤醒,默认状态等的参数。但实际上,GPIO作为输出口时,还会有一种区别,是我们很少关注的,即输出方式是推挽还是开漏。

那我们今天就来详细说明开漏输出。

场效应管(FET)

在介绍开漏输出前,首先来简单介绍下场效应管。

场效应管(FET)通常分为结型场效应管(JFET)和绝缘栅型场效应管(IGFET),绝缘栅型场效应管因其栅极为金属铝,则又有一个被我们熟知的称呼——MOS管(Metal Oxide Semiconductor)。现代微电路中,MOS管因其稳定性好,集成简单而得到广泛应用。

MOSFET(金属氧化物半导体型场效应晶体管)

MOS管分为N沟道和P沟道两类,每一类又分为增强型和耗尽型两种。当栅源电压为零时,漏极电流为零的管子为增强型,而漏极电流不为零的则为耗尽型。本文只讨论增强型MOSFET,对耗尽型不做过多讨论。

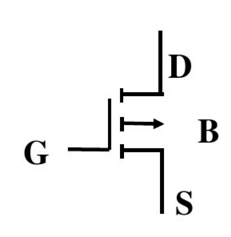

图1和图2分别为N沟道增强型MOS和P沟道增强型MOS。MOS管有三个极,分别为G(gate)栅极、S(Sourse)源极以及D(Drain)漏极。N-MOS相当于三极管的NPN管,即源漏两极为N端,栅极为P端,P-MOS相当于三极管的PNP管,源漏两极为P端,栅极为N端。

图1 N沟道增强型MOS管

图2 P沟道增强型MOS管

栅极又被称为门极,很形象,栅极就像一个开关一样。当控制开关打开时候,DS导通,当控制开关关闭时候,DS断开。MOS管是一个电压驱动的器件。对N-MOS管来讲,当Vgs>Vgsth时,即大于管子的导通电压时,或者说,G端电压高于S端电压一定程度后,管子导通,Vd=Vs。当Vgs

对P-MOS管来讲,当Vsg>Vsgth时,即大于管子的导通电压时,或者说,S端电压高于G端电压一定程度后,管子导通,Vd=Vs。当Vsg

开漏输出(Open-Drain)

下面进入我们的正题,开漏输出,即OD门电路。

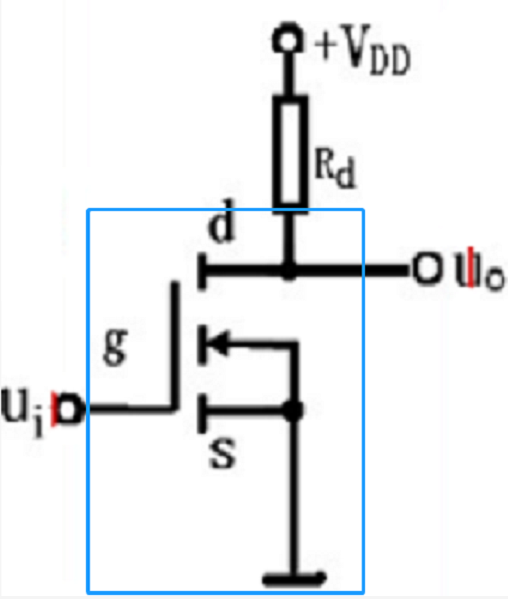

开漏输出是基于MOS管,开放漏极的一种电路结构。图3为典型的开漏输出电路。

图3 开漏输出电路

电路分析

如上图,开放漏极是指,漏极电压VDD为外部供给。即蓝框内的为芯片集成,上拉电压VDD则需要自己外接。当Ui大于一定值(Vgsth)时,即逻辑1,MOS管导通,VS=VD,即此时Uo输出电压=Vs=0;当Ui=0时(或小于Vgsth),即逻辑0,则管子不导通,Uo处于悬空状态。此时若外接电压VDD,则Uo=VDD电压。

特点

由此电路可以看出开漏输出的几个特点:

开漏输出需要外接上拉电阻

开漏输出本身是不带高电平的,若想要输出为高,需要外接上拉电阻才能输出高电平。常用的I2C电路为典型的开漏输出电路。

开漏输出输出高电压较为灵活

由于本身不带高电压输出能力,因此外接VDD是多少,就能输出多少的高电压,这使电路变得更加灵活。在实际应用中,我们若想将两个不同等级的电压芯片相连,不妨使用开漏电路来完成电平转换

开漏输出所需要的驱动电流较小

前文介绍MOS管是就说过,MOS管是一种电压驱动型器件,即门极的开关条件取决于电压的高低,而对开启的电流的要求几乎没有,因此管子导通时,栅极所需的驱动电流很小,损耗很少。

与之相对应的是三极管的开集电路(Open-Collector),即OC门电路。前文提到,N-MOS管与三极管的NPN管相对应,P-MOS管与三极管的PNP管相对应。三极管电路中也存在类似电路,即开集电路。不同的是,三极管是一种电流驱动型的管子,因此,三极管导通,需要基极电流达到一定程度才能导通,饱和导通则需更高驱动电流。

综上,若非放大电路,在实际接口电路中,由MOS管为基础的开漏电路要比三极管的开集电路应用更广泛。

开漏输出可作为反相器使用

分析电路我们可以看出,当输入为0时,输出为1;当输入为1时,输出为0。因此可以作为反相器应用在电路中。

开漏输出可以作为“与非门”使用

与非门是一个逻辑门电路,它的逻辑关系为,假设输入为ABCD任意多个,其中任意一个输入为1,则输出为0;当所有输入均为0,则输出为1。

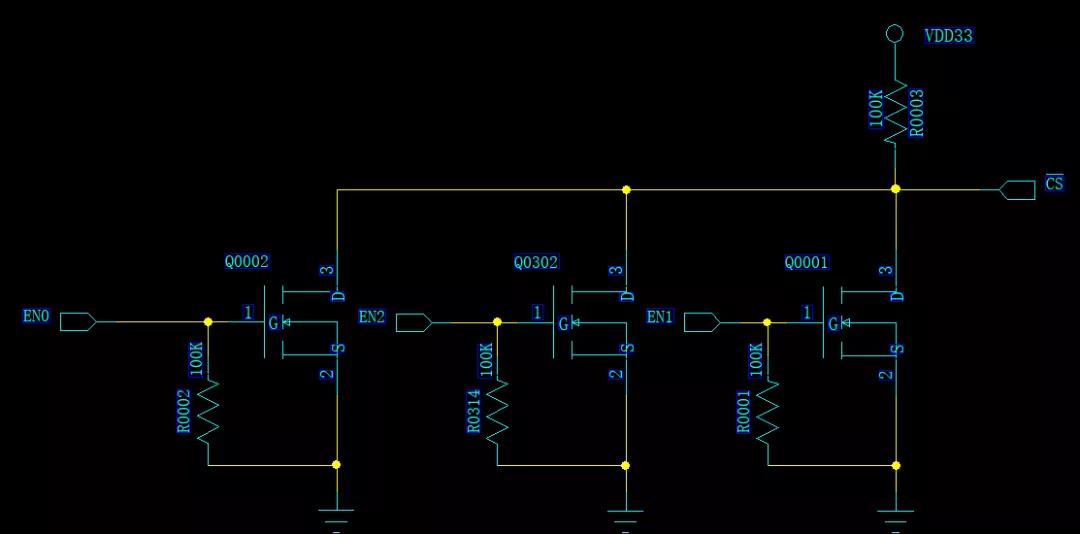

我们可以通过并联多路开漏电路,来完成与非门的功能。

下图为一个与非门功能实例。

图4 开漏电路作与非门

使能信号EN0、EN1、EN2三路信号,任意一路信号为逻辑1,则片选信号CS为0;任意一路信号为0,则片选信号CS为上拉电压3.3V。另外,输入信号EN0,EN1,EN2并不要求电平相同,只要他们的逻辑1的电平值高于该MOS的开启电压Vgsth即可,因此应用也很灵活。

当然,这只是电路的一种应用形式,这里并非说这种与非门的实现形式为最佳方案,但它确实是一种实现形式。

开漏输出的高电平上升沿触发慢

这是开漏输出的一个不足。由于开漏输出自身没有高电平输出能力,需要外接上拉电阻,因此就导致了,当输出高电平时,实际上是外接的VDD提供的高电平电压。这时候上拉电阻Rd的选取就很关键。当Rd过大时,若负载为非纯阻性负载,则上升时间非常缓慢;Rd太小,则又会使电路的静态电流过大,导致静态功耗偏大。

因此,若是可以选择,我们可以让后级电路用下降沿触发,避免上升沿引入的诸多尴尬问题。若是不能选择,则需要平衡静态功耗和速率之间的矛盾关系。

开漏输出的原理和应用大致介绍完成。在实际应用中,用MOS管做开关电路实在是太常见了,因此对开漏输出的理解也需要更深刻全面。

那么还有另外一种输出方式——推挽输出,我们等下一次详细说明。