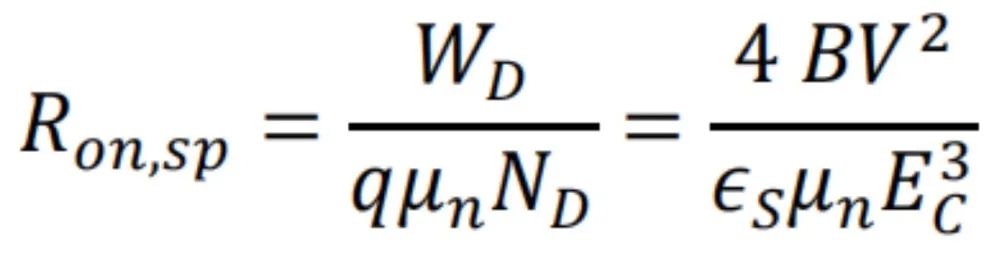

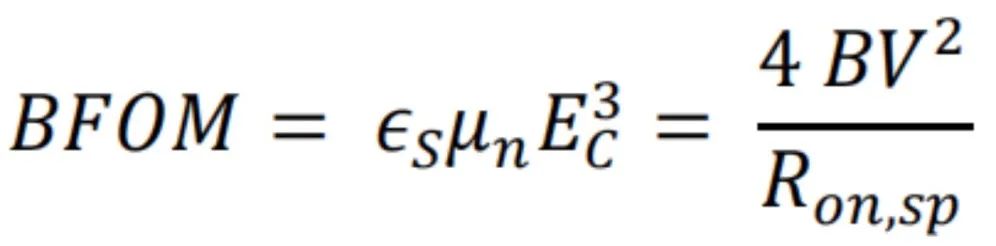

理想比导通电阻的一个关系式,其中WD是满足所需击穿电压BV的漂移区的厚度,q是电子电荷,ND是漂移区的掺杂浓度,μn是电子迁移率,εn是半导体介电常数,EC是所需耐压的临界电场值。

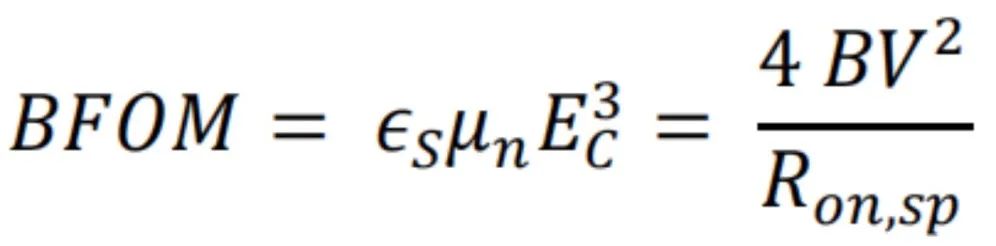

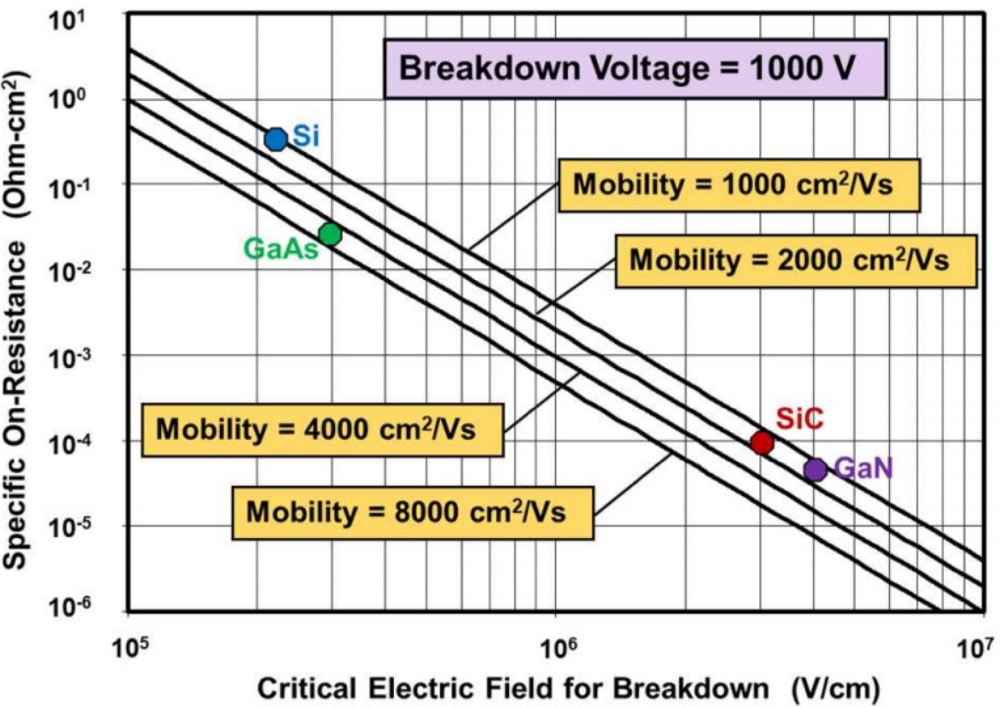

也就是我们常说的Baliga优值,由于每种半导体材料的击穿临界电场是随击穿电压而变的,所以BFOM适合在相同的BV条件下比较不同的半导体材料。下图是基于击穿临界电场的各个半导体材料的比导通电阻的比较:

我们可以看出,使用较大的Ec能够显著地减小,这是为什么碳化硅(Ec近硅基10倍)快速发展的主要原因之一。

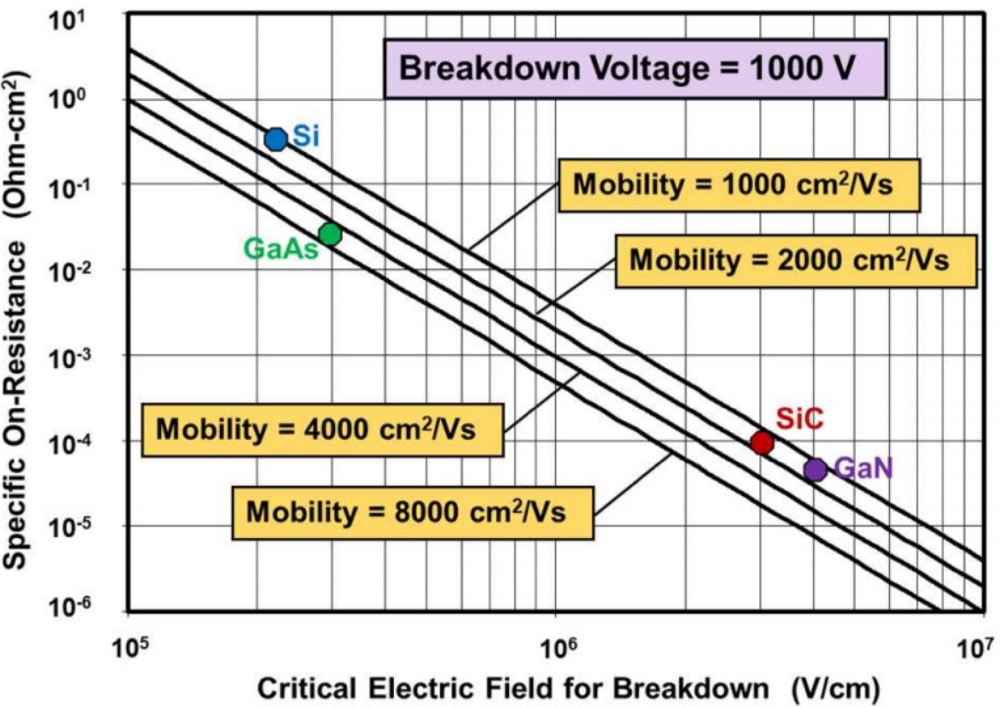

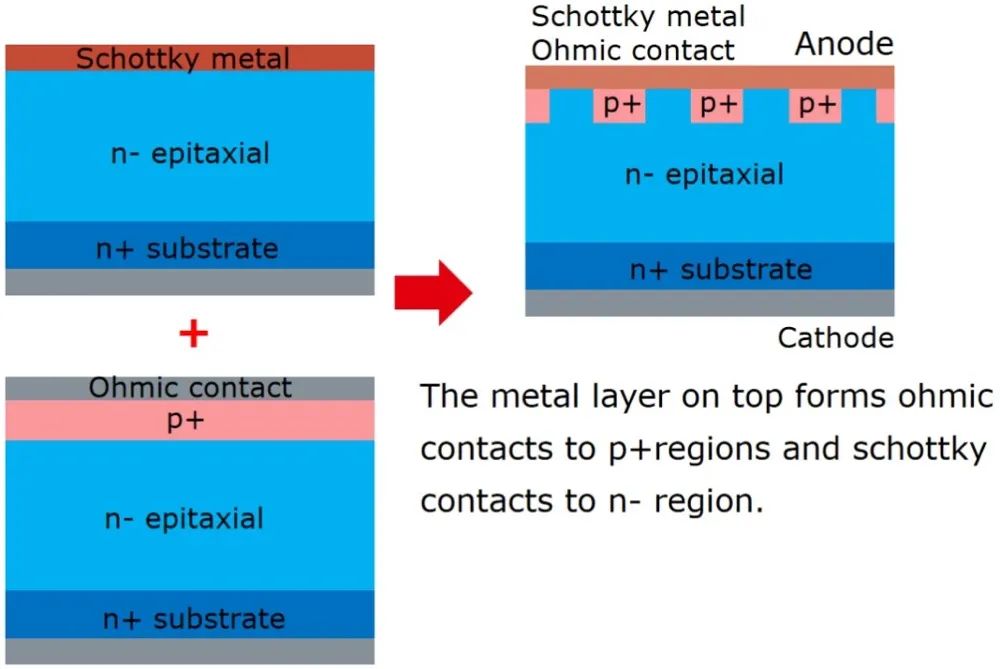

最初碳化硅应用的目标场景是在航空航天、国防和高温应用,这也推动了20世纪90年代更大直径和更低微管密度的碳化硅晶圆的发展,同时也得到了足够的资金支持。碳化硅经过这些年的沉淀,如今在各个应用基本都能看到它的身影,以后只会更盛,只是需要足够的时间。在20世纪80年代,通用电气发明IGBT和商业化不久,硅基二极管的反向恢复行为不佳便成为了电机控制等领域的主要障碍,估计整流桥中的大反向恢复电流,IGBT搭配应用中的显著损耗等。后来也出现了硅基肖特基二极管,但由于漂移区的电阻较高,反向阻塞时的漏电流很高,限制了其耐压不适合超过300V。所以使用碳化硅取代硅,能够将漂移区电阻降低1000倍,这为制造碳化硅肖特基二极管提供了强大动力。第一个400V的碳化硅肖特基是基于6H-SiC的,与硅基PiN二极管相比,其导通压降约为1.1V,没有反向恢复电流。与硅基相比,由于金属-半导体界面的电场大得多,碳化硅肖特基势垒降低的效果要差很多;同时由于漂移区的掺杂浓度较大,从而产生了较强的隧穿诱导电流。这两者都导致了泄漏电流的大量增加。幸运的是,这个问题有一个很好的解决方案,早前被称为"pitch-rectifier"应用到硅基肖特基上,后来被成为结势垒肖特基(JBS),依赖于肖特基接触下方的PN结。

早在1998年就出现了基于4H-SiC的JBD二极管,2005年1.2kV的商业化,由于光伏储能等应用的需求,1.7kV与2015年发布,同时3.3kV的SiC肖特基二极管也被开发。开发更高耐压的肖特基二极管将带来更多应用上的优化,比如应用于微电网中的10kV肖特基二极管。广泛用于制造硅基MOSFET的双扩散工艺不太适合碳化硅,主要是因为在多晶硅栅极能够承受的温度下,N和P型掺杂剂的扩散系数太低,所以一般采用的是离子注入工艺,这种方法在1997年首次用于6H-SiC的MOSFET。

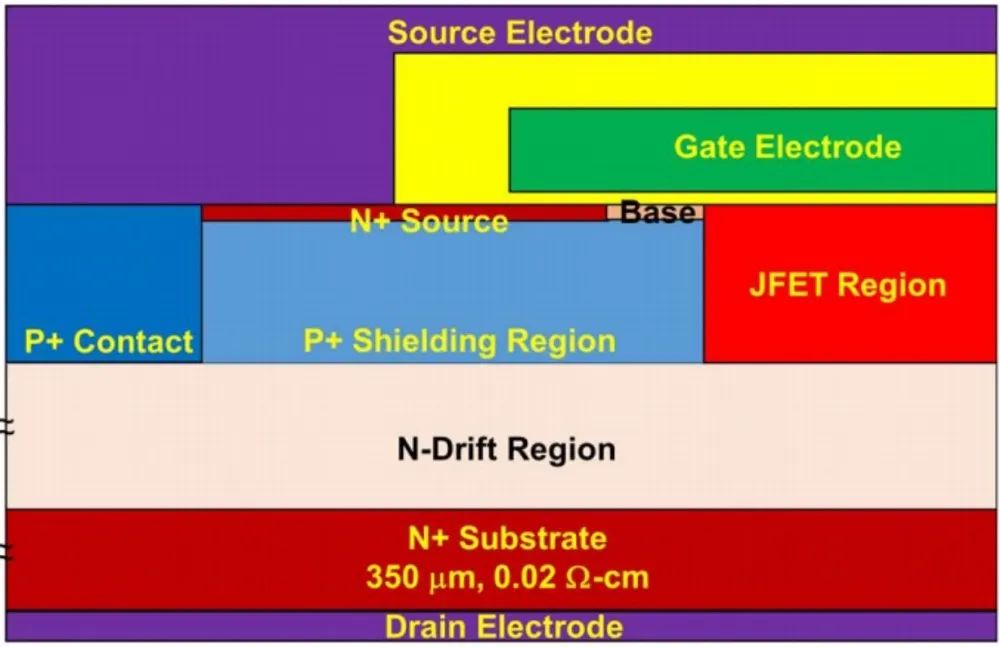

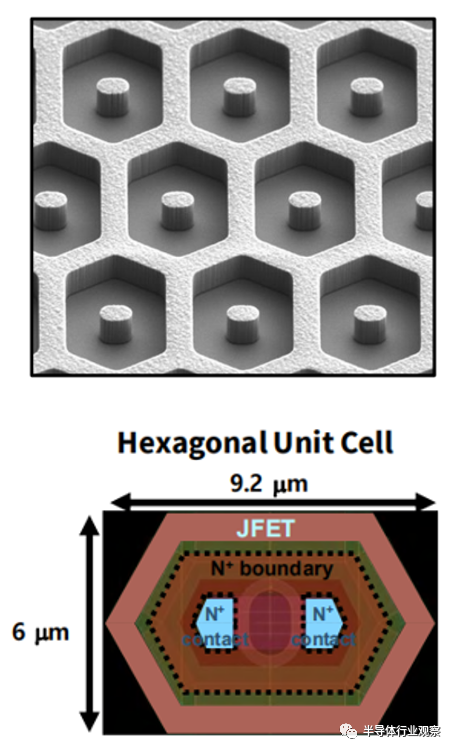

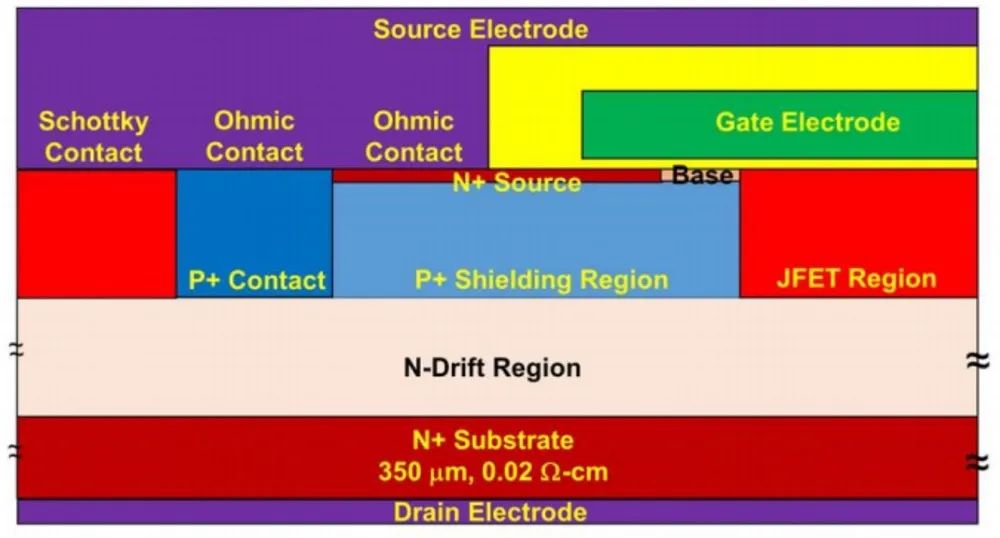

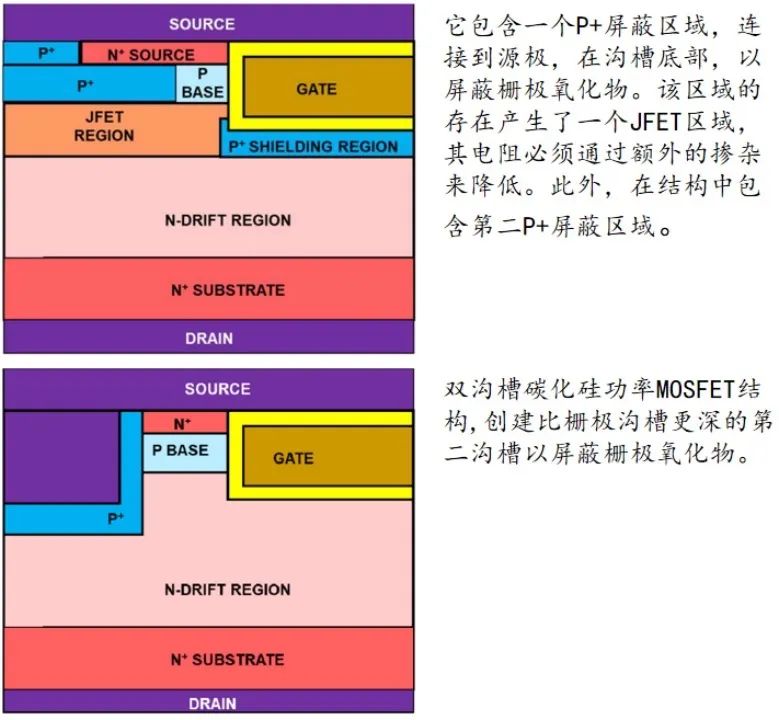

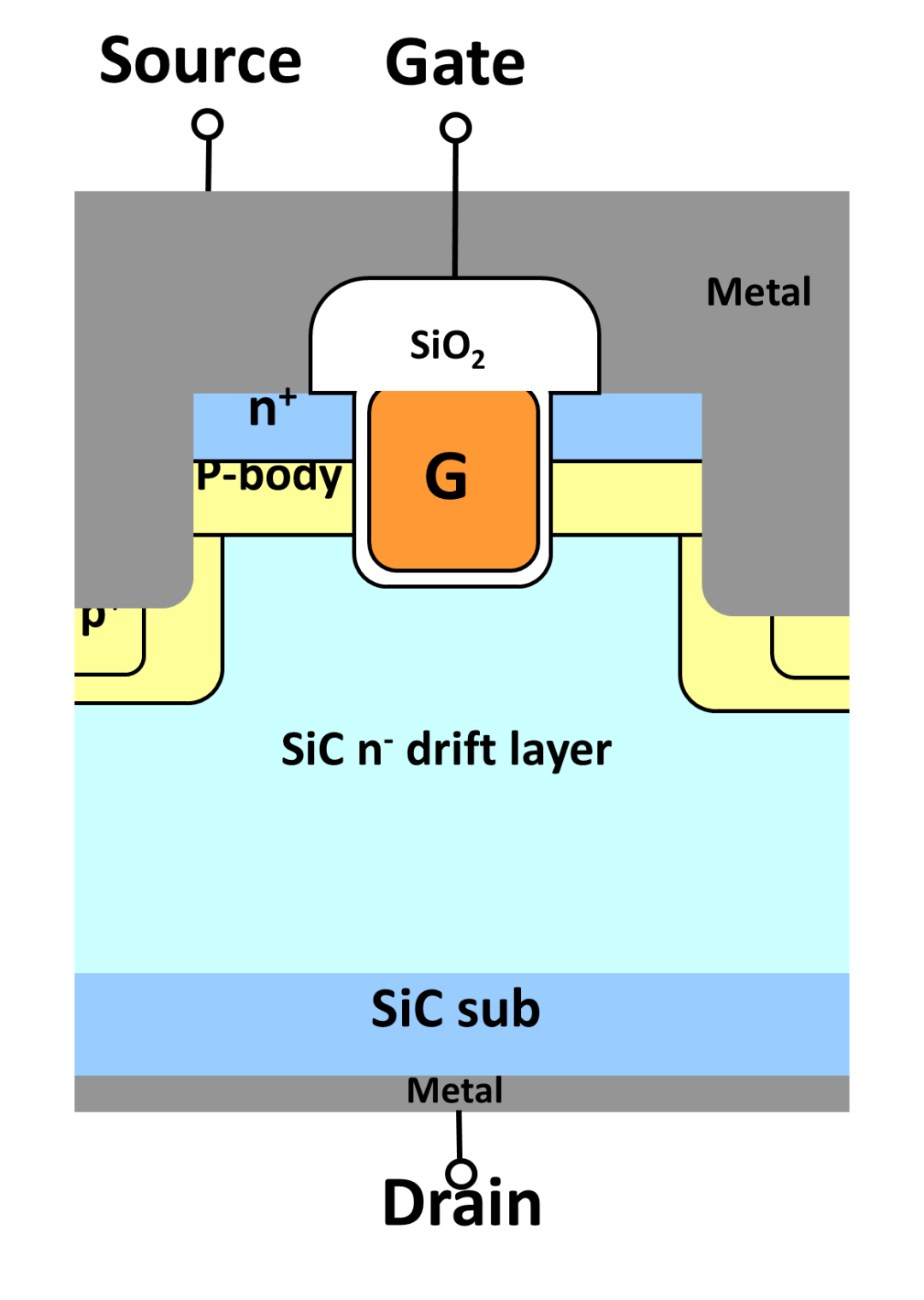

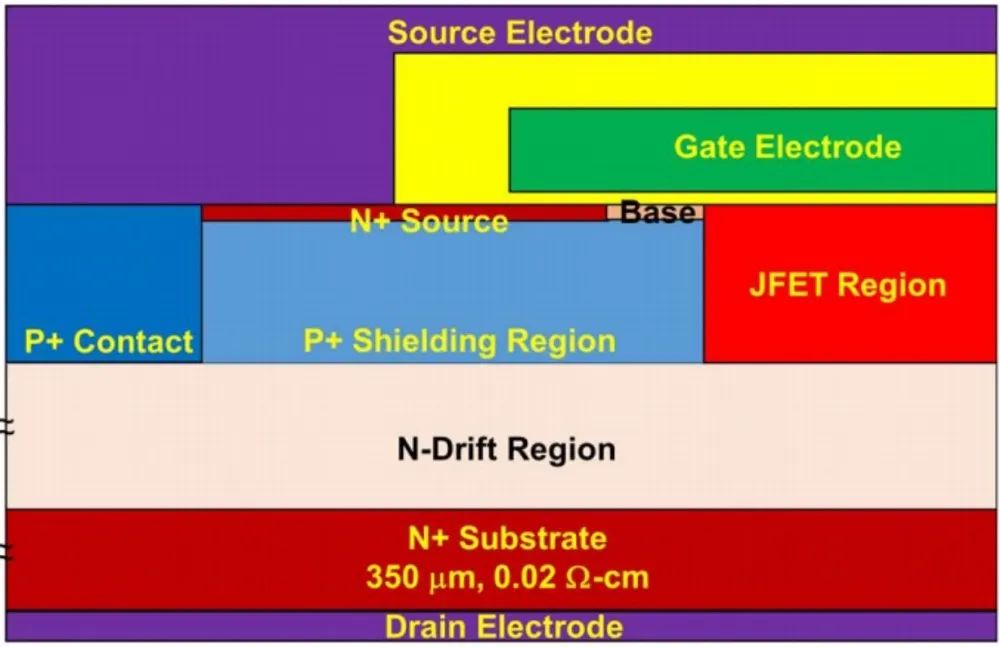

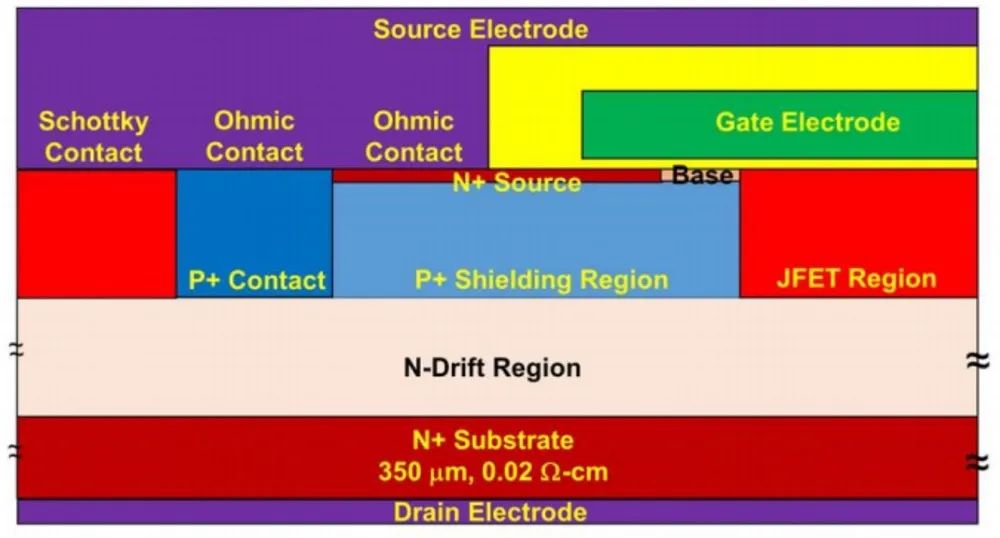

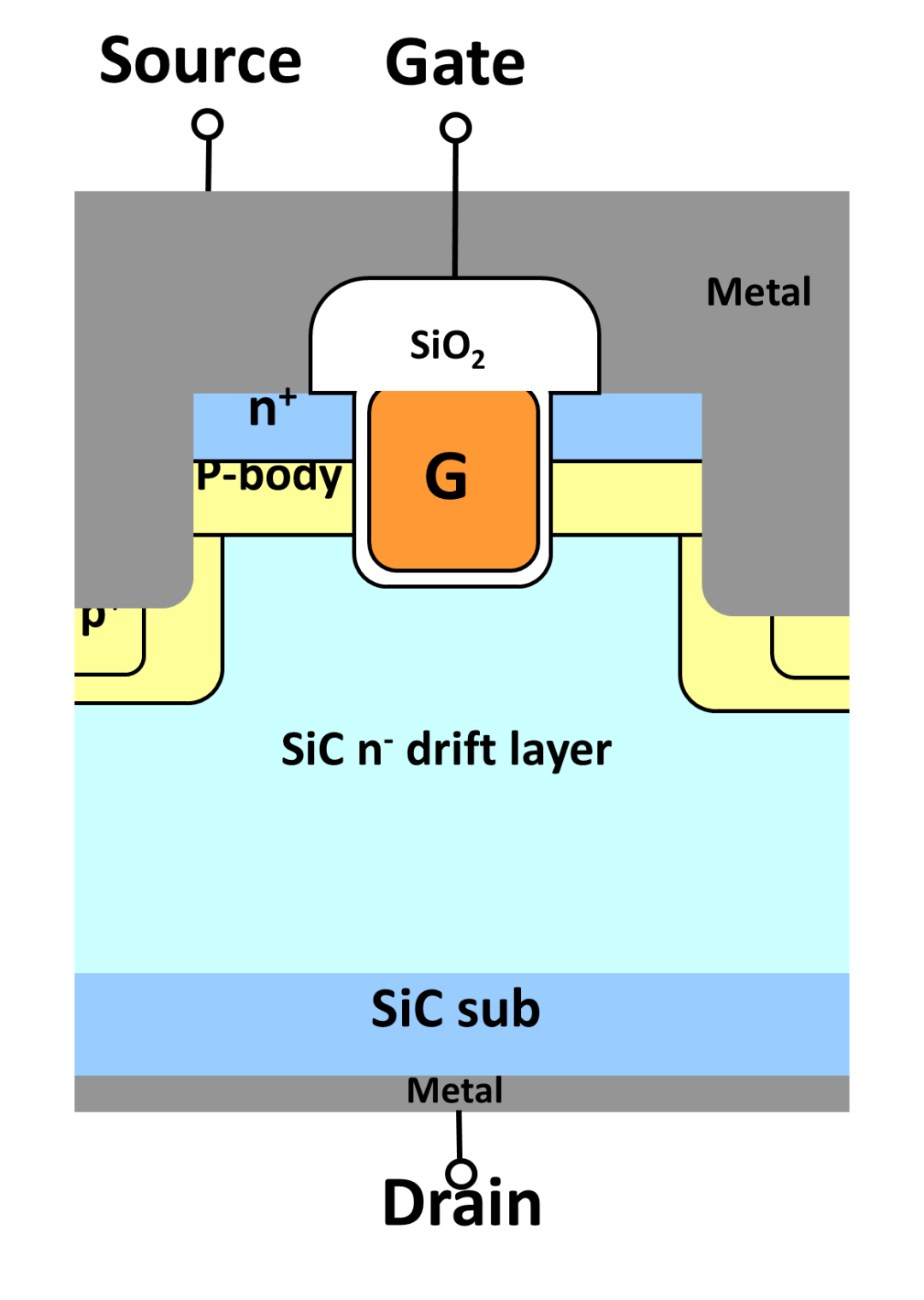

其中包含了P+屏蔽区域,旨在减少氧化物中的电场,在没有P+屏蔽区时,电场的大穿透导致了有限的击穿电压,除非使用较长的通道。在高压阻塞状态下,碳化硅漂移区的大电场会引起栅极氧化物的可靠性问题,P+屏蔽区在JFET区域产生了一个势垒,从而降低了氧化物附近的电场,使其保持在3MV/cm以下,以确保其可靠性。在碳化硅功率MOSFET中优化JFET区域的宽度,能够减少比导通电阻,还能够抑制栅极氧化物中的电场。目前,国内外主流的碳化硅产品多数为平面型,以碳化硅行业龙头Wolfspeed的碳化硅MOSFET产品为例,目前出货产品也处于第3代(Gen 3),涵盖650V到1200V之间的多个电压规格。与之前两代产品相比,WolfspeedGen 3 平面MOSFET采用六边形晶胞微观设计,650V Gen 3和1200V Gen 3+的单位面积导通电阻分别为2.3 mΩ·cm2和2.7 mΩ·cm2,较上一代Strip Cell减少了16%。Wolfspeed Gen 3碳化硅MOSFET采用Hex Cell的平面技术最初提出在碳化硅MOSFET中通过体二极管来进行第三象限的电流流动,但由于双极性退化的原因,导致了MOSFET特性的退化。主要是双极电流传输引起的基面位错产生的堆叠引起的。可以通过并联一个碳化硅二极管来绕过双极性的体二极管,但这相当于额外的增加了一个器件,所以提出了MOSFET集成JBS二极管的方案,即JBSFET。

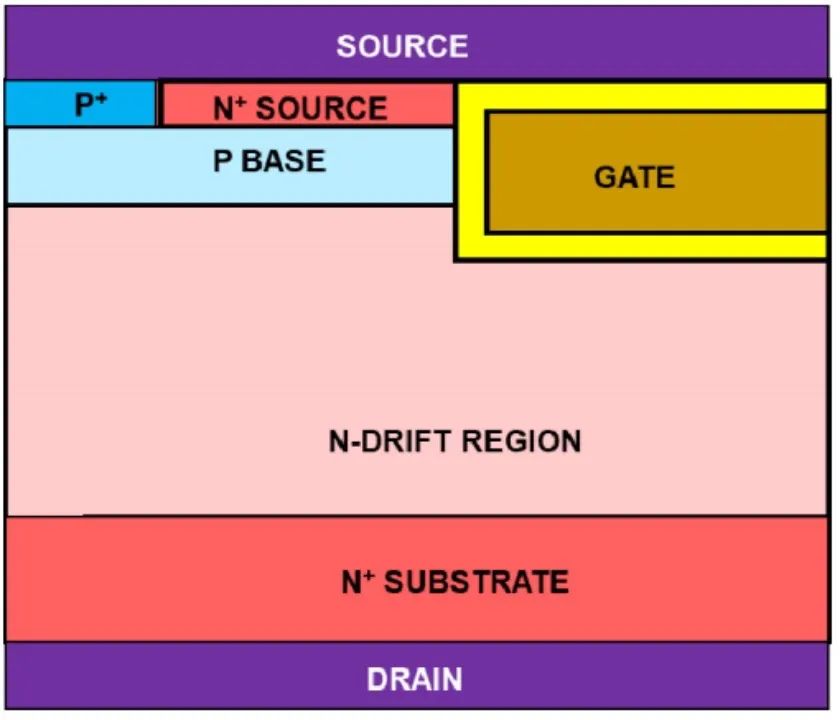

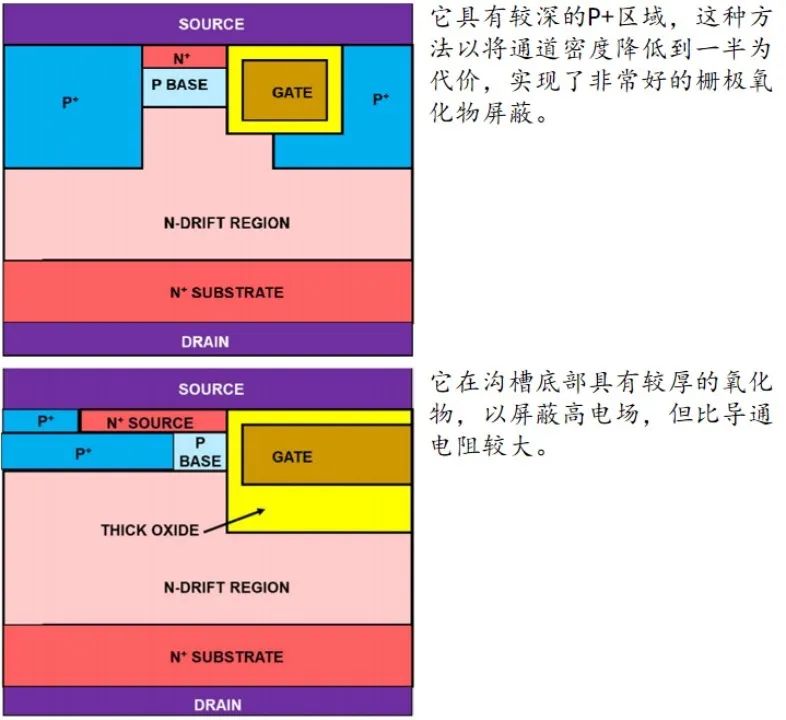

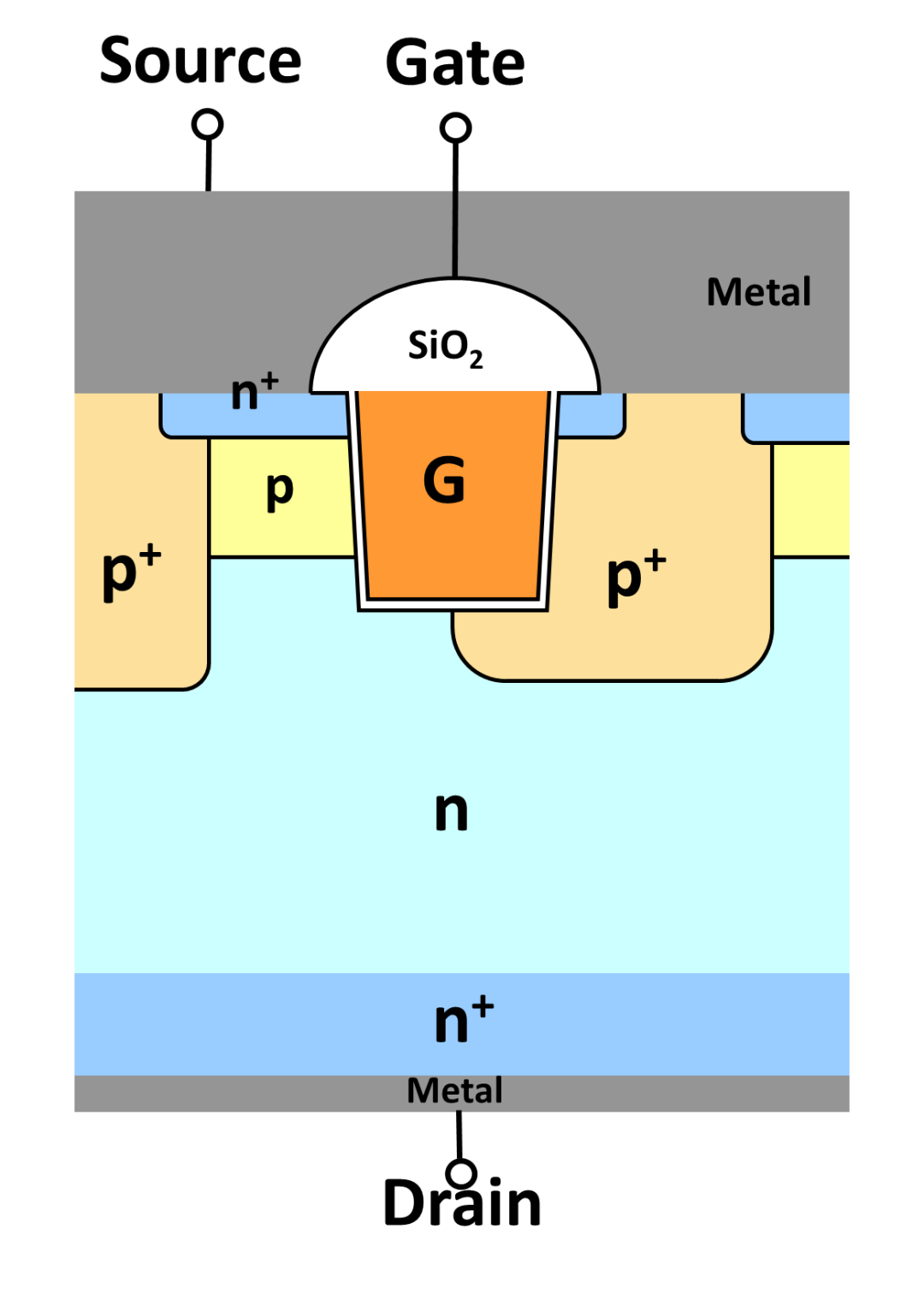

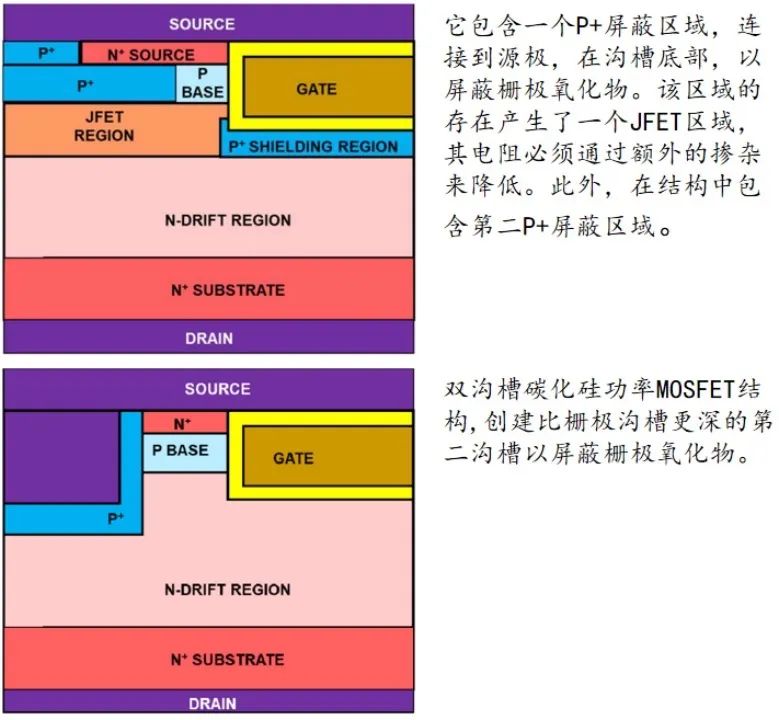

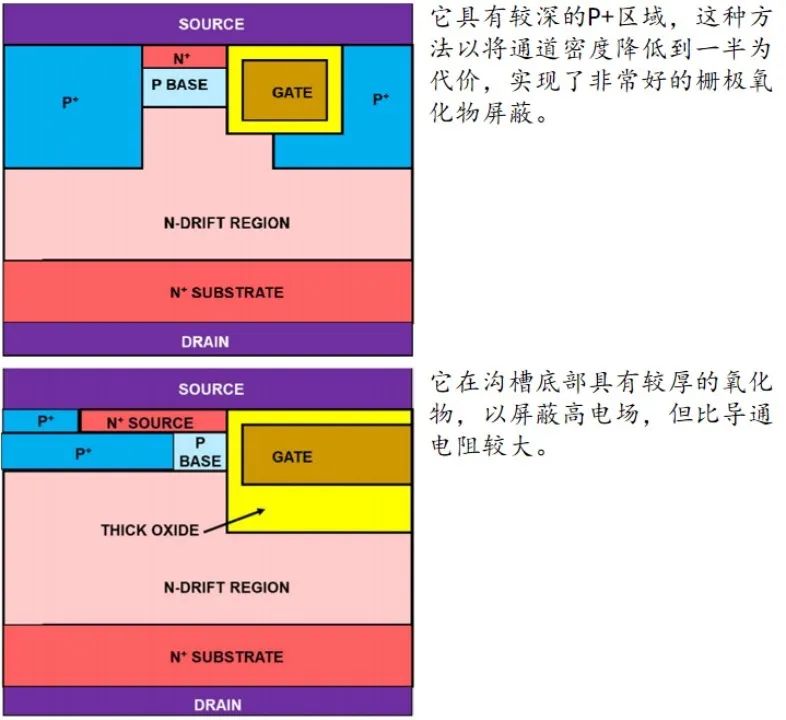

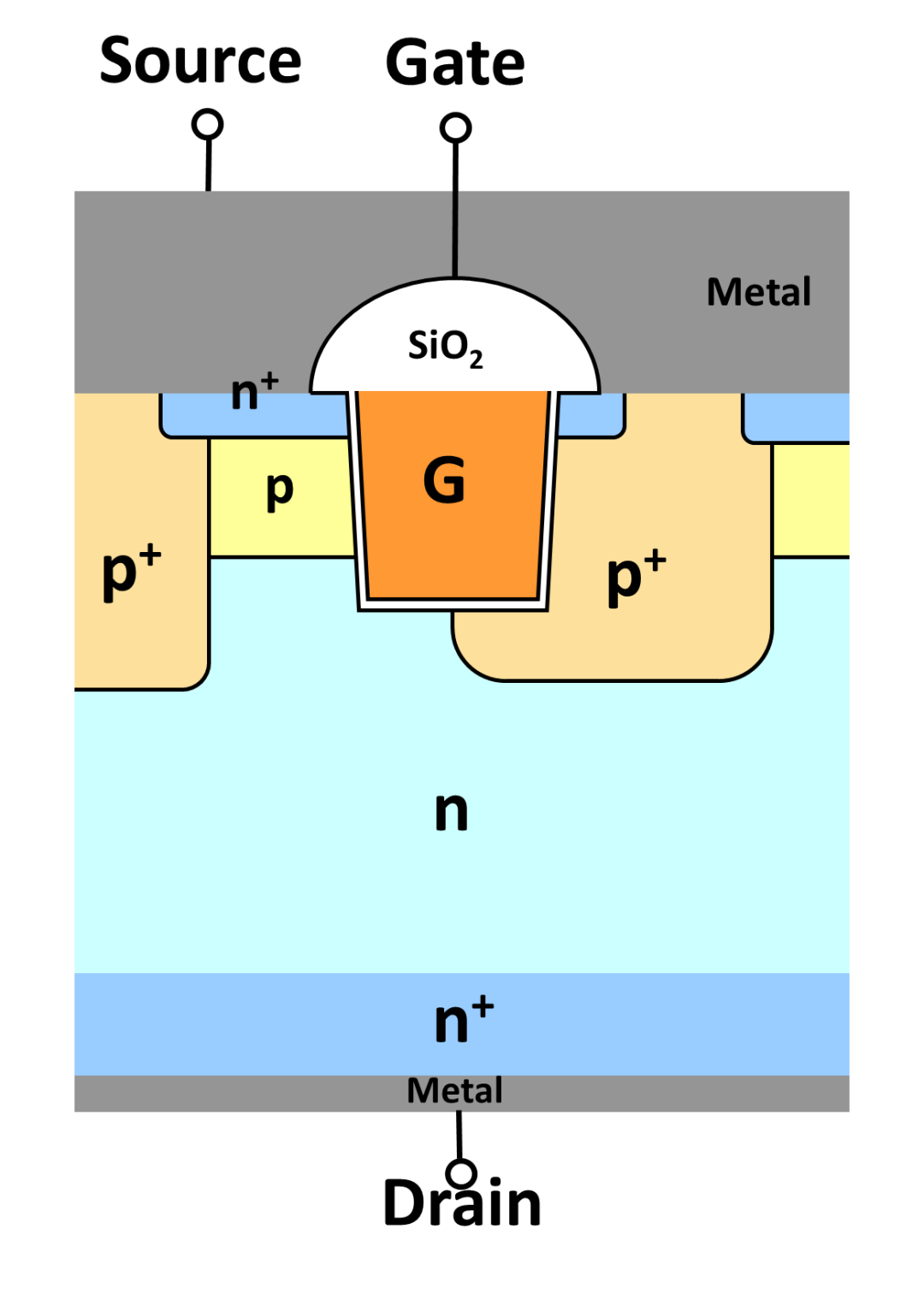

此外,由于JBS具有较小的通道密度,它比MOSFET具有更高的短路耐受能力。硅基的平面栅到沟槽栅,我们可以在碳化硅中看到平面栅和沟槽栅,但由于一些原因,目前只有部分厂家推出了沟槽栅碳化硅MOSFET。下图是沟槽栅MOSFET的示意结构图:但这个结构并不适合碳化硅MOSFET,首先,在阻塞状态下,在沟槽底部会形成非常大的电场,对于栅极氧化物造成较大的威胁。其次,除非使用非常宽的P基区,否则在P基区的耗尽层穿透会使通道电阻非常大。为了应对上述问题,多种沟槽栅的方案被提出。

从产品推进看,2020 年罗姆推出了针对电动汽车优化的第 4 代 1200V碳化硅MOSFET,第4代产品获得了更好的FOM(品质因数,Figure of Merit)。2023年罗姆的第四代碳化硅产品开始在客户端放量,产品质量与性能得到客户认可。

ROHM双沟槽MOSFET结构

该结构同时具有源极沟槽和栅极沟槽

除此之外,英飞凌的半包沟槽结构也是业界不多的几个能够量产上车的碳化硅沟槽结构设计。按照公众号“碳化硅芯片学习笔记”作者的说法,“沟槽MOS成套工艺及结构IP,是未来十年碳化硅竞争的入场券!”

英飞凌CoolSiC™ MOSFET采用了不对称的沟槽结构,该结构中MOS沟道选择了最有利的方向。从图中看到,参杂毗邻沟槽中的区域是不对称的,沟槽的左侧壁包含了MOS沟道,它被对准到a-plane面,以实现最佳的沟道迁移率。

长远来看,碳化硅MOSFET的发展以降低成本,降低导通电阻,提高可靠性为主,同时往更高的电压等级发展,未来还有更高耐压的碳化硅IGBT产品结构待攻克。

当然目前应用最多的,依旧是650V~1700V或者2200V耐压的碳化硅器件,主要集中于新能源汽车,光伏储能等这些各大厂家深耕的领域。但目前这些领域的主要供应商仍以海外大厂为主,国产仍需要在未来一段时间内奋力追赶。

袁隆平爷爷说,人就像一颗种子,要做一颗好种子。

我看碳化硅芯片也一样,碳化硅芯片这颗种子只有种在系统里,长在具体的应用中,长期的使用,才能看出这颗种子的好坏。

Wolfspeed联合创始人John Palmour博士也曾在采访中表示:“客户并不关心碳化硅芯片结构是平面MOSFET还是沟槽MOSFET,重要的是应用时满足特定的导通电阻需求。事实上,我们也不在乎哪种技术路线,我们只关注哪种设计能给客户带来最大的利益。”在这个背景下,我们认为只有下游真的大规模使用并且用好碳化硅,提升整体系统效率,才会向上推动芯片产品迭代,进一步优化产能及成本。这才是助推碳化硅产业链起飞的真正关键。

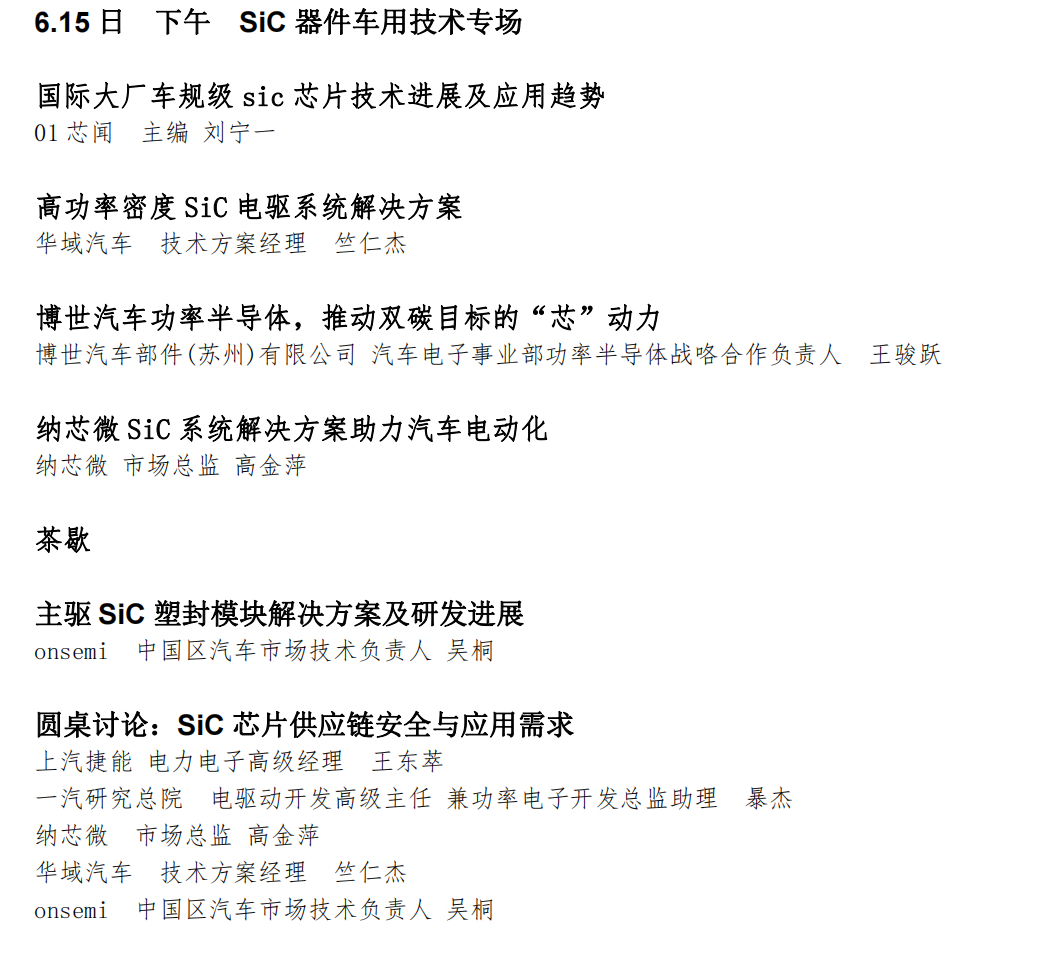

6月15-16日 我们在江苏·无锡举办 2023 碳化硅器件应用与测试技术大会,会议将分为两个应用专场展开,重点聚焦碳化硅产品在光储系统及车用主驱产品中的当前的应用进展及技术要求。诚挚邀请各位行业同仁出席!

今天分享的这篇文章主要内容来自B. Jayant Baliga,半导体元老的"Silicon Carbide Power Devices: Progress and Future Outlook"