作者:AMD intern Zhang Guanghao

文章来源:AMD Xilinx开发者社区

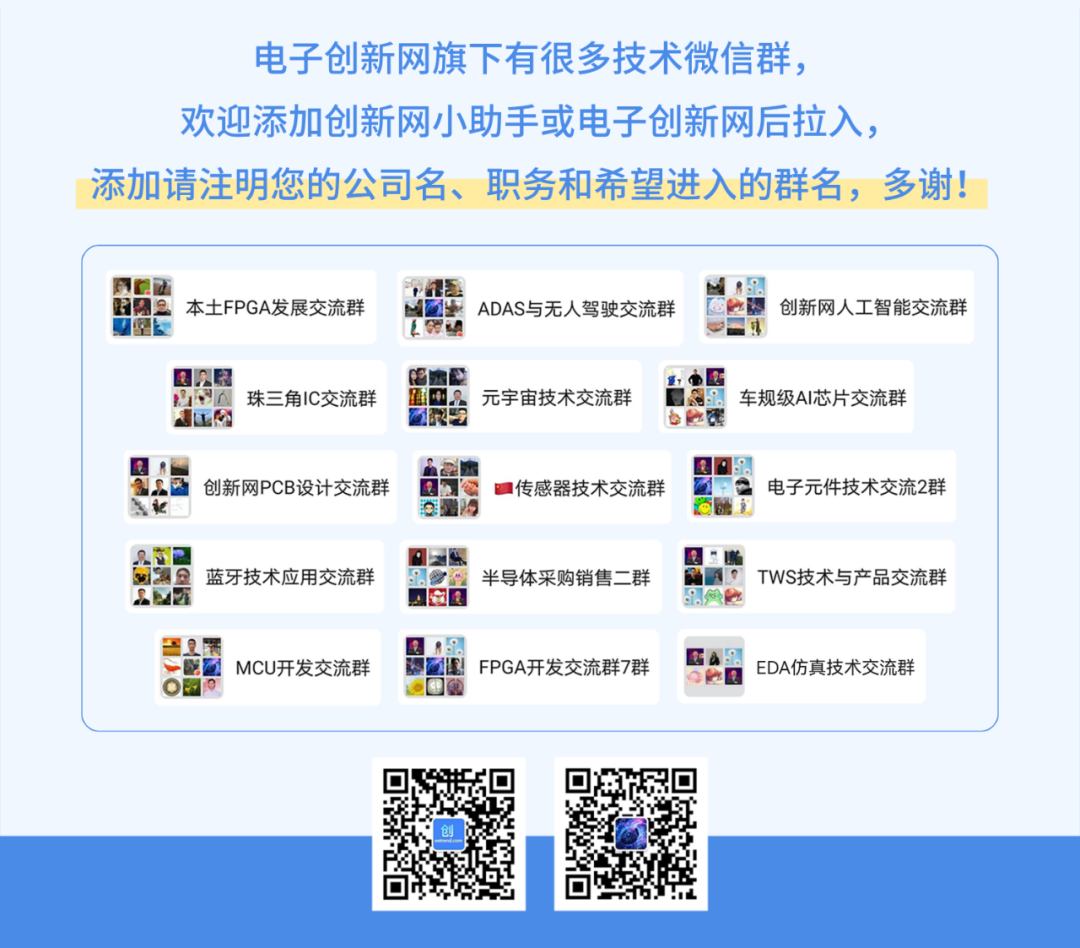

Multi-Scaler是一个用于图像缩放的视频处理IP核,支持最多8路输出,使用Memory接口,从源缓冲区读取图像,在H和V域进行缩放后写入到目的缓冲区,源端的缓地址和目的端缓存地址可以动态的更改,输出完成之后会产生一个中断信号。IP的配置界面如图:

此示例提供了一个Multi-Scaler的典型用法,测试程序将在缩放前读取目的缓冲区,然后将指定图像写入源缓冲区,并且将用户提供的参数载入到硬件寄存器中并启动IP。Multi-Scaler读取源缓冲区的图像进行缩放后写入目的缓冲区,当所有的输出都完成后Multi-Scaler会产生一个中断信号,这会调用中断处理程序去读取目的缓冲区的内容并验证数据是否正确。

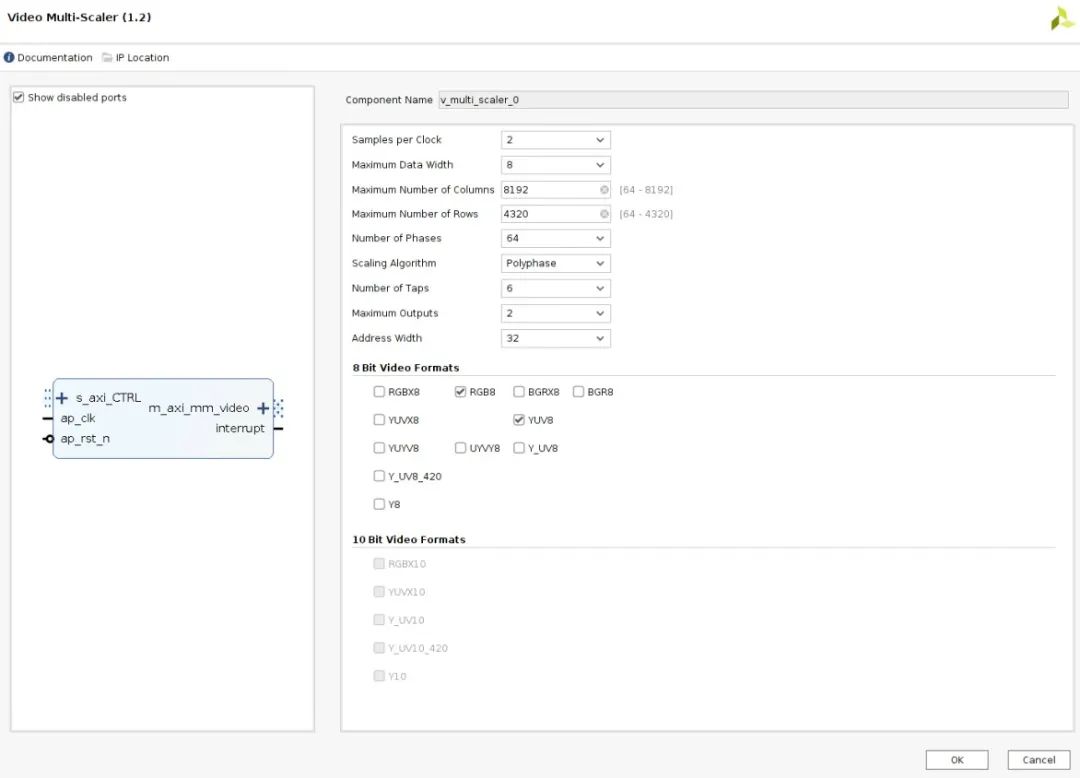

此示例支持的平台如图所示:

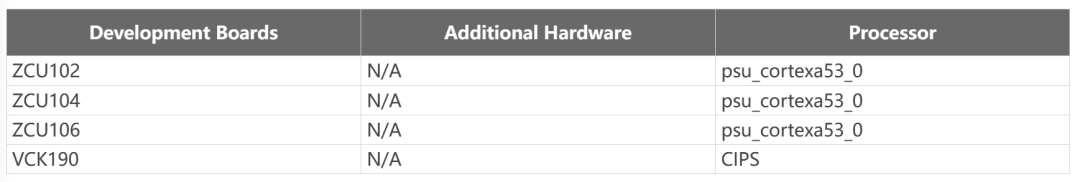

首先建立一个工程,这个工程用来打开example工程,这里我使用ZCU102评估版。

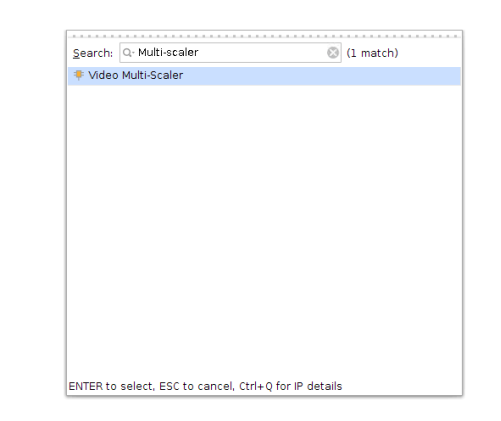

建立好工程后创建一个block design,添加Multi-Scaler IP。

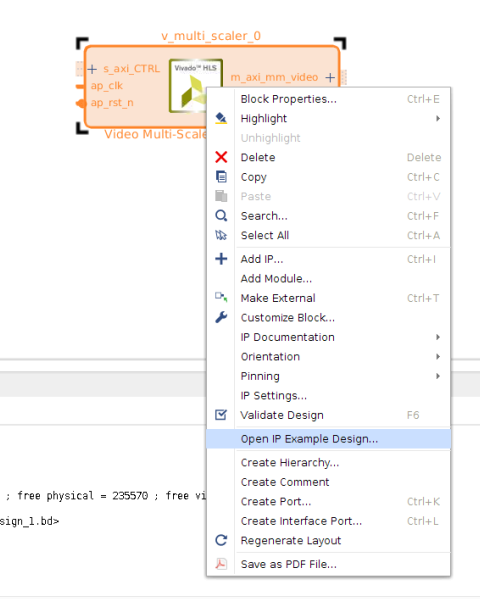

右击Multi-Scaler IP,选择Open IP Example Design

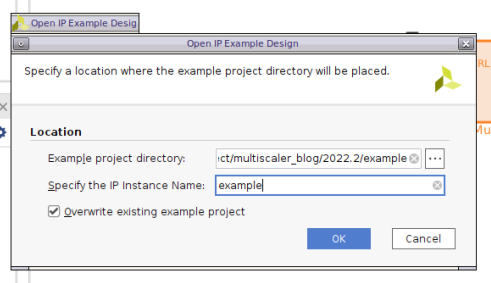

选择Example工程的路径和例化名称,Vivado会自动生成一个新的工程

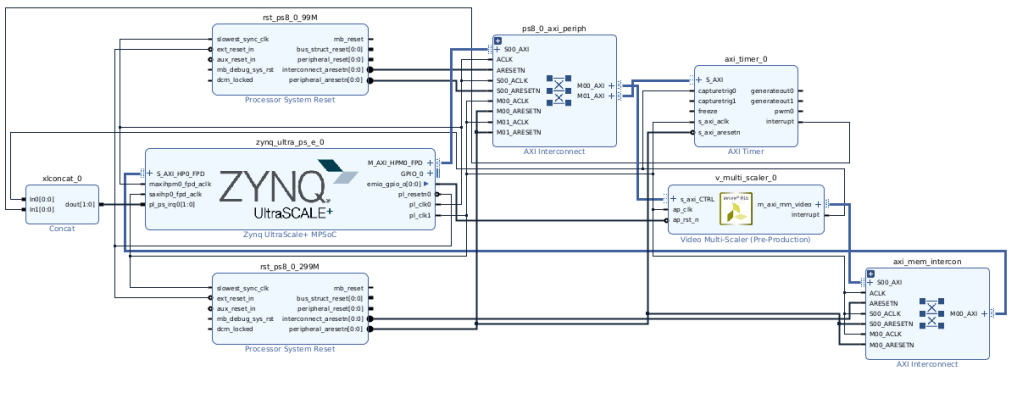

打开后的Example工程如图所示

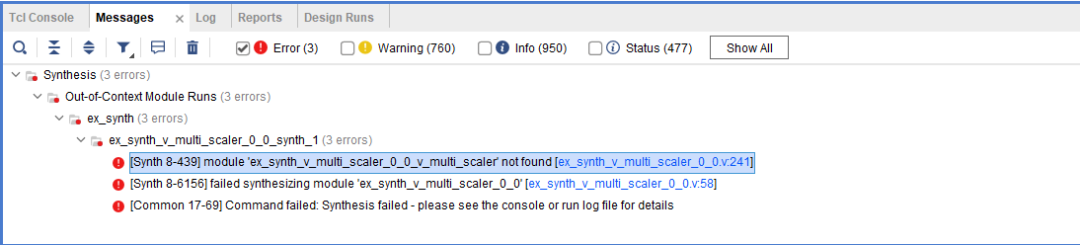

直接进行综合、实现、生成bit流文件,这个过程会花费大量时间。

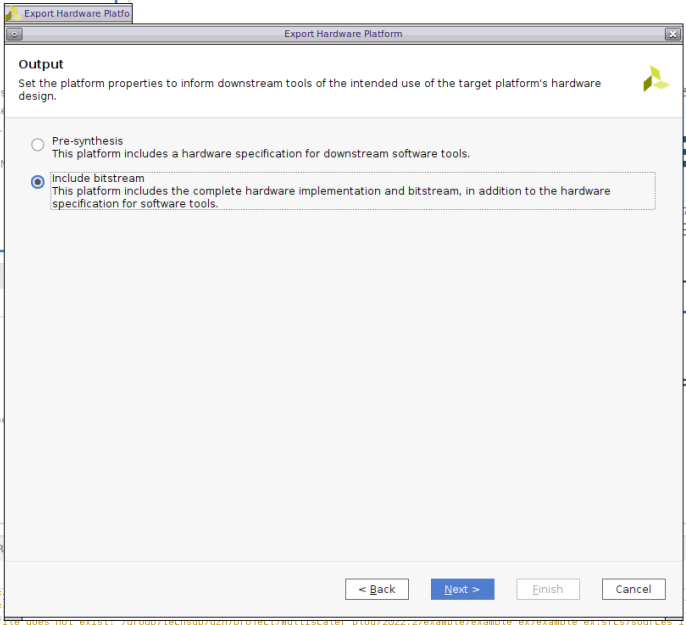

成功后导出包含bit流的hardware

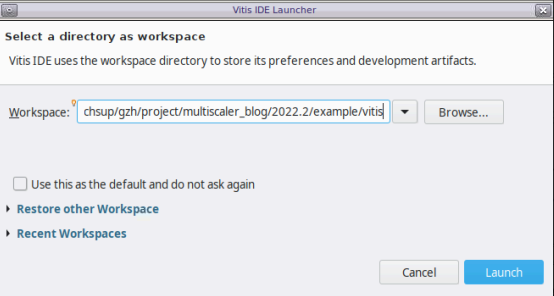

到此硬件部分已经完成,打开Vitis进行软件部分的设计,选择工作路径。

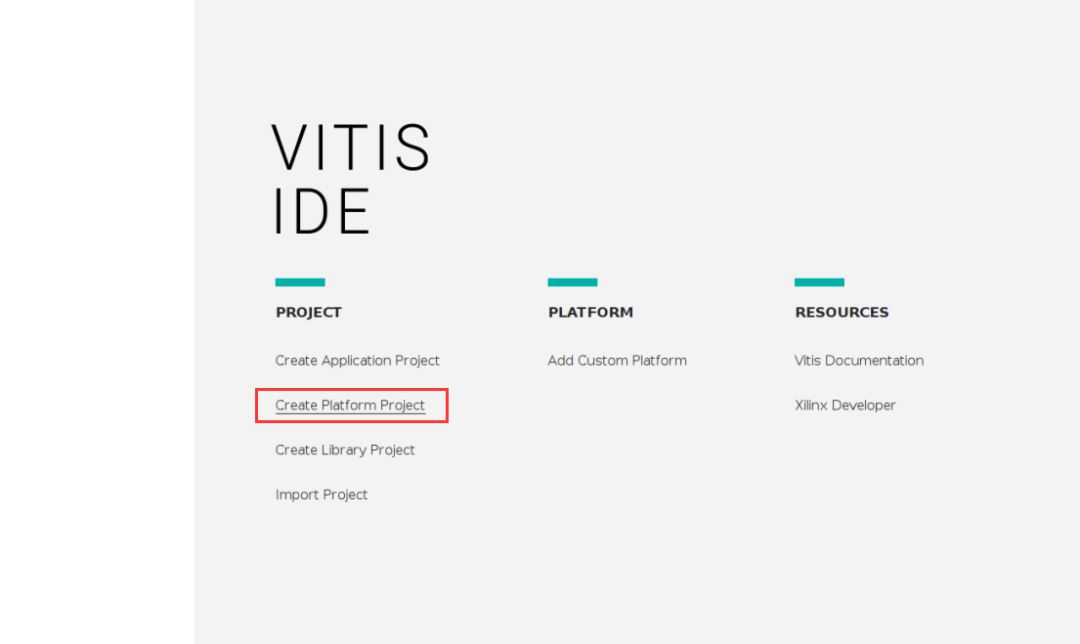

建立一个Platform工程

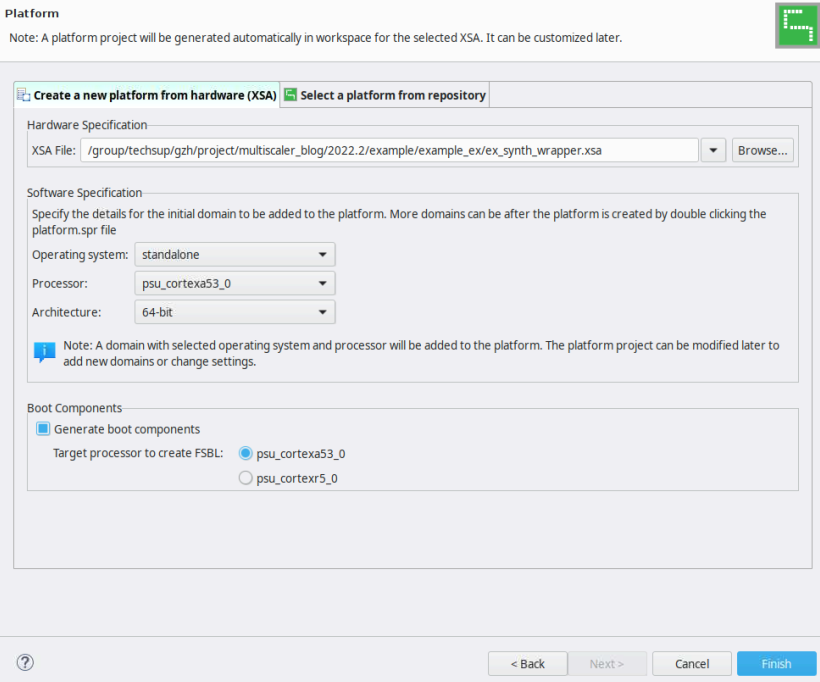

填写工程名称后选择刚才生成的XSA文件,vitis会解析我们的硬件文件。

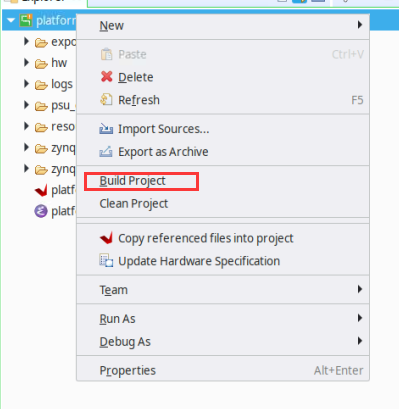

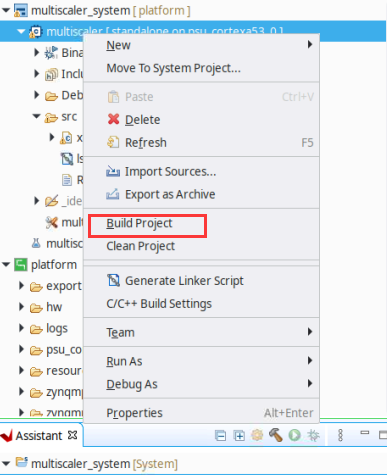

完成工程的创建后,右击platform工程,点击build project。

Build成功后再新建一个application project

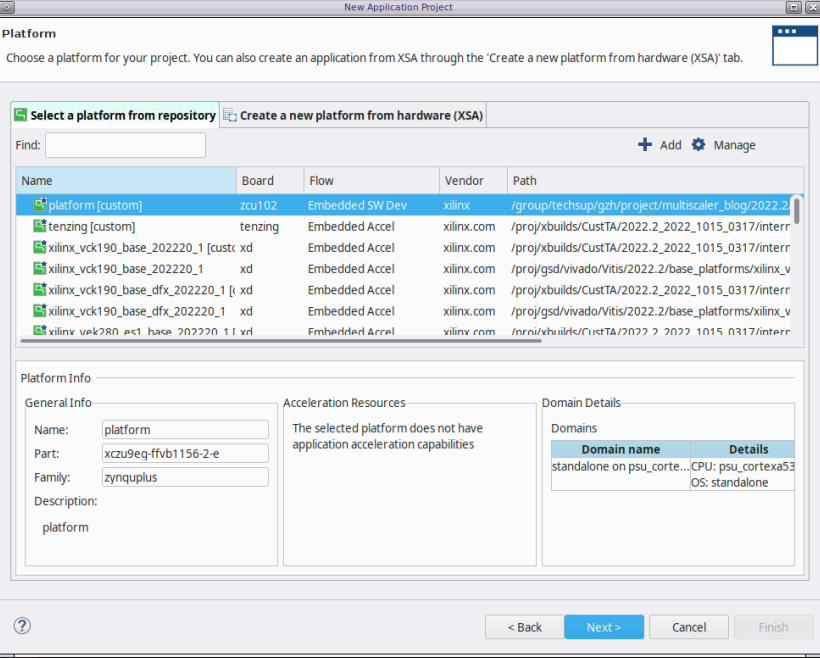

这里的platform选择我们刚才生成的platform工程

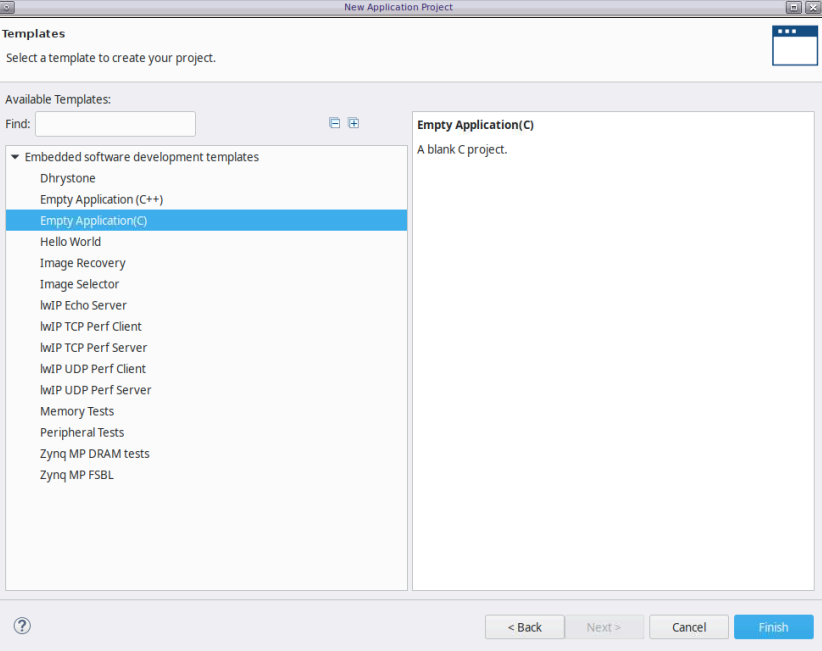

Next后输入工程名称, 一直Next,直到最后选择模板的页面,选择空的C模板。

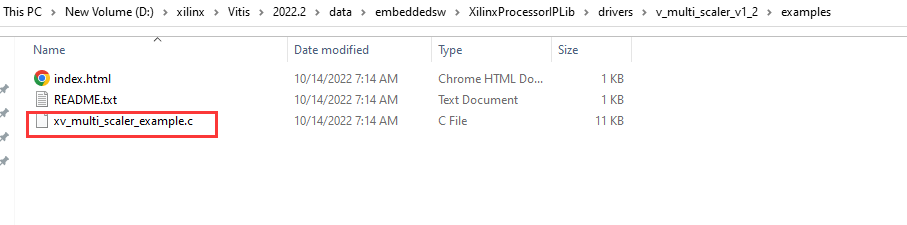

之后需要插入XILINX提供的测试代码,测试代码的路径在

Install_directory即为XILINX工具的安装路径,release是版本号。比如我在windows下的路径就是:D:\xilinx\Vitis\2022.2\data\embeddedsw\XilinxProcessorIPLib\drivers\v_multi_scaler_v1_2

将这个.c文件复制到vitis工程路径下,vitis会在工程中自动识别到

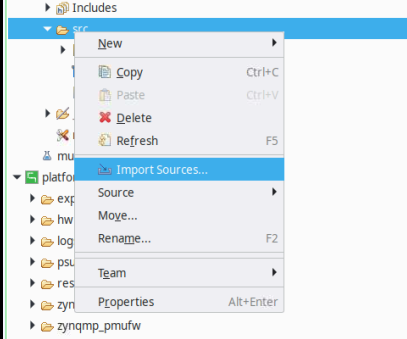

或者右击src插入,选择此文件。

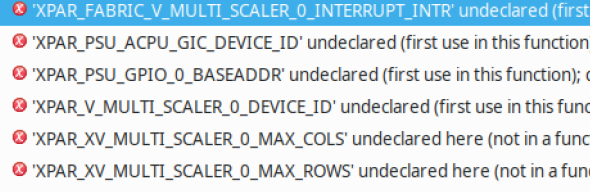

之后对工程进行build project

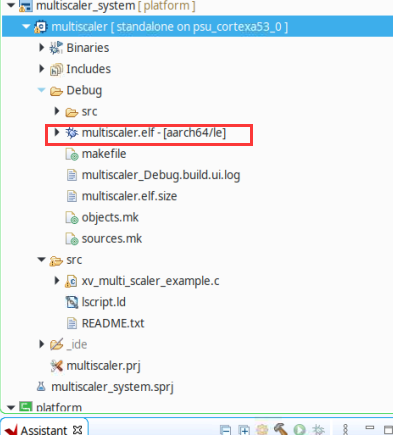

Build结束后,可以看到Debug下生成了elf可执行文件

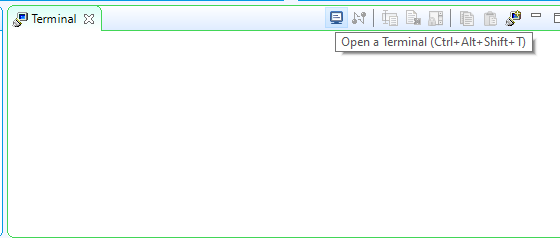

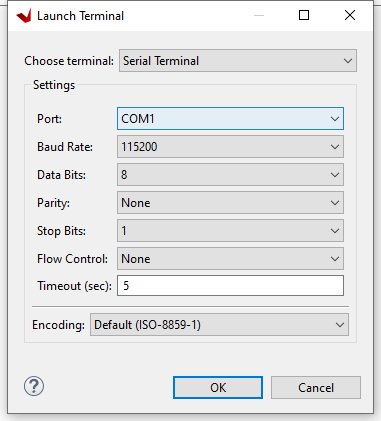

此时即可连接板子,把启动方式更改为JTAG启动,连接JTAG线和串口线,打开Vitis的串口终端,这里演示2022.2的打开方式,不同版本打开方式可能不同。

Windows -> show view -> terminal

打开一个terminal,选择serial,选择对应的COM口,波特率设置为115200

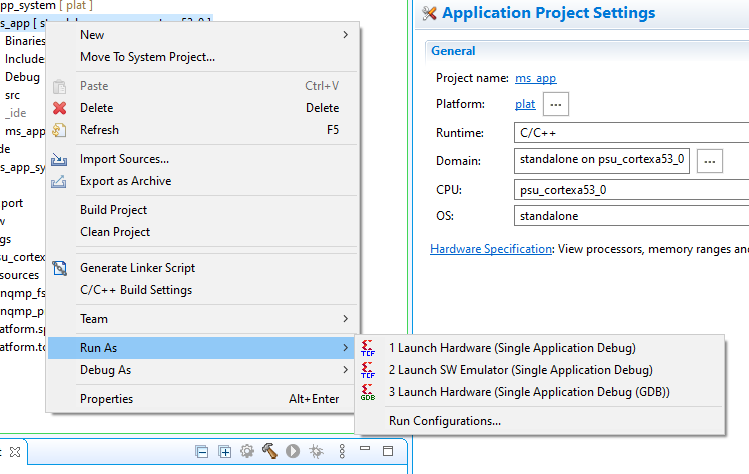

之后右击工程运行即可

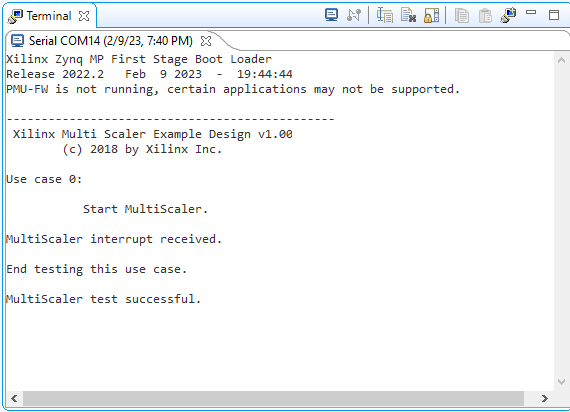

可以看到串口输出结果,提示Multi-scaler测试运行成功

在测试过程中需要注意:

1.工具版本尽量使用最新工具,否则会有IP无法使用等报错,这里我使用2022.2版本。

2.建立好platform后一定要先build,否则可能在建立应用程序时出现缺少文件的情况。

3. 由于测试过程中有诸多不确定因素,本文使用的硬件平台为ZCU102,软件平台为vivado2022.2和vitis2022.2,其他版本的软硬件平台在操作过程中可能会与文章所述有所出入。

4. 此文章只介绍了Multi-Scaler的基本作用,以及示例工程的测试,具体的实现代码可以查看xv_multi_scaler_example.c文件,有关Multi-scaler的详细信息请查阅参考文档的PG325。

点击“阅读原文”查看参考文档:Multi-Scaler LogiCORE IP Product Guide (PG325)