扫描关注一起学嵌入式,一起学习,一起成长

1.1. Makefile基础语法

如果还不熟悉Makefile语法,建议先系统的学习一下,特别是以下几点:

(1) Makefile哪些部分包含的是shell语句:编译规则中的指令部分

${shell XX},var != XX中的XX部分

$(if …, XX, XX)中的XX部分

(2) 变量展开:

=(延迟赋值)、:=(立即赋值)、!=(值为shell命令)、?=(条件赋值)、+=(追加)

(3) include:将指定的其它Makefile内容,展开到当前Makefile

-f/-C:嵌套执行指定(目录中的)Makefile

执行一个Makefile,并不是从第一行开始执行,而是从指定或默认的编译目标开始执行(位置目标编译规则之前的赋值语句,只在相应变量需要被使用时才会执行),其中,Makefile(包括include内容)中的第一个目标,为默认目标,如果make命令行中没有指定编译目标,则执行默认目标。

(5) 根据文件时间戳、中间文件(.d、.cmd),判断依赖更新,决定是否需要重新编译

$(wildcard pattern)

$(patsubst pattern, replacement, text)

$(strip string)

$(filter pattern, text)

$(filter-out pattern, text)

$(call func, args..)

…

$@:编译目标

$<:依赖列表中的第一个依赖对象

$^:依赖列表中的所有对象

$?:依赖文件列表中所有有更新的文件跟我一起写makefile(陈皓):Make 命令教程 | 手把手带你入门 Makefile (精典,超级详细)

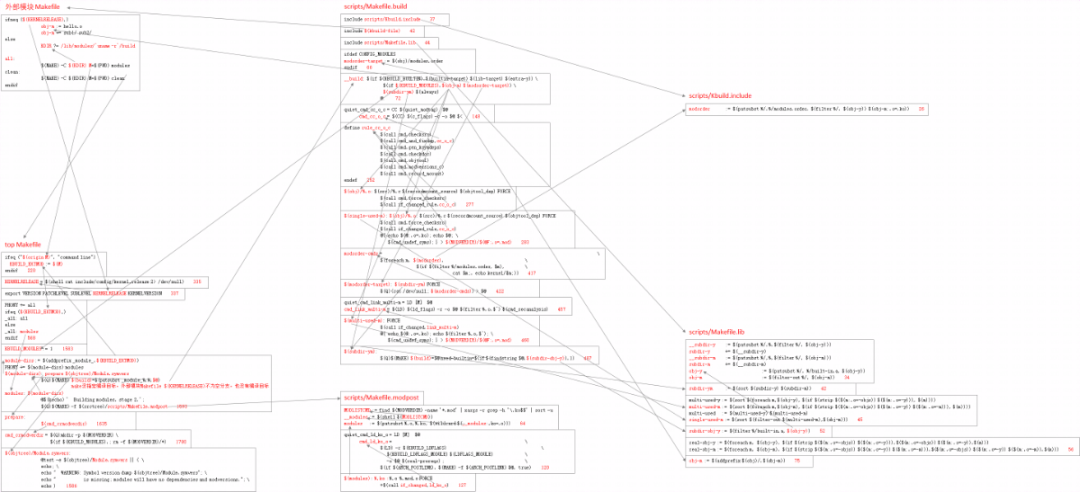

1.2. Kbuild内置函数

Linux内核源码包含一套Makefile程序,本文基于Linux-5.2.5内核源码分析,其中包括top Makefile,scripts/目录下的Makefile、Makefile.build、Makefile.lib、Kbuild.include、Makefile.modpost、kconfig/Makefile等,以及其它目录下的很多子Makefile,统称为Kbuild。Kbuild是按照框架设计思路实现的,使得内核自身包含或外部提供的大量驱动模块,只需要按照Kbuild框架的约定,各自提供一个简单的Makefile即可编译。

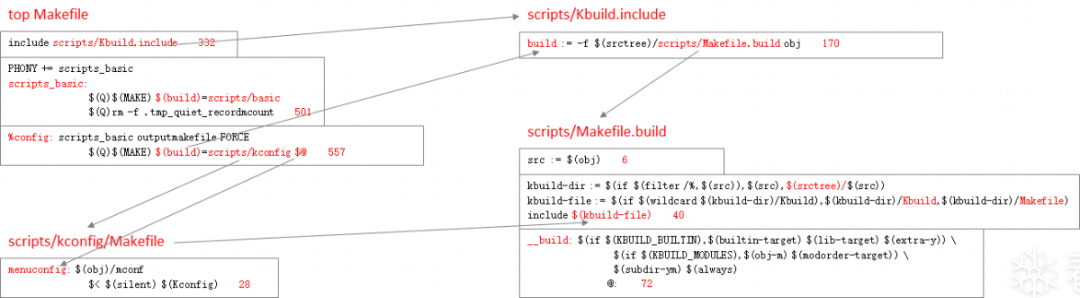

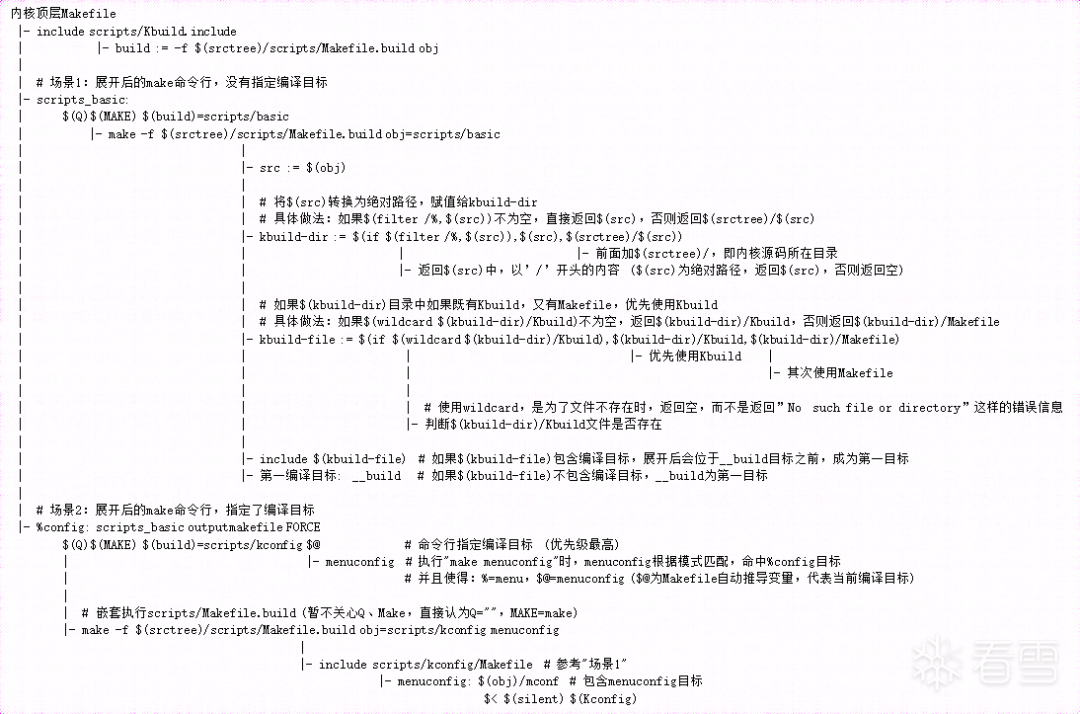

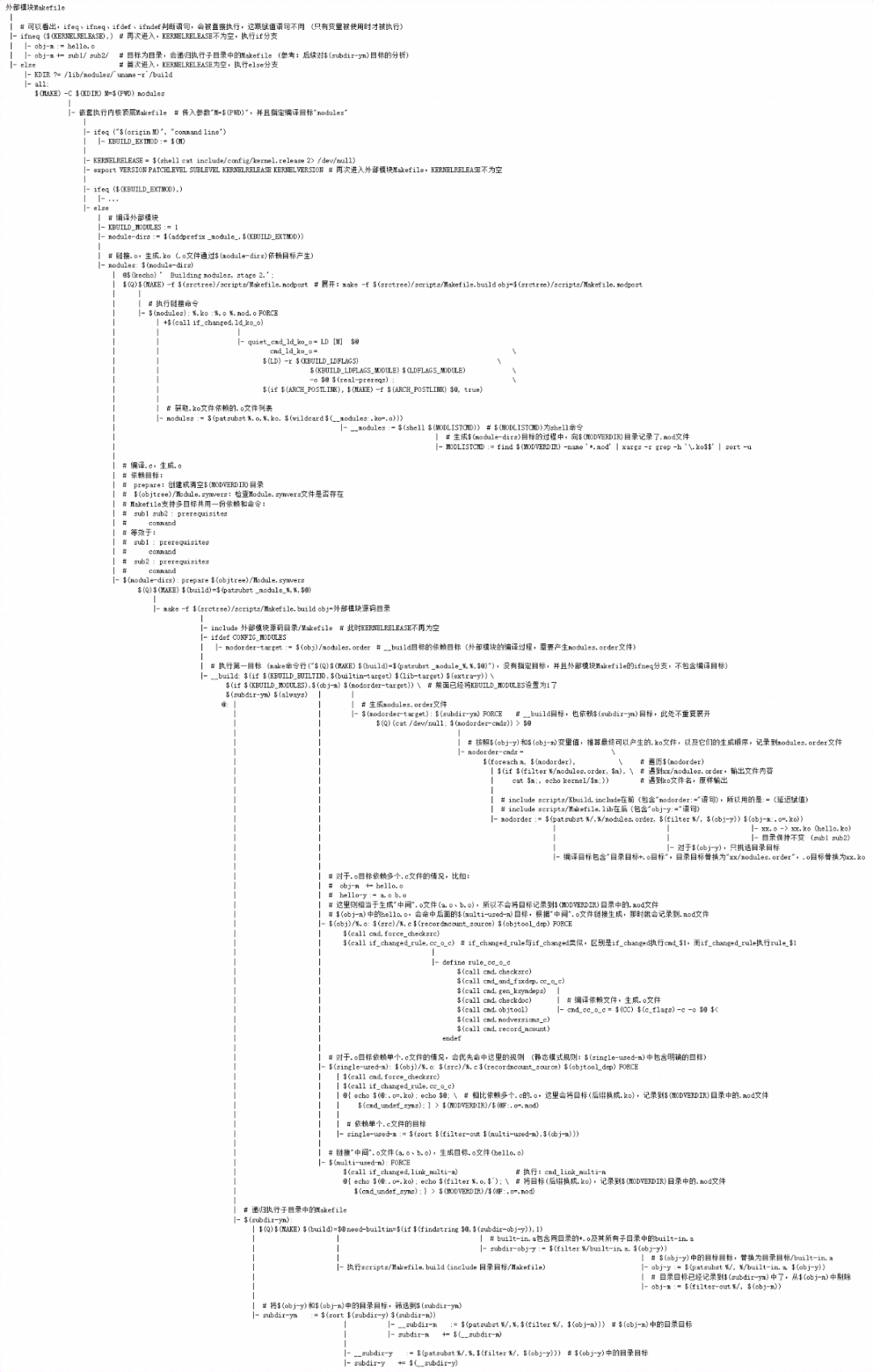

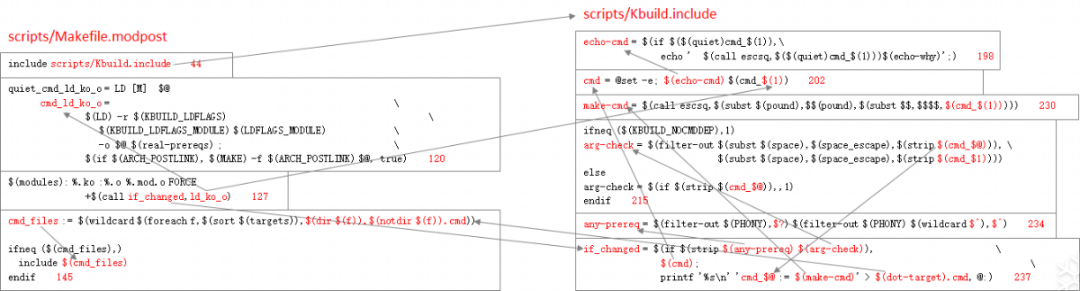

所以,理解内核或驱动文件的编译过程,其实就是要理解Kbuild这套Makefile程序的实现逻辑,既然是程序,就免不了会定义一些函数,由于很多关键的流程,都使用了$(build)和$(if_changed),所以以下先单独介绍(本文分析的Makefile内容,来自Linux-5.2.5内核源码):1.2.1. $(build)

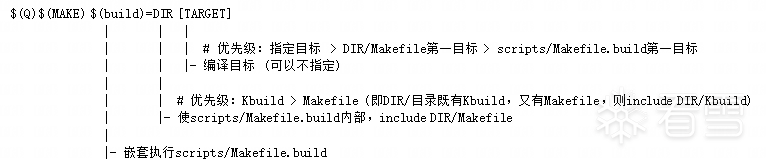

◆使用形式:$(Q)$(MAKE) $(build)=xx目录 [编译目标]以下是$(build)的使用形式,以及每个部分的作用:

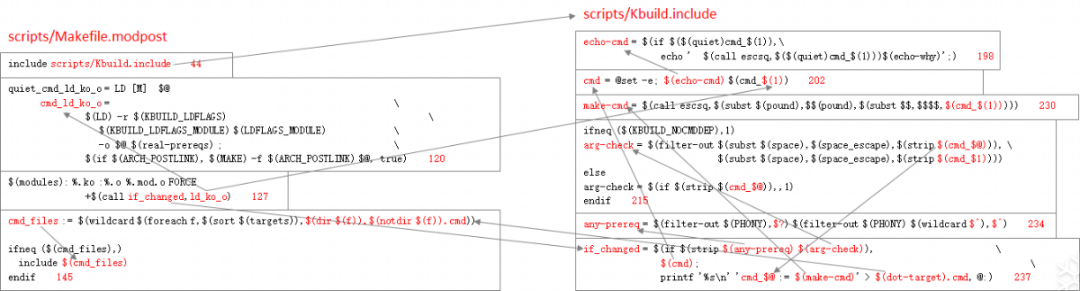

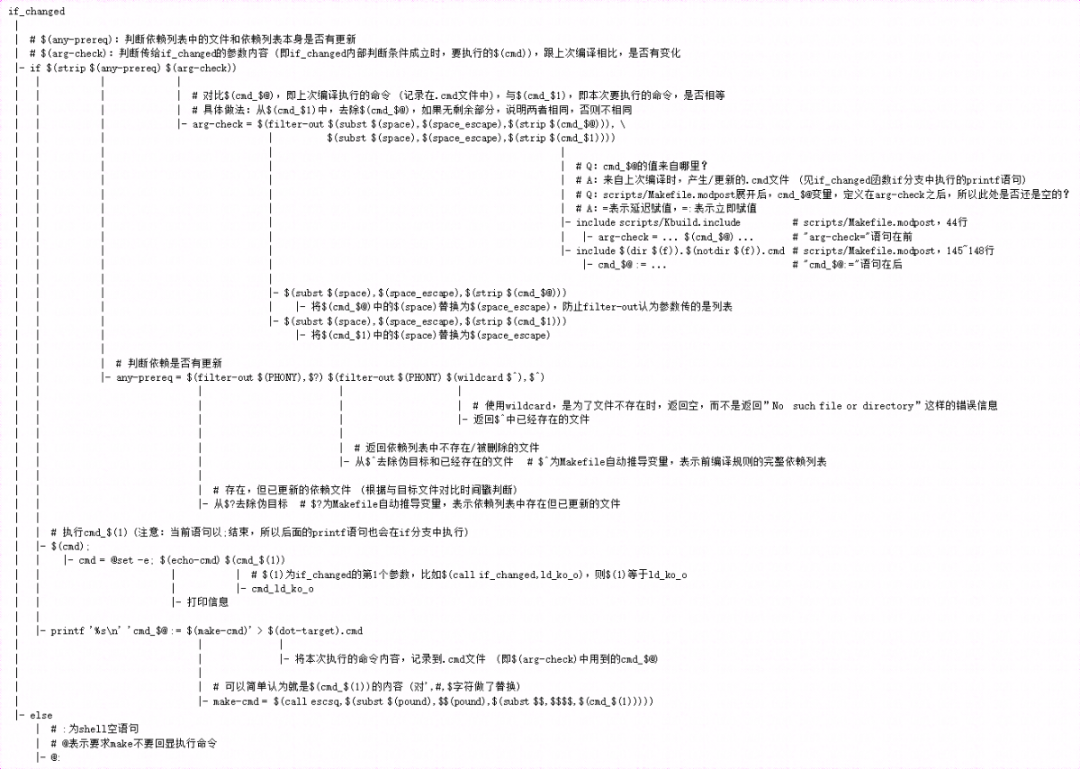

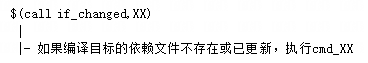

1.2.2. $(if_changed)

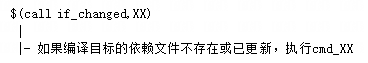

◆使用形式:$(call if_changed, xx)

以下是$(if_changed)的使用形式,及其参数的含义:

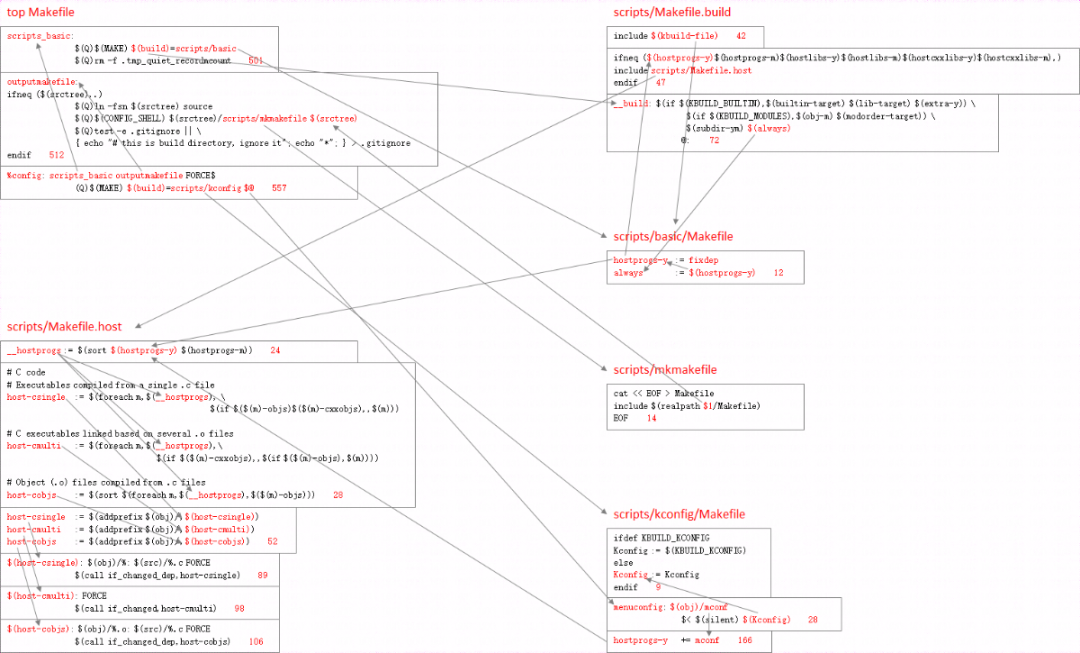

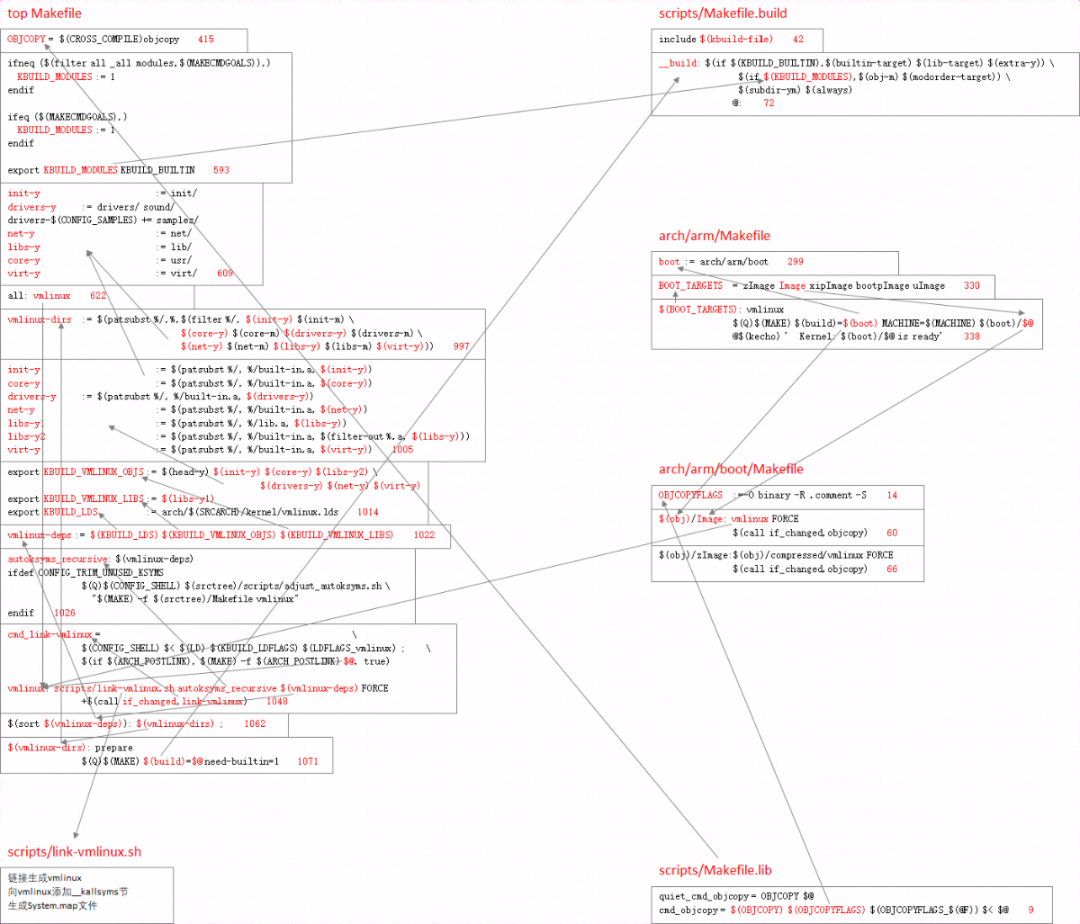

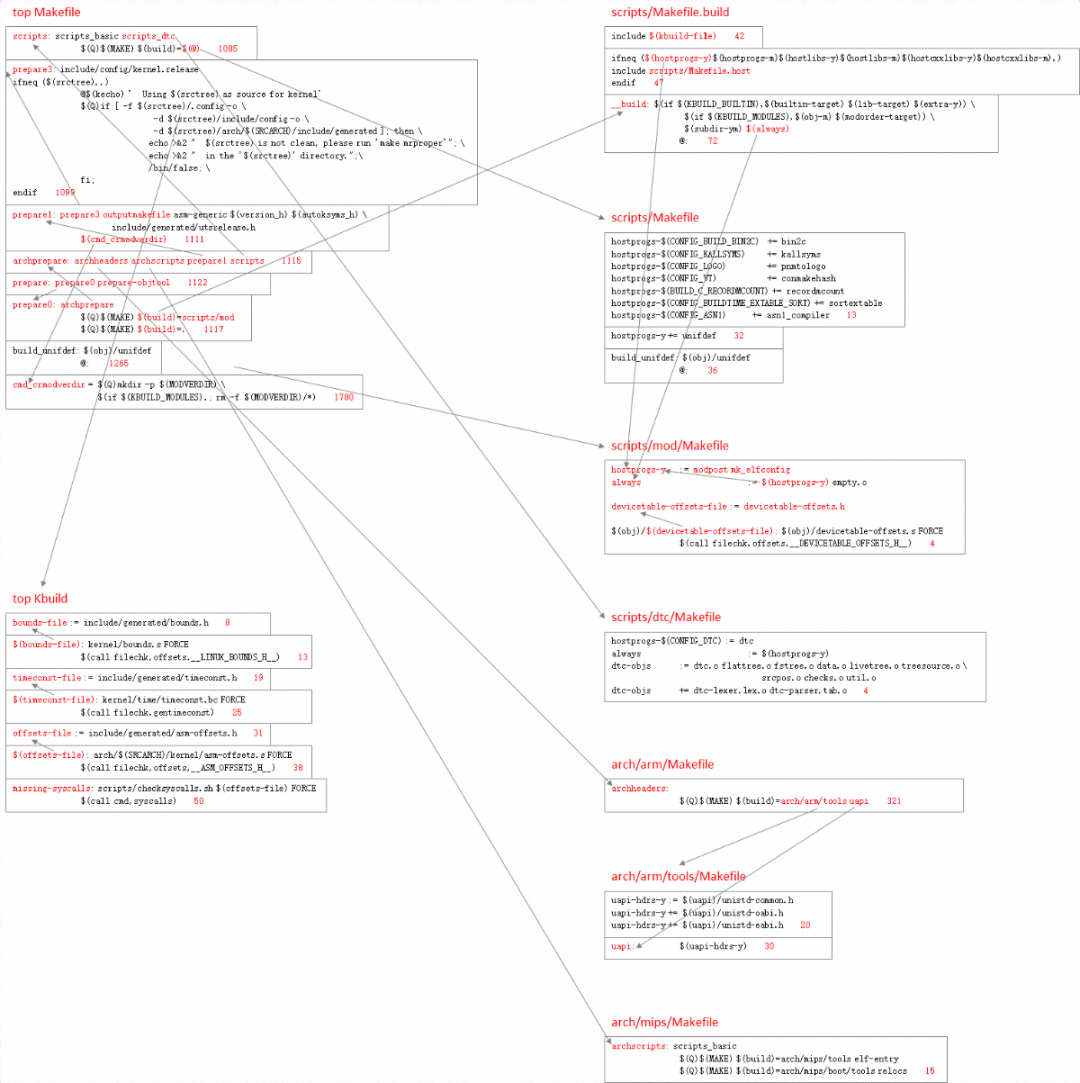

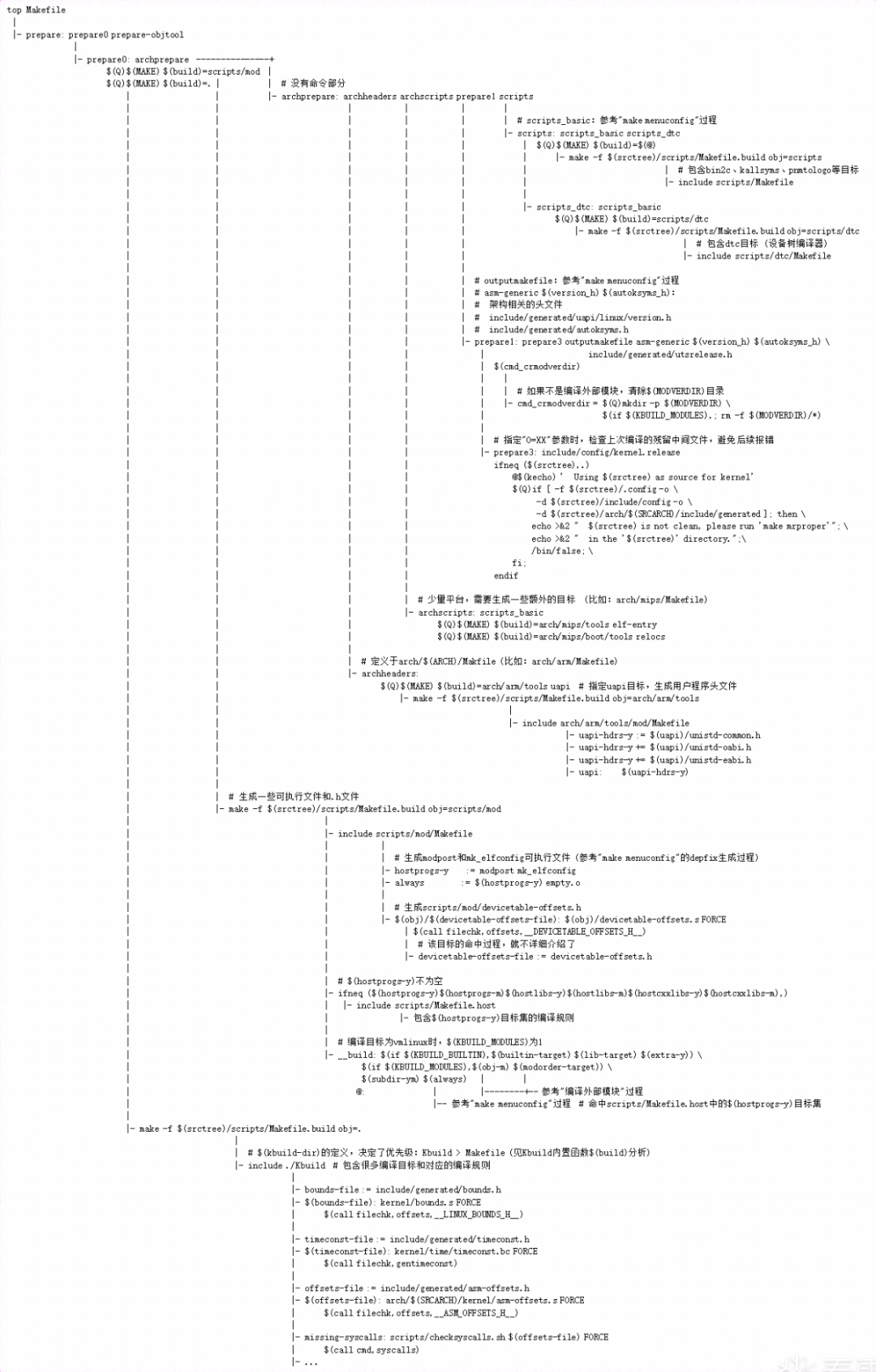

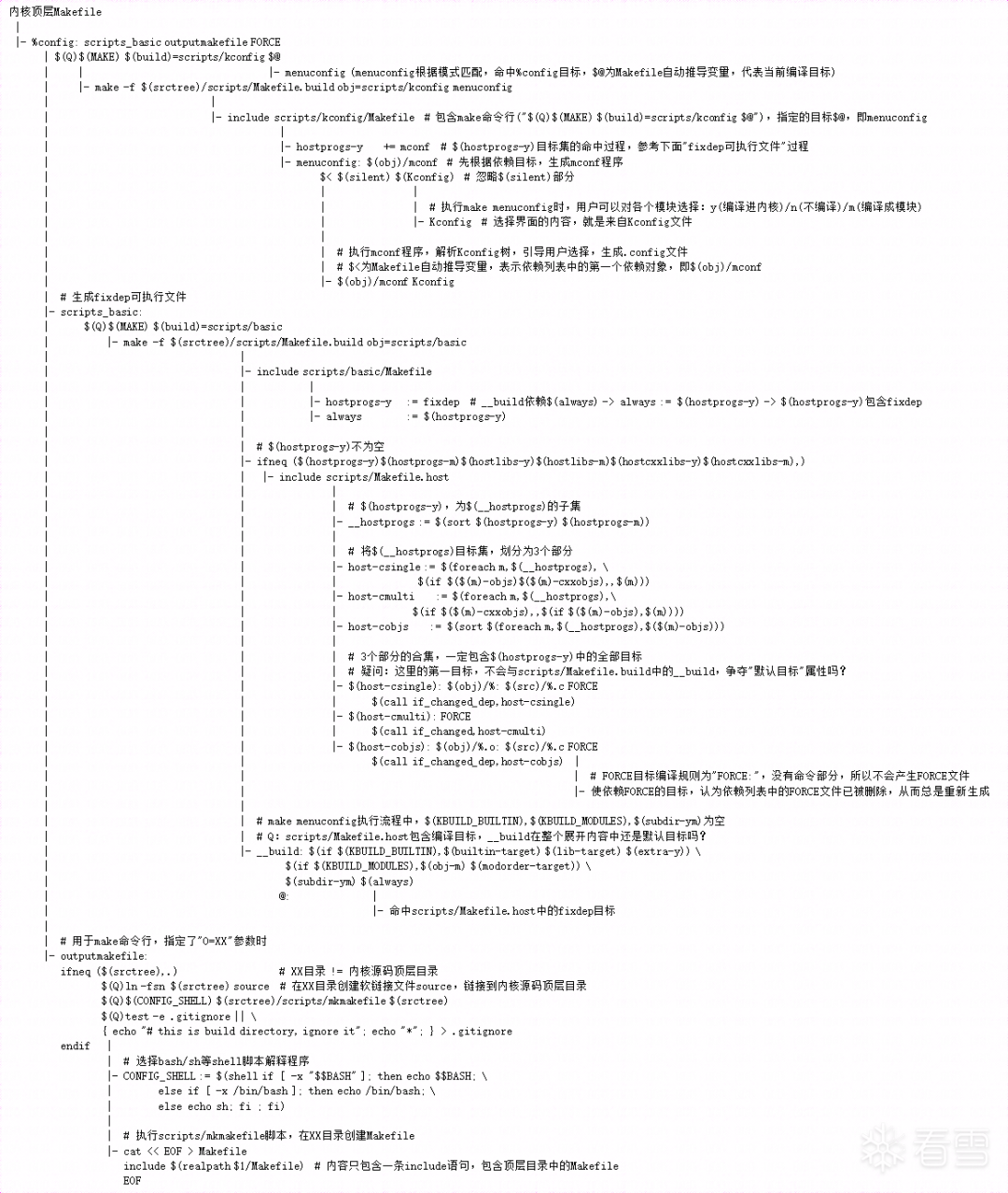

2.1. 涉及Makefile内容

2.2. 概要流程

2.3. 详细流程

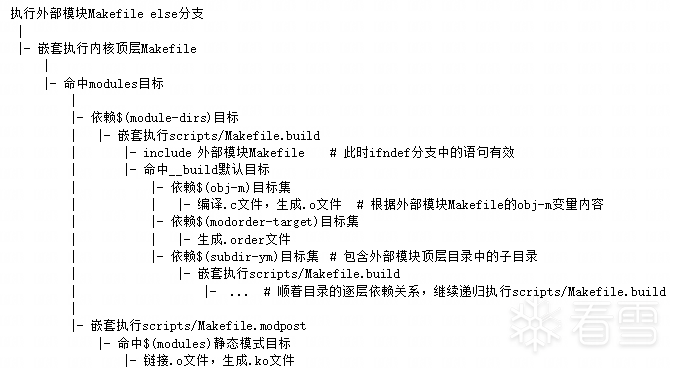

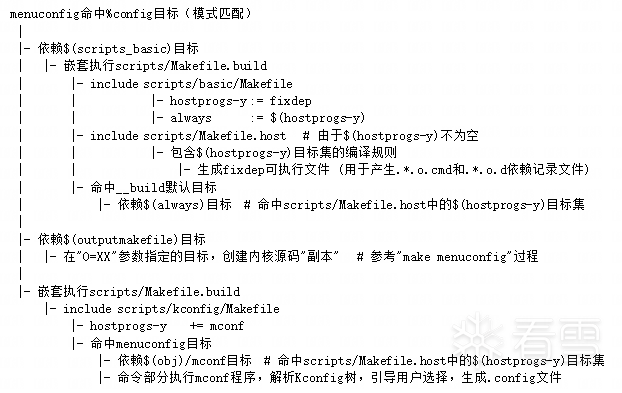

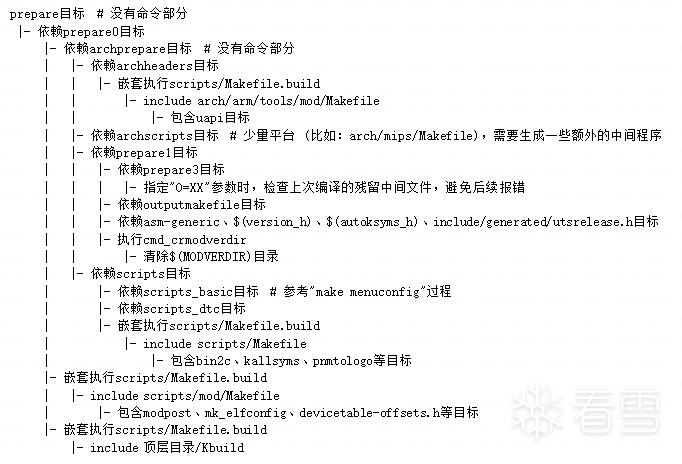

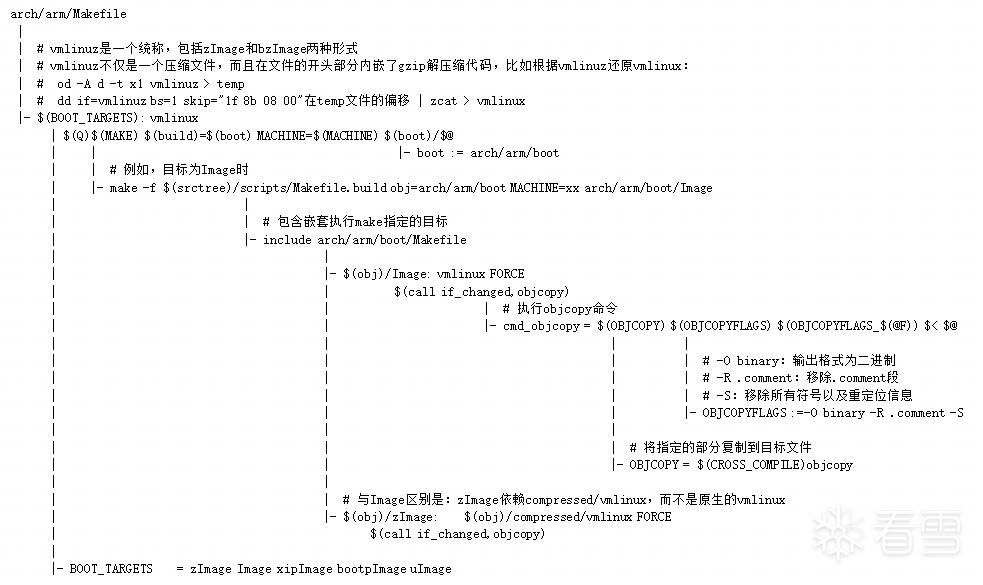

3.1. 涉及Makefile内容

3.2. 概要流程

3.3. 详细流程

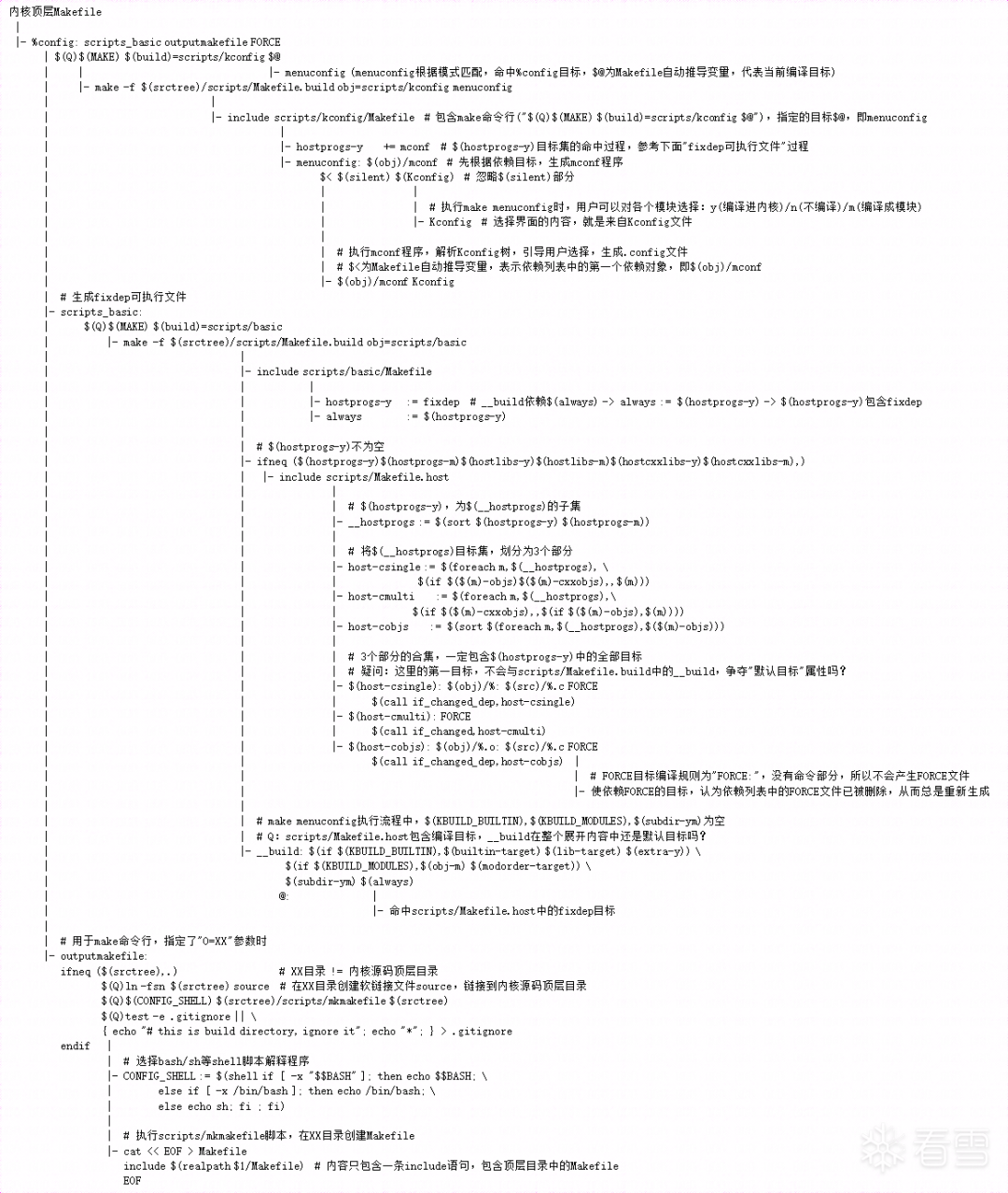

4.1. 涉及Makefile内容

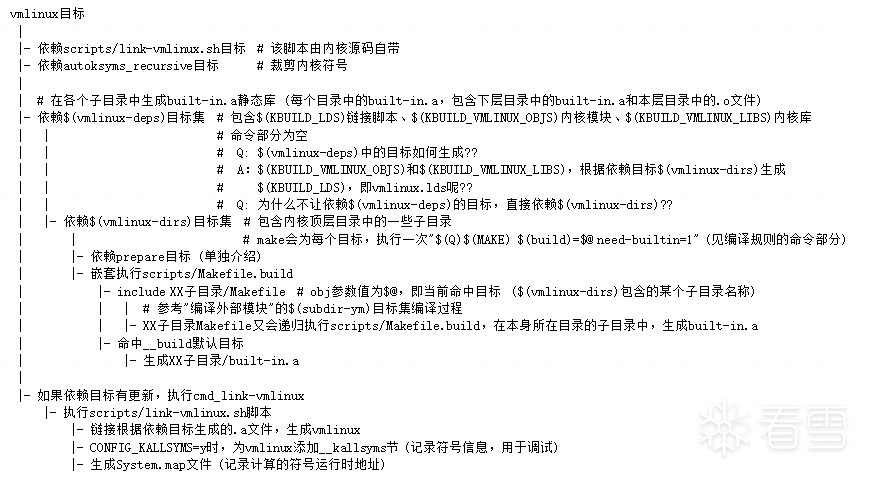

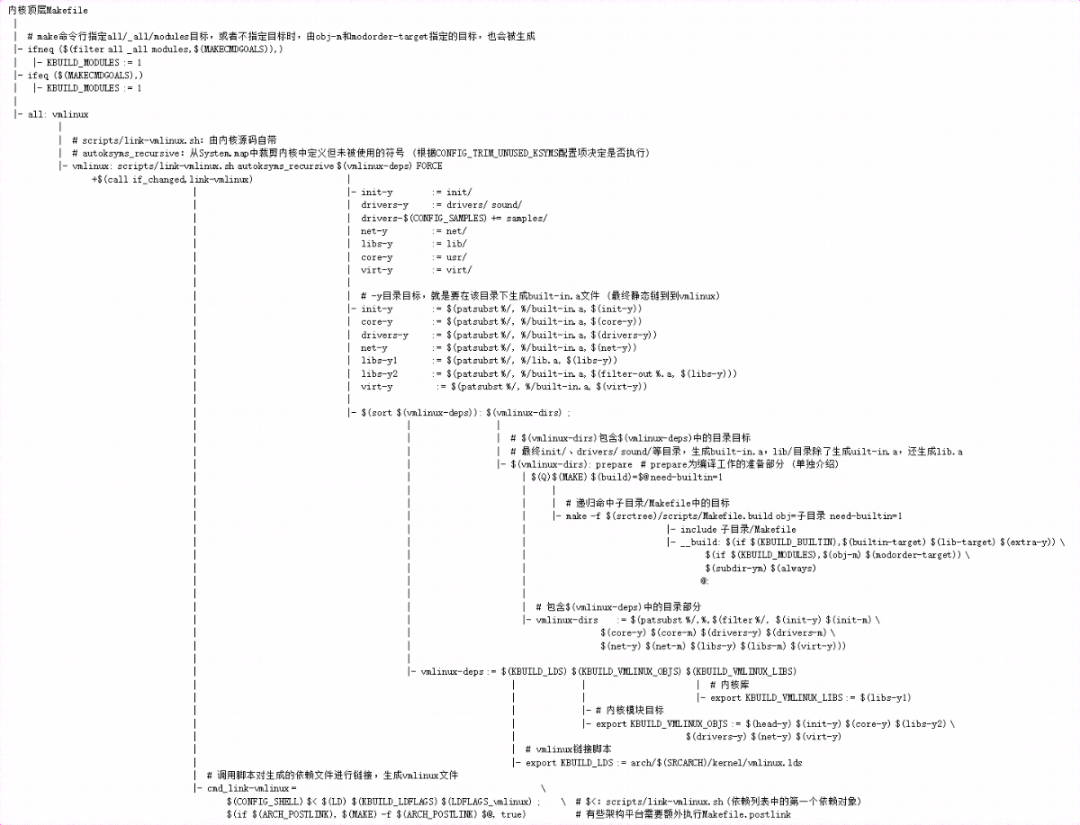

make命令行指定all/_all/modules目标,或者不指定目标时,是为了生成vmlinux文件,而vmlinux目标间接依赖prepare目标,且prepare目标编译规则展开内容比较多,所以以下分开介绍:

4.2. 概要流程

4.3. 详细流程

https://zhuanlan.zhihu.com/p/362640343

跟我一起写makefile:https://blog.csdn.net/whitefish520/article/details/103968609

来源:看雪学苑

文章来源于网络,版权归原作者所有,如有侵权,请联系删除。

推荐阅读:

Linux 内核的 C 语言编程范式 (qq.com)个人微信开放,扫码添加,进高质量嵌入式交流群

觉得文章不错,点击“分享”、“赞”、“在看” 呗!