Efabless 人工智能生成的开放芯片设计挑战赛获胜者将获得免费制造他们的芯片的奖励。这个过程通常成本差不多1万美元。比赛现已开放,需要在6月 2日之前提交参赛作品。

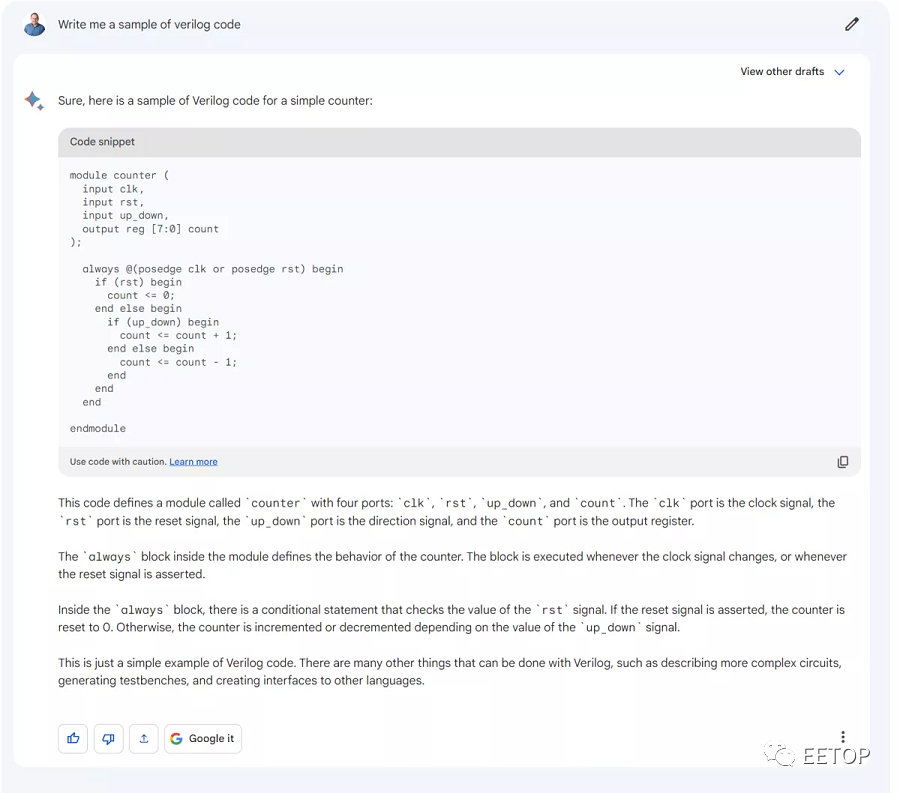

如何使用人工智能来设计芯片?不管你信不信,ChatGPT和Google Bard都能够根据命令编写Verilog代码。Verilog和HDL(硬件描述语言),可以在芯片制造过程中使用,因为它详细说明了有关数字电路和寄存器的关键细节。

比如当我要求Bard给我写一些示例Verilog代码时,我得到了这个:

Efabless拥有一个平台,用于创建和获取设计和制造的开源芯片样本集。在2021年5月推出了chipIgnite计划在,与SkyWater Technology合作开发该计划支持的第一个工艺节点。该公司每年有几次批量制造芯片的计划,客户可以将他们的设计运送到晶圆厂,并在几个月后返回。该公司的chipIgnite程序允许您使用RISC-V内核,自动化设计流程,并选择100,300或1,000个工程样品。

制造完成后,您将获得封装好的芯片,并且某些零件将放在可用于测试的评估板上。然后,您可以使用该公司的开源工具来测试您的设计并将固件下载到其中。该公司对每个chipIgnite项目收费9,750美元。

如果您想开始尝试制作自己的芯片设计,您可以在Efabless注册一个免费帐户,并查看该公司的许多资源和教程。

您还可以在其项目页面上看到人们使用Efabless所做的许多开源设计。(在新选项卡中打开).其中包括VGA精灵生成器,具有模拟神经网络的10位DAC和加密币挖矿SoC。

为了有资格参加人工智能生成的开放芯片挑战赛,参赛者必须至少有人工智能生成的芯片的Verilog,并且必须在提交的文件中包括所有的提示或自动GPT会话记录。不过,你可以在人工智能环境之外进行验证。这些设计必须是开源的,因此任何人都可以复制它们,而且必须使用OpenLane chipIgnite流程来实现。

参赛作品将由一个专家小组进行评审,并在2023年6月9日宣布获奖者。

大赛链接:

https://efabless.com/ai-generated-design-contest