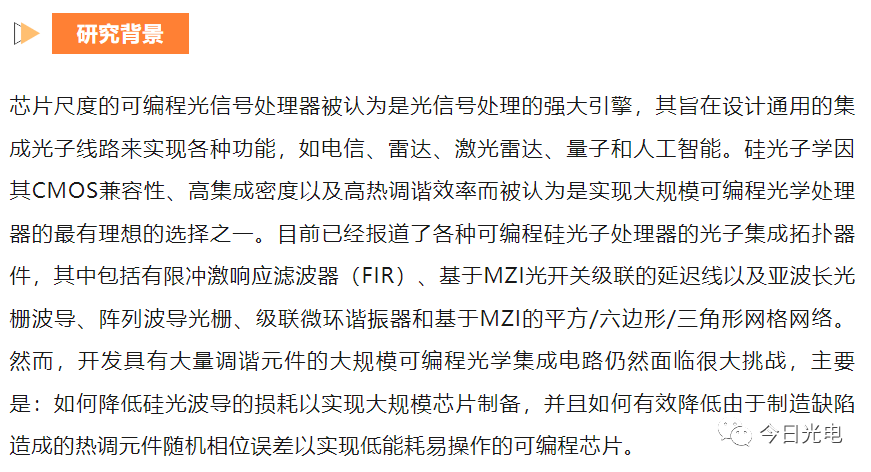

图1 可编程片上信号处理器的结构图

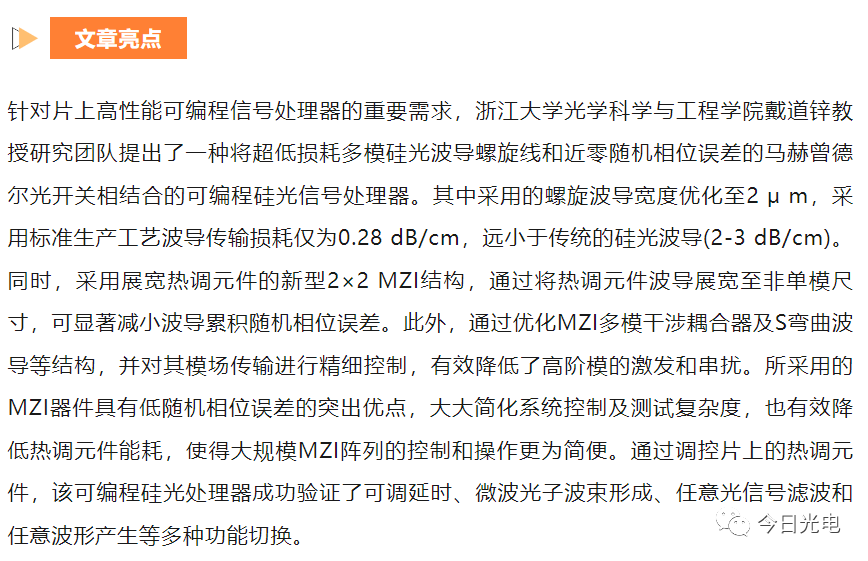

图2 (a)基于光延迟线的4通道光子波束形成器的重构(I2端口输入,4个探测器输出);(b)实验设置。测量延迟线第一通道所有32种延迟状态下微波信号的相位响应(c)和群延迟响应(d)。在18 GHz时,所有四个信道的延迟变化(e)和测量的S21 (f)

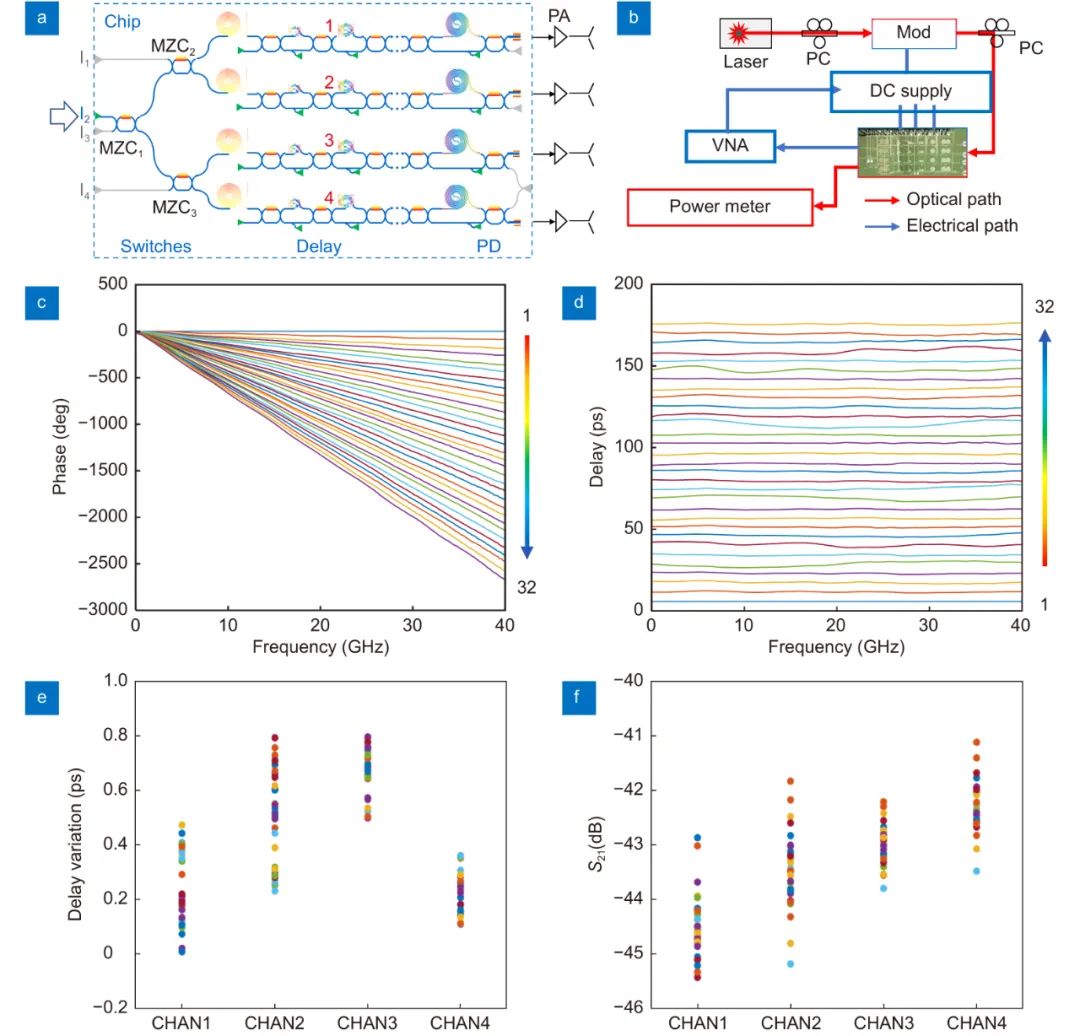

图3 (a)任意频谱产生器的重构(I4端口输入,O3端口输出);滤波器频谱响应测量: (b)-(d)滤波器自由光谱范围可调谐性的演示;(e)滤波器通带整形的演示

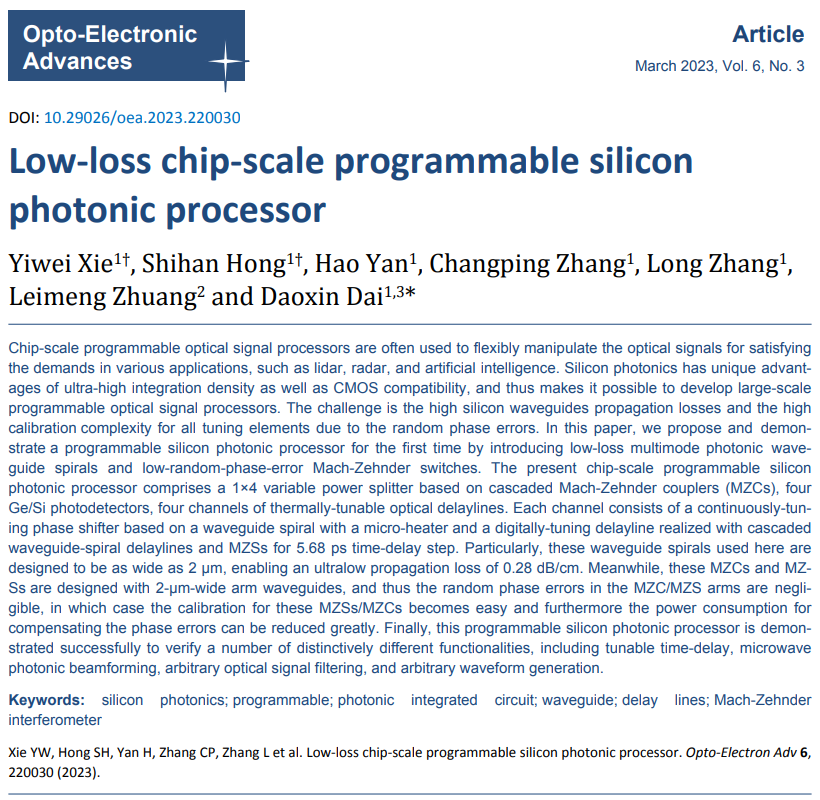

该工作以“Low-loss chip-scale programmable silicon photonic processor”为题发表在Opto-Electronic Advances (光电进展)2023年第3期。

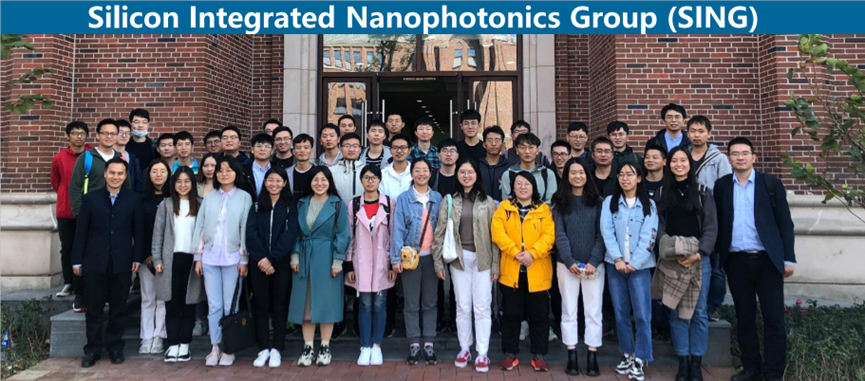

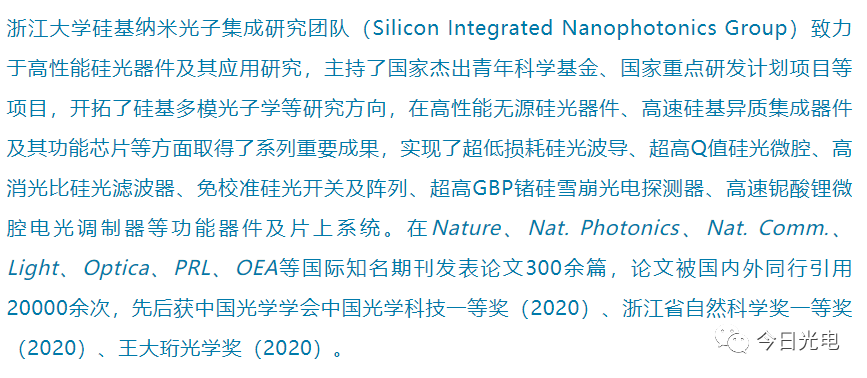

研究团队简介

来源:光电期刊

申明:感谢原创作者的辛勤付出。本号转载的文章均会在文中注明,若遇到版权问题请联系我们处理。

----与智者为伍 为创新赋能----

联系邮箱:uestcwxd@126.com

QQ:493826566