第32届国际物理设计研讨会(ISPD2023)于2023年3月26日至29日在线举行,来自世界各地的顶尖研究人员和下一代设计师每年都会聚集在一起,进行未来芯片的物理设计。半导体制造工艺技术的进步继续将工艺光刻的极限推向深纳米领域,以获得更好的性能、功率和面积,遵循摩尔定律。各种器件都采用了异构集成,以实现更好的系统级电源性能成本权衡和更高的性能。

2023年3月29日,加州理工学院和NVIDIA的Anima Anandkumar教授发表“求解偏微分方程的神经算子与反向设计Neural Operators for Solving PDEs and Inverse Design”的主题演讲。

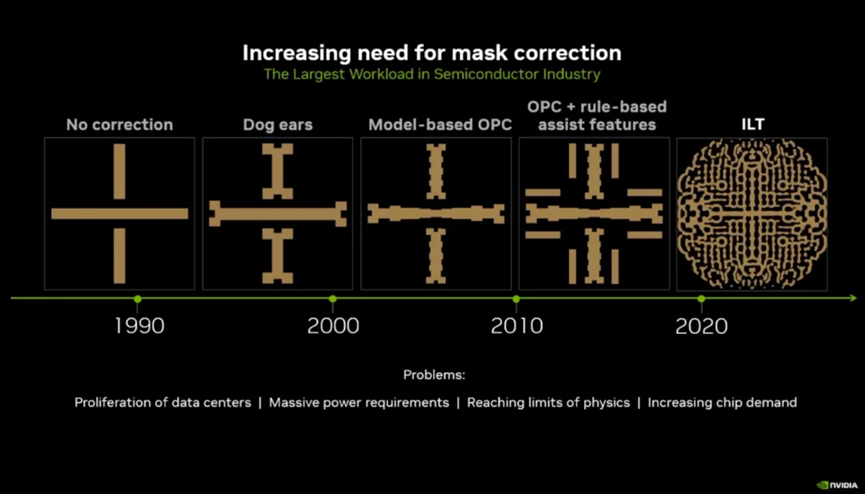

计算光刻通常包括光学邻近效应修正(OPC)、光源-掩膜协同优化技术(SMO)、多重图形技术(MPT)、反演光刻技术(ILT)等四大技术。当芯片的关键尺寸小于光源波长的时候,所需要的掩膜板越来越复杂。因此这几十年来,芯片在制造过程中制作掩膜一直是半导体制造中的关键环节。尤其是芯片逐渐来到3nm及以下,不仅需要更加精准的光刻计算,反而光刻计算所需的时间也越来越长。

深度学习代理模型在模拟光子学、流体流动、分子动力学和材料特性等复杂物理现象方面显示出了前景。然而,标准神经网络假设有限维的输入和输出,因此无法承受训练和测试之间分辨率或离散化的变化。

Anima Anandkumar教授介绍了可以学习算子的傅立叶神经算子,傅立叶神经算子是无限维空间之间的映射,是离散不变的,并且可以推广到训练数据的离散化或分辨率之外。团队研究了各种用于正向建模和反向设计问题的偏微分方程,并展示了光刻领域的实际增益。Anima表示,与传统的数值方法或优化技术相比,人工智能可以通过使用GPU加速计算来显著加速,机器学习可以找到更快的方法来解决偏微分方程和光刻等其他物理问题,渐进式自我训练可以不断提高掩模的质量。

就在ISPD2023会议开幕前的3月21日,一年一度的英伟达春季GTC大会正式开幕,英伟达在GPU之上构建了cuLitho计算光刻技术软件库,可以将计算光刻加速40倍以上,使得2nm及更先进芯片的制造成为可能。

计算光刻是芯片设计和制造领域中最大的计算工作负载,每年消耗数百亿CPU小时。大型数据中心24x7全天候运行,以便创建用于光刻系统的掩膜板。这些数据中心是芯片制造商每年投资近2000亿美元的资本支出的一部分。cuLitho能够将计算光刻的速度提高到原来的40倍。举例来说,英伟达H100 GPU的制造需要89块掩膜板,在CPU上运行时,处理单个掩膜板需要两周时间,而在GPU上运行cuLitho只需8小时。

目前,全球最大晶圆代工龙头台积电、全球光刻机龙头ASML、全球EDA龙头新思科技(Synoposys)均参与合作并引入这项技术。

据悉,台积电将于6月开始对cuLitho进行生产资格认证。台积电可通过在500个DGX H100系统上使用cuLitho加速,将功率从35MW降至5MW,替代此前用于计算光刻的40000台CPU服务器。使用cuLitho的晶圆厂,每天可以生产3-5倍多的光掩膜,仅使用当前配置电力的1/9。台积电首席执行官魏哲家则夸赞它为台积电在芯片制造中广泛地部署光刻解决方案开辟了新的可能性,为半导体规模化做出重要贡献。

黄仁勋说,cuLitho已集成到新思科技Proteus全芯片掩膜合成解决方案和Proteus ILT逆光刻技术中。新思科技董事长兼首席执行官Aart de Geus称,在英伟达的cuLitho平台上运行新思科技的光学邻近校正(OPC)软件,将性能从几周加速到几天。

ASML首席执行官Peter Wennink称阿斯麦计划将对GPU的支持集成到其所有的计算光刻软件产品中。