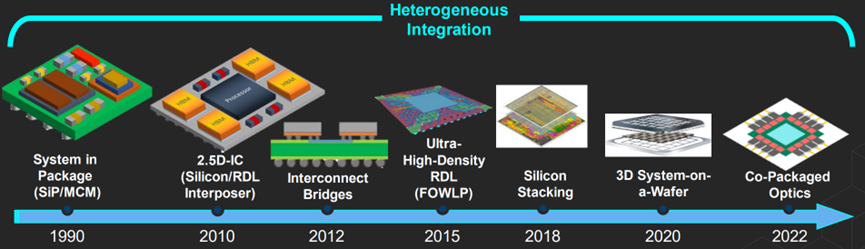

第32届国际物理设计研讨会(ISPD2023)于2023年3月26日至29日在线举行,来自世界各地的顶尖研究人员和下一代设计师每年都会聚集在一起,进行未来芯片的物理设计。半导体制造工艺技术的进步继续将工艺光刻的极限推向深纳米领域,以获得更好的性能、功率和面积,遵循摩尔定律。各种器件都采用了异构集成,以实现更好的系统级电源性能成本权衡和更高的性能。

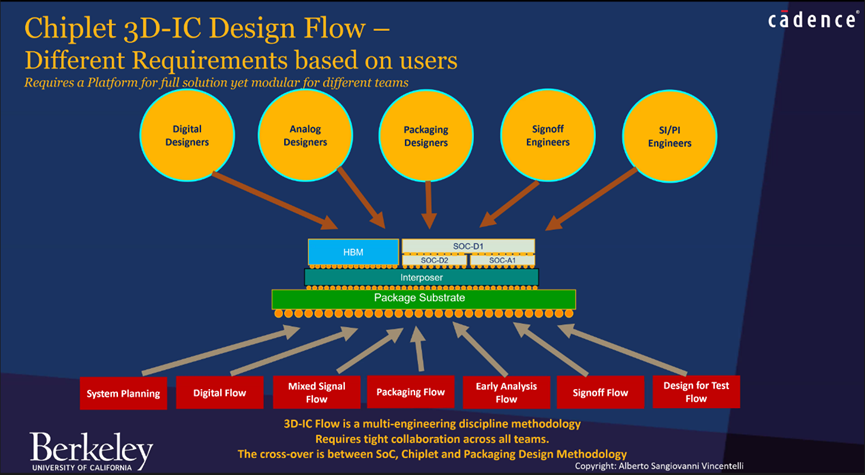

2023年3月27日,加州大学伯克利分校教授Alberto Sangiovanni Vincentelli在主题演讲“芯粒的自动化设计Automated Design of Chiplets”中表示,芯粒的目标不是设计一个大芯片,而是通过最新的封装方式,满足来自智能系统设计的需求。芯粒已被公认为单片SoC的一种有前途的替代品。

尽管在各个相关领域取得了进展,但目前芯粒的设计在很大程度上仍然依赖于手动过程。Alberto Sangiovanni Vincentelli强调,芯粒自动化设计的前景很好。

同日上午,举办了两场关于3D IC、异构集成和封装的会议,来自慕尼黑工业大学、佐治亚理工学院、台湾阳明交通大学、桑迪亚国家实验室、楷登电子和新思科技的专家,分别介绍了该领域的最新进展。

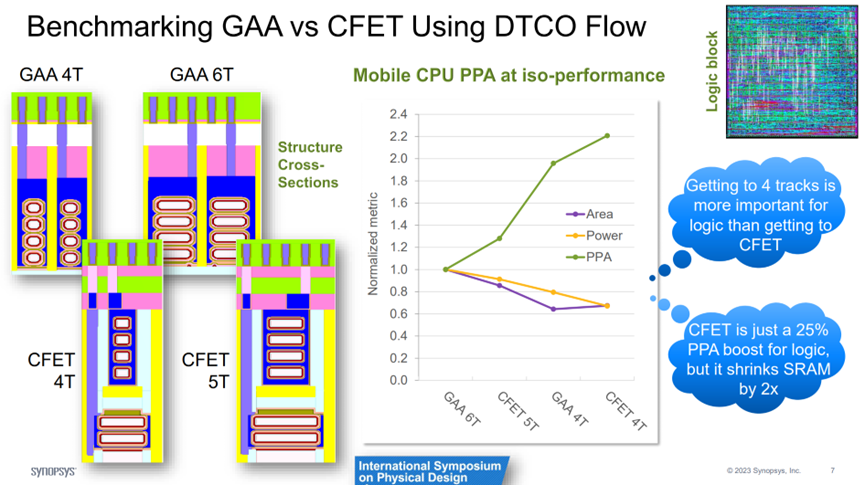

目前产业正在从FinFET向全环栅(GAA)技术过渡,未来几年可能会有几代GAA技术。那么接下来是什么?新思科技的Victor Moroz表示,我们试图通过将GAA技术与2D材料上的晶体管和堆叠晶体管(CFET)进行比较来回答的问题。逻辑的主要目标是在功率、性能、面积和成本(PPAC)方面获得有意义的增益。SRAM的主要目标是在不损失性能和产量的情况下,实现SRAM阵列及其外围的显著密度缩放。另一个目标是朝着有希望长期进步的方向前进,比如在向更大数量的晶体管层移动之前开始堆叠两层晶体管。