什么是FPGA原型验证?

EDA工具的使用主要分为设计、验证和制造三大类。验证工作贯穿整个芯片设计流程,可以说芯片的验证阶段占据了整个芯片开发的大部分时间。从芯片需求定义、功能设计开发到物理实现制造,每个环节都需要进行大量的验证。

大规模集成电路设计复杂性的提升,使芯片验证面临资金与时间的巨大挑战。早期开发者想验证芯片的设计是否符合预设,只有等待漫长的模拟结果,或是等待流片成果。时间成本和经济成本都较高。

现如今验证方法也越来越多,例如:逻辑仿真(功能验证),形式验证,原型验证。功能验证基于软件,验证成本较低,验证环境方便,但性能较差;形式验证为静态验证方式,但不可仿真DUT的一些动态行为。

而开发者即可通过用FPGA板拼凑出有效的流程来对设计进行验证,FPGA原型验证这一解决方案就此应运而生。

FPGA原型设计是一种成熟的技术,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能和性能。

FPGA原型验证,是SoC基于FPGA的一种验证方式,一般是在前端RTL设计和RTL仿真之后。FPGA和ASIC前端代码都是基于 Verilog HDL 开发的,所以ASIC代码理论上是可以在FPGA平台上跑起来的,在流片之前,尽可能的去确定芯片功能的正确性的一种验证方式。

FPGA的应用范围广泛,且基于FPGA可以反复擦写,使用的语言和ASIC设计都是一样的,因而被当作一种性价比优越的芯片验证基础设施。FPGA原型验证已是当前原型验证的主流且成熟的芯片验证方法。

FPGA原型在数字芯片设计中非常重要,因为相比用仿真器,或者加速器等来跑仿真,FPGA的运行速度,更接近真实芯片,可以配合软件开发者来进行底层软件的开发。这一流片前的软硬件的协同开发,是其最不可替代的地方。

为什么要做原型验证

1、在流片之前,尽可能还原芯片真实使用场景,达到充分验证芯片功能的目的,确保功能模块的可靠性和稳定性,评估其性能;

2、可以缩短芯片类产品上市的时间,也可以给有需求的客户演示,开始预售;

3、原型验证可以降低成本,在芯片原型验证这个阶段,改代码相对容易很多,可以节省大量成本;也可以给软件设计人员提供验证平台。

原型验证的原则

1、在芯片设计中,FPGA所有工作都是为芯片服务的;

2、在芯片设计中,芯片的逻辑规模远大于FPGA设计逻辑。一般FPGA原型验证都选用资源逻辑相对多的FPGA芯片,同时一要对芯片逻辑进行正确的分割;

3、在芯片设计中,芯片的主频远高于FPGA平台上的时钟。在原型验证过程中,一定要做的就是降低主频。

用FPGA对ASIC进行原型验证

ASIC→FPGA原型步骤:

1.FPGA选型

需考虑:容量(纯逻辑容量,存储容量,DSP单元容量等)、内置IP(时钟,存储控制,CPU等硬核)、接口(普通接口与专用高速接口)、速度(资源占用率在50%左右时的速度,一般被用来评估原型)

2.做板或者购买原型板

需考虑:信号完整性,电源问题,时钟问题,可扩展性等

3.将ASIC设计转换装入FPGA

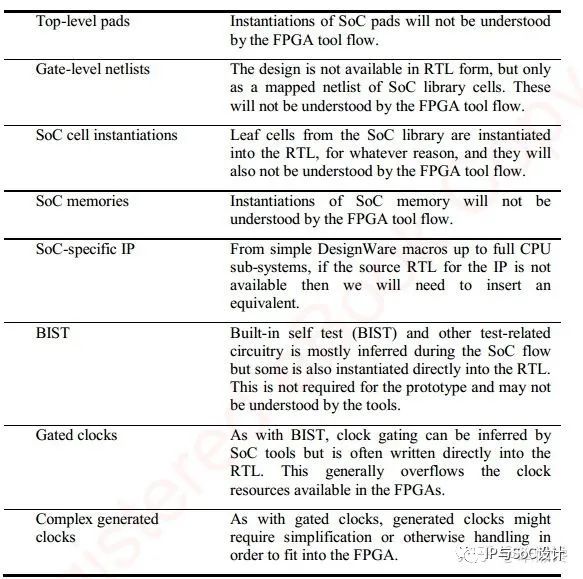

以下内容需要修改:

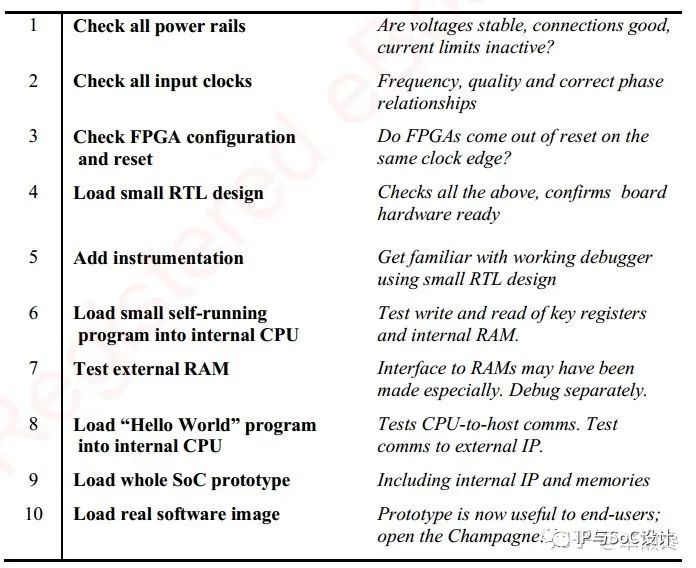

4.调试启动FPGA原型

5.载入软件协同运行

6.软硬件系统验证

FPGA原型验证的优缺点

FPGA原型设计的优点是什么

性能

FPGA通常建立在最新的制造流程上,以实现最高的密度和运行速度。即使是采用主流工艺构建的FPGA,也可以提供高门限等效计数(FPGA通常以可容纳多少个标准查找表来衡量)。

超过最大FPGA功能的设计有时在多个FPGA上进行原型设计。这使得将源RTL映射到FPGA原型环境变得更加困难,并且可能会降低原型的性能。

成本

FPGA是批量生产的芯片,具有竞争力的价格。许多公司将它们集成到现成(OTS)原型板上,尽管一些公司更喜欢建立自己的原型印刷电路板(PCB) 。

基础设施

两家主要FPGA供应商(原型设计市场领导者Xilinx及其竞争对手Altera)都提供了广泛的工具来支持他们的产品。他们还与主要的EDA供应商建立了联盟,这些供应商为软件套件提供了增强的FPGA原型设计。

其他OTS主板供应商也与这些和其他工具供应商以及他们自己的软件有合作关系。

可移植性

FPGA板可以在与最终SoC相同的嘈杂环境中进行测试。这对于打算用于便携式消费设备以及工业,通信基础设施,医疗和军事/航空航天市场的产品有益。

可用性

FPGA原型的成本相对较低意味着公司通常可以构建其中的几个,这加速了硬件验证,软件开发,硬件/软件协同验证和软件验证。每个团队都可以有自己的原型。

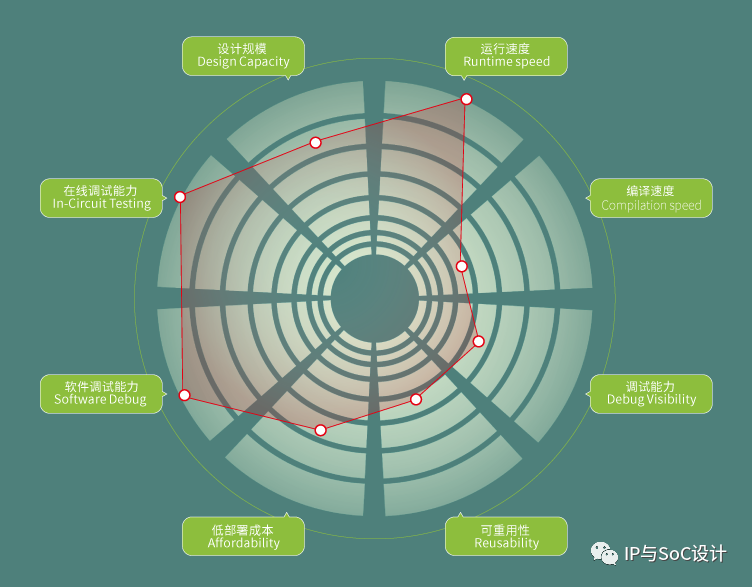

FPGA原型验证的缺陷

-编译时间比较长

-debug方式不是特别成熟

FPGA原型验证面临的技术挑战

分区

大型设计可能需要在多个FPGA之间进行分离(分区)以实现所需的门控容量。这项任务通常被认为是FPGA原型设计的最大挑战。

分区过程本身很可能是一个棘手的迭代过程,涉及将设计映射到设备的众多判断调用,以及从RTL或软件中的实际错误中过滤出并纠正映射错误。

手动干预

FPGA原型设计可能需要几种类型的手动干预。

由于原始设计RTL被转换为FPGA综合和布局工具所需的硬件描述语言(HDL),因此即使工具已经实现了大部分翻译的自动化,也可能需要一些手动编码才能使原型工作。

映射的各个方面都面临着挑战。FPGA上的时钟树路由(特别是原始设计具有门控时钟的地方)非常困难。如果允许关键路径通过缓慢的芯片到芯片到芯片路径运行,原型性能将会受到影响。原创中的内存和加密块也会带来重大困难。

调试可见性

可用的可见性往往局限于单个FPGA,这使得跨多个FPGA映射的设计使调试可见性变得更加困难。

编译时间

编译FPGA原型如果产生错误,修复错误后,需要从头开始重新编译。这会造成很严重的延误。

容量限制和性能要求

对于大型的设计(大于2千万等效ASIC门),一块FPGA往往容纳不下,此时必须将多块FPGA互联才能验证整个设计,在这种情况下,就需要对大型的设计进行Partition即分割。Partition引入了新的问题,而这些问题其实在芯片中并不存在,很多时候耗费很多人力去实现一个可用的Partition方案,仅仅是受限于FPGA的容量而不得已的处理办法。Partition引入的最大问题是对I/O的需求激增。另一个方面,由于在SoC原型验证中模块常常会增减,导致需要频繁的改动Partition方案,如果手动去处理,则需要花费很多精力才能得到一个上文提到可用但折中的方案。此外,处理大量的Cross-FPGA信号非常容易出错,所以对于大型的SoC FPGA原型验证,必须采用自动化的工具去完成Partition,这对EDA工具而言亦是全新的挑战。

迭代速度

由于SoC芯片的设计频率很高,为了让原型验证平台尽可能和SoC芯片性能接近,开发者期望让FPGA原型平台运行在尽可能高的频率上,但是由于SoC的RTL代码是为芯片实现设计,大量深层次组合逻辑的存在,导致了SoC RTL代码在FPGA上实现时时序收敛困难。

可观测性

FPGA也是芯片产品,所以内部的信号无法直接观测。通常需要借助于FPGA的Debug工具在生成Bit文件前选取要观察的信号。当Bit文件加载运行时,必须通过配套的Debug工具观察指定的信号波形,但是受限于Block RAM的容量以及信号优化等原因,如此调试的效率比较低。

FPGA原型验证平台的分类与选择

FPGA原型验证平台基本可以分为两大类,自研的原型验证平台和商业的原型验证平台。而这种选择则基于自身项目决定。

自研的原型验证平台

一些公司会选择使用自研,因为它们内部就有硬件设计部门,所以会直接从Xilinx或者从Intel采购FPGA,自行设计研制的FPGA平台。由于同属一个体系,针对新的项目或者新的原型验证平台需求,能够快速进行实现平台更新或者重新设计,并且可以定制化一些特殊的接口来满足自己芯片的某些特殊应用。

商业的原型验证平台

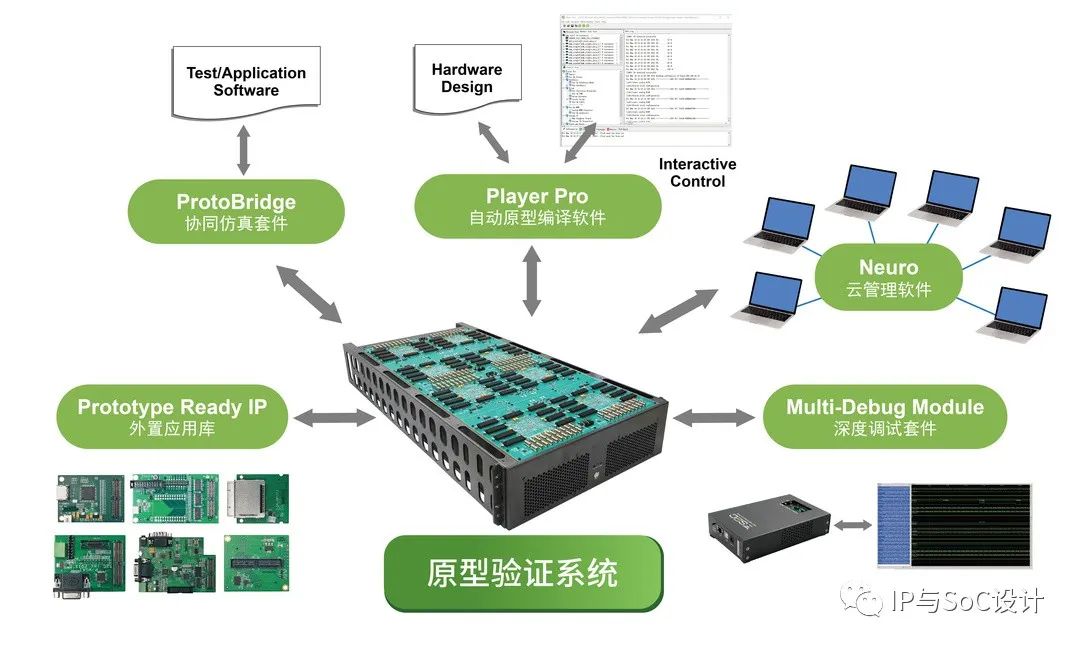

国微思尔芯-S2C

S2C公司是一家国内的 FPGA 快速原型验证解决方案供应商,他提供丰富种类的FPGA原型验证硬件平台。芯神瞳逻辑矩阵 Logic Matrix(LX)是国微思尔芯结合多年的原型验证产品经验,与当前高端分割、互联技术相结合所推出的高密原型验证平台。芯神瞳逻辑矩阵 LX 每个平台均配备了8颗 FPGA,LX1 选用的是赛灵思 (Xilinx) 的 Virtex UltraScale VU440,LX2 选用的是Virtex UltraScale+ VU19P,并且都能搭配使用芯神瞳自动原型编译软件、深度调试套件、协同仿真套件、以及外置应用库来快速搭建原型验证环境。除了硬件平台,S2C还提供了Prodigy系列软件。其中Player Pro能提供基于网表(EDIF)的自动分割功能。

·高性能高密多核硬件

·自动设计分割

·深度调试系统

·丰富的接口库

Synopsys公司的HAPS系列

HAPS是Synopsys公司推出的FPGA原型验证平台,该平台自2003年第一代HAPS-10起,到目前已经发展到HAPS-100。HAPS原型验证平台是一个集成解决方案,包含了硬件部分和软件部分。被广泛应用的HAPS80系列,发布于2014年,最大规模的硬件平台HAPS80-S104,内含4颗Xilinx的VU440 FPGA,及支持多用户模式和多台级联(最高可达64台)模式来满足不同设计的需求。集成软件除了提供编译,综合等功能,最大的亮点是支持多FPGA和多台HAPS的Auto Partition(自动分割),同时拥有强大的调试能力,比如DTD(深度跟踪调试)和GSV(全局信号可见)功能。

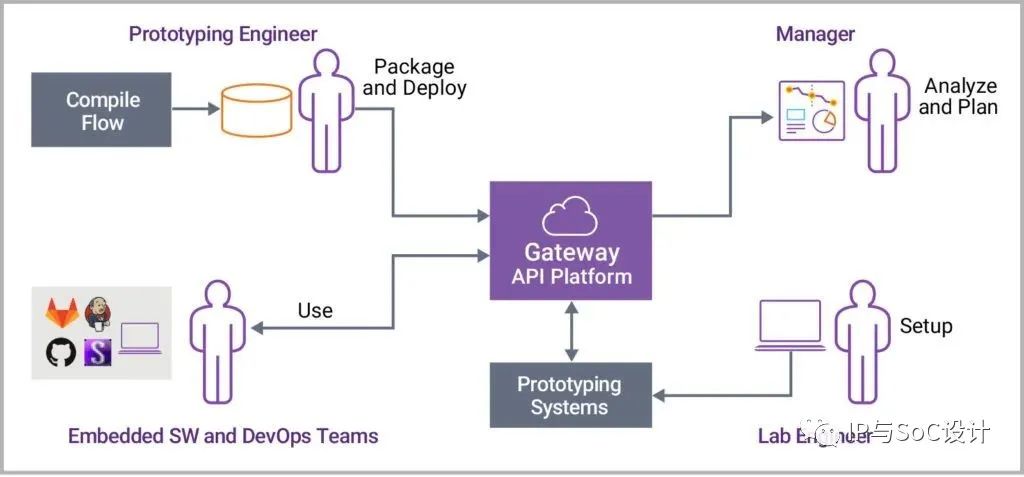

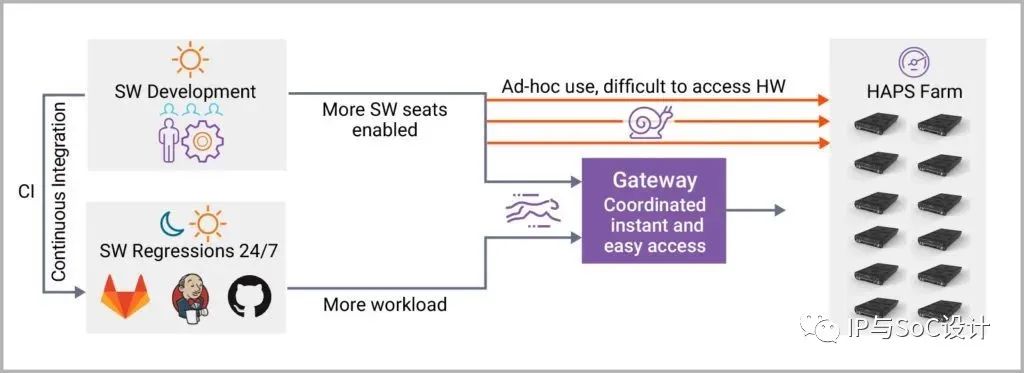

新思的云原生Web

Cadence公司的Protium系列

Cadence公司在FPGA原型验证平台上起步比较晚,2017年尝试推出了第一代FPGA原型验证平台Protium S1,于2019年发布了改进的第二代Protium X1。Protium X1 硬件采用Blade/Rack结构,一个Blade/Rack包含了6颗Xilinx VU440 FPGA,集成软件除了支持编译,综合以外,也支持跨FPGA的Auto Partition(自动分割),同时支持DCC(Data Capture Card)调试等。2021年,发布了Protium X2系统。新一代系统基于下一代硬件仿真核心处理器和 Xilinx UltraScale+ VU19P FPGA,将为客户带来2倍容量提升和1.5倍性能提升,以更少的时间为大规模芯片验证完成更多次数的迭代。

除此之外,国内还有一些优秀的公司提供FPGA原型验证工具,例如亚科鸿禹和芯启源。

亚科鸿禹

芯启源

IP供应商详情可见:https://www.ip-soc.com/vendors(点进阅读原文进入)

本文综合自网络

参考资料:

1、https://blog.csdn.net/zhajio?type=blog

2、https://zhuanlan.zhihu.com/p/401611922

3、https://zhuanlan.zhihu.com/p/445578718

4、https://blog.csdn.net/pqb777/article/details/120172467

5、http://www.cnblogs.com/dpc525/p/4999544.html

本文来源:IP于Soc设计、ZYNQ

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有,如涉及侵权,请后台联系小编进行处理。

END

往期精选

FPGA技术江湖广发江湖帖

无广告纯净模式,给技术交流一片净土,从初学小白到行业精英业界大佬等,从军工领域到民用企业等,从通信、图像处理到人工智能等各个方向应有尽有,QQ微信双选,FPGA技术江湖打造最纯净最专业的技术交流学习平台。

FPGA技术江湖微信交流群

加群主微信,备注姓名+公司/学校+岗位/专业进群

FPGA技术江湖QQ交流群

备注姓名+公司/学校+岗位/专业进群