二十年前,英特尔开创了PCIe(PCI Express)技术,但存储成本不断增加、数据爆炸式增长、计算和带宽开始失衡,PCIe逐渐乏力。2019年,英特尔又提出一种开放性互联协议——Compute Express Link(CXL),能够让CPU与GPU、FPGA或其他加速器之间实现高速高效的互联,从而满足高性能异构计算的要求。

#

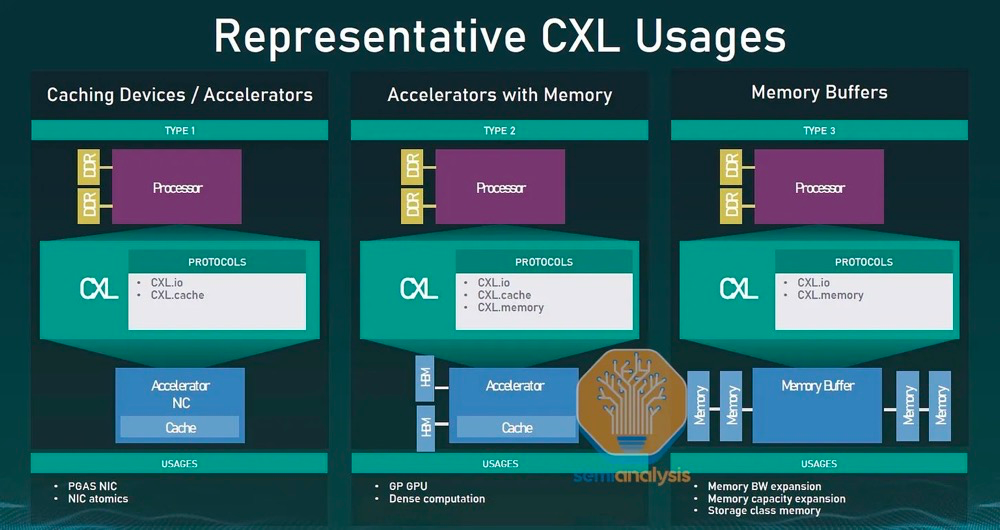

类型 1 设备

智能网卡等加速器通常缺少本地内存。通过 CXL,这些设备可以与主机处理器的 DDR 内存进行通信。

#

类型 2 设备

GPU、ASIC 和 FPGA 都配备了 DDR 或 HBM 内存,并且可以使用 CXL 使主机处理器的内存在本地可供加速器使用,并使加速器的内存在本地可供 CPU 使用。它们还位于同一个缓存一致域中,有助于提升异构工作负载。

#

类型 3 设备

可以通过 CXL 连接内存设备,为主机处理器提供额外的带宽和容量。内存的类型独立于主机的主内存。

#

CXL.io

该协议在功能上等同于 PCIe 协议,利用了 PCIe 的广泛行业采用和熟悉度。作为基础通信协议,CXL.io 用途广泛。

#

CXL.cache

该协议专为更具体的应用程序而设计,使加速器能够有效地访问和缓存主机内存以优化性能。

#

CXL.memory

该协议使主机(例如处理器)能够使用load/store命令访问设备附加的内存。

类型 1 设备:CXL.io + CXL.cache

类型 2 设备:CXL.io + CXL.cache + CXL.memory

类型 3 设备:CXL.io + CXL.memory

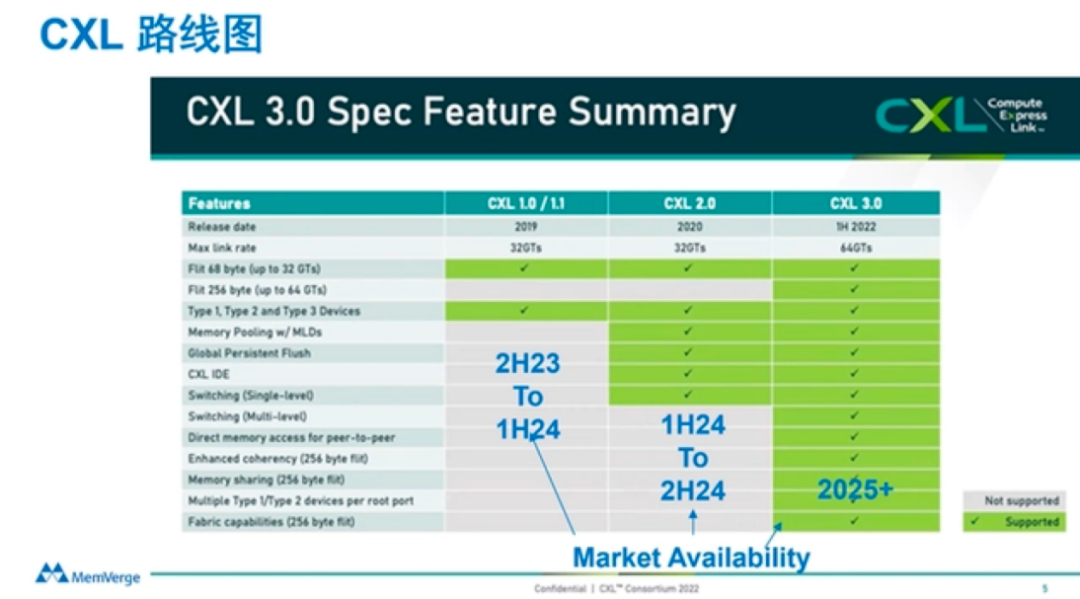

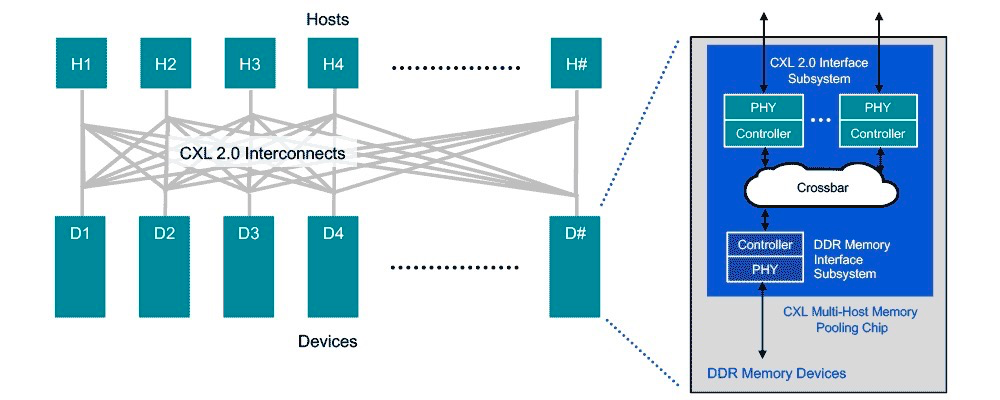

内存池

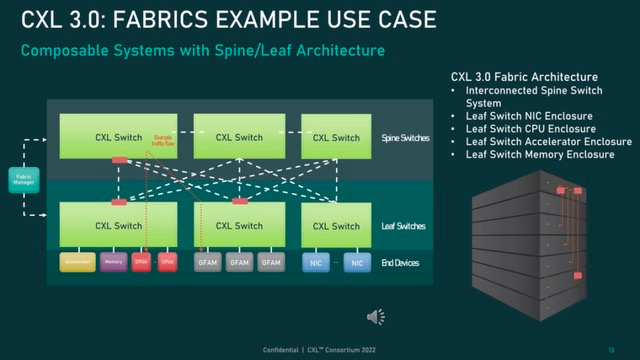

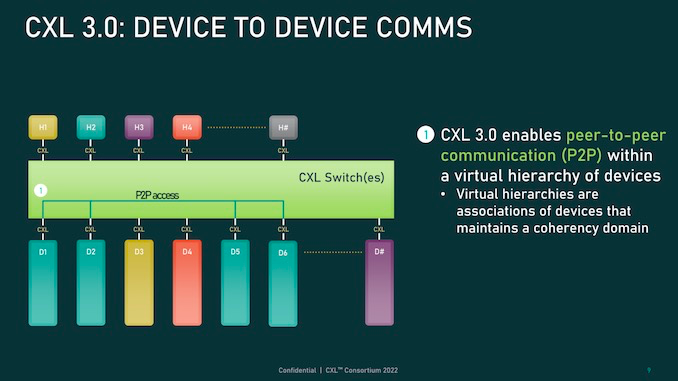

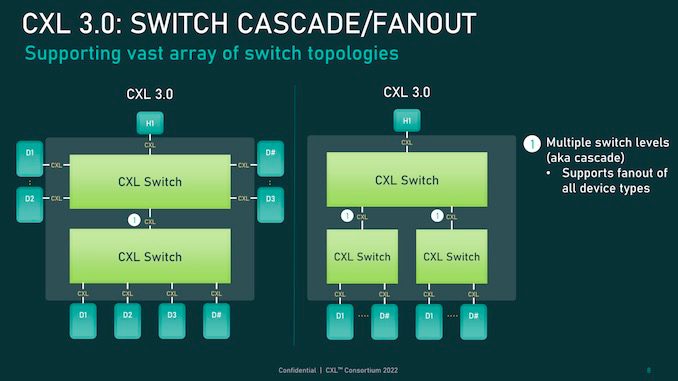

Switching

按需内存

完整性和数据加密 (IDE)

信令扩展到 64 GT/s