全栅极(GAA,Gate-all-around)将取代finFET,但它带来了自己的一系列挑战和未知数。

虽然只有12年的历史,但finFET已经走到了尽头。从3纳米开始,它们将被全栅极(GAA)所取代[1],预计这将对芯片的设计方式产生重大影响。

GAA目前有两种主要类型--纳米片和纳米线。对于纳米片,以及纳米片和纳米线之间的区别,人们有很多困惑。业界对这些设备仍然了解不多,也不知道一些问题在长期内会有多大影响。与任何新设备一样,第一代设备是一个学习工具,随着时间的推移,会有改进。

我们为什么要做这种改变?"如果finFET间距可以继续扩大,人们就会一直使用finFET,"imec研发副总裁Julien Ryckaert说。"问题是finFET不能扩展,因为你需要把栅极、工作功能堆栈插在两个鳍之间。根据这些设备的构造的性质,你不得不将两个鳍片分开15到20纳米。所以你有这个悬崖。由于这种量化,如果你继续将你的标准单元扩大1纳米,你的有效面积就会减少1纳米,这可能会导致整个鳍的消失。这就是人们说'我们需要找到一个解决方案'的时刻"。

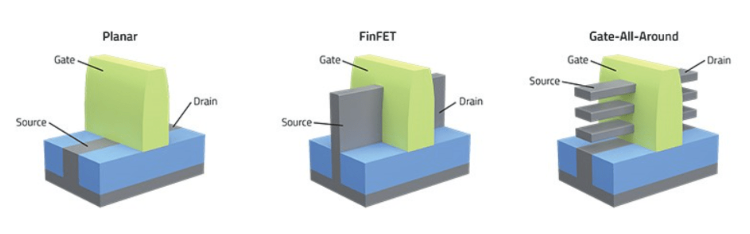

图1:平面晶体管与鳍式场效应晶体管与全栅极晶体管的对比 资料来源:Lam Research: 来源:Lam Research

全栅极(GAA)与finFET类似。"FinFETs将平面晶体管翻转过来(见图1),这样鳍的高度就变成了等效平面晶体管的宽度,"Atomera的首席技术官Robert Mears说。"由于加工限制固定了翅片的高度,晶体管的宽度只能通过使用额外的翅片进行不连续的变化。GAA回到了一个平面几何形状,但现在是垂直堆叠的平面纳米片。因此,原则上,宽度可以连续变化"。

这不太可能发生。"imec的Ryckaert说:"在调整活性宽度方面将有更大的灵活性,因为它是一个平面结构,理论上你可以连续改变片材的宽度。"然而,代工厂极有可能限制设计者玩弄任意纳米片宽度的能力,他们会强制限制。"

这很可能是因为创建模型的时间和难度。"每个器件尺寸都必须单独进行表征、鉴定和建模,增加了开发PDK的成本,"Atomera的Mears说。"在库的层面上,我们可以期望更好地优化逻辑和SRAM,使用宽度作为额外的变量来优化电源性能的权衡。"

变异性驱动GAA

但转向GAA的最大问题是变异性,这是影响产量和性能的一个关键因素。

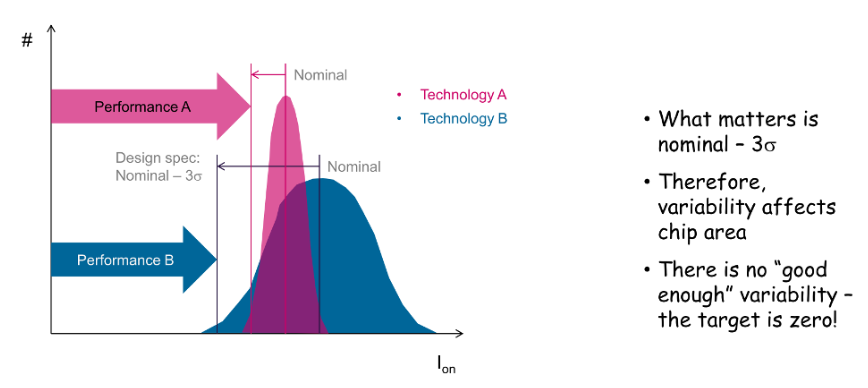

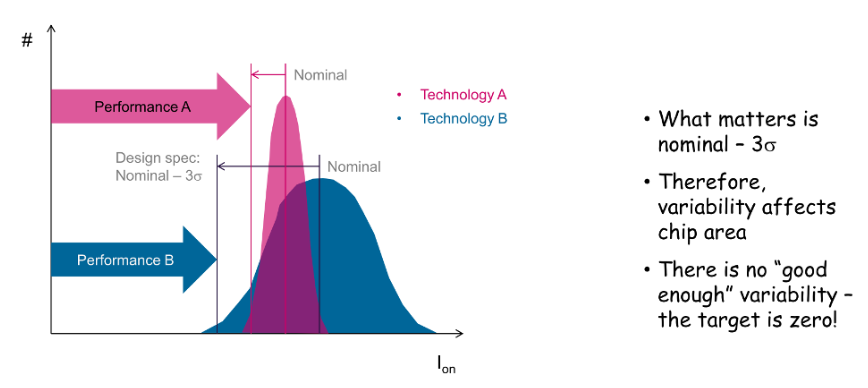

Synopsys公司TCAD产品组的研究员Victor Moroz说,"假设你有技术A(见图2),你有一定的晶体管强度分布,以晶体管的驱动电流来衡量,它们有一些额定的行为和分布。但芯片上的十亿个晶体管不可能都是一样的。有些是略有偏差的。通常情况下,它有些类似于高斯分布。对电路设计者来说,重要的不是标称行为,而是工艺角落,也就是标称减去三个西格玛的东西。想象一下,你有另一种技术B,它有更好的标称性能,但有更大的变化性。如果它的变异性大得多,可能是设计者被迫按照这个工艺角进行设计,那么拥有更好的标称性能就没有用了。GAA技术是一种控制甚至可能减少变异性的方法。"

图2:变异性的影响。资料来源: 新思科技

随着鳍式晶体管越来越小,变异性也在增加。"当一个finFET变成一个鳍时,变异性会变得非常有问题,"Ryckaert说。"有很好的迹象表明,导致变异性的机制在纳米片中可能会得到更好的控制。翅片FET的一个大问题是翅片轮廓,它可以在翅片脚下引起相当大的变异性。对于纳米片,因为你是从一个预先定义的超晶格外延生长开始的,这些堆栈是由原子控制的。纳米片的厚度是由原子控制的,所以你的片子厚度,这是一个非常重要的变化来源,将有更好的控制。"

纳米片与纳米线

这些术语几乎可以互换使用,但它们并不是一回事。"纳米线是一个对通道进行完全控制的想法,通过让栅极包裹着一个圆形的硅通道,"Ryckaert说。"这就是你将得到最好的静电,最好的通道控制。"

但这是一种权衡。"Mears说:"虽然纳米线确实改善了短通道的控制,但由于它的几何尺寸小,通常是5纳米乘5纳米的数量级,它降低了驱动电流。"纳米片结构是介于鳍状FET和纳米线之间的一部分。片状结构的高度也是大约5纳米,但宽度要大得多,而且可以连续变化。栅极静电控制比finFET好,但比纳米线差,因为虽然纳米片的栅极确实环绕所有四面(因此称为 "栅极环绕"),但其较大的宽度导致边缘的栅极控制减少。另一方面,与两者相比,纳米片的驱动电流有很大的改善。目前的GAA结构应该被描述为纳米片而不是纳米线"。

SRAM推崇折衷方案。"纳米片的厚度大约是5纳米,宽度大约是20或30纳米,"Synopsys的Moroz说。"这对逻辑来说是典型的。但是对于SRAM来说,没有空间拥有一个宽的通道,所以对于SRAM来说,通道宽度将是10纳米或更小,这几乎是纳米线。"

现在你必须处理好后果。"纳米线在静电方面更好,但那个圆的周长超小,"Ryckaert说。"你需要建立整个栅极,以及围绕它的这个大的源-漏极,这将引入与你在板块中一样多的寄生因素,但驱动力非常差。在很小的电流下,你将会有很多寄生器件。对于SRAM来说,纳米片是一个非常糟糕的想法,仅仅是因为几何尺寸的问题。鳍的足迹是5纳米。纳米片迫使宽度为15纳米或20纳米,所以这只是你所消耗的房地产,这意味着你的SRAM不能与纳米片一起扩展。"

SRAM的可变性也会造成问题。"对于逻辑来说,电路有一定的深度,"Moroz说。"想象一下,你的晶体管沿着那条路是随机变化的,但因为你可能有15个阶段,所以有一些自我平均的情况发生。对于SRAM来说,你所拥有的只是两个相邻的反相器。总共有两个NMOS和两个PMOS晶体管,如果它们不匹配,这就是一个问题。"

也有其他问题。"掺杂物的变化会导致阈值电压的明显变化,"Mears补充说。"随机掺杂物波动(RDF)的变化会导致器件之间的显著差异--即使是匹配的器件--这导致SRAM的性能和产量降低,并为逻辑器件的时序模型增加额外的最坏情况下的保护带。"

有多少层?

制造GAA的一个额外变量是纳米片的数量。"Mears说:"PPAC(功率、性能、面积/成本)限制将推动更多的层数,特别是随着纳米片的不断扩展。"例如,假设其他一切保持不变,从3层纳米片到4层,性能提高了近33%,但芯片尺寸应保持不变,晶圆加工成本应仅有小幅增长。GAA的经济效益依赖于堆叠多个GAA片,以达到有效的密度,因此增加层数的压力肯定是存在的。"

但这并不完全是变量。"很难相信它将被限制在两个,而超过五个也将是非常困难的,"Ryckaert说。"这归结于简单的数学。仅仅通过计算电容和通道宽度就可以得到90%的答案。你还需要计算在源-漏极和栅极之间有多少表面,你需要围绕一定的硅面积进行封装。对于最大化驱动力和最小化电容来说,周长才是最重要的。最大化驱动力和最小化电容仅仅是表面与周长的比率。如果你比较一个三鳍鳍片FET器件,没有任何纳米片结构可以打败它。但由于鳍式晶体管的量化性质,单元高度损失一纳米就意味着失去一个鳍。纳米片为你提供了你的逻辑扩展所需的纳米级的扩展。然后,纳米片将开始与鳍式晶体管相比大放异彩。这发生在三到四片左右。五片就不行了,因为源-漏的电阻,以及结构的电阻。你意识到,第五片刚好足以驱动你为使结构变高而增加的寄生物。你只是在你自己的结构中消耗了电流。"

在一个芯片内改变这个也没有什么意义。"在同一个芯片上改变层数是不容易的,"莫罗兹说。"一旦你决定了某个数字,这将可能适用于整个芯片。对于高性能计算,你最好采用四层。对于移动设备来说,你最好用三层。"

性能

每个节点都有降低电压和功率的愿望。"Mears说:"降低电压供应的压力始终存在,因此也就降低了功率,但Vt是受限制的。"它不能再降低了,因为它是由Ioff规格和有限的亚阈值斜率(SS)设定的,由于热力学(kT/q),它不能低于每十年60mV。目前正在研究能进一步降低SS的新型电路元件,如铁电栅电介质的 "负电容",但这些元件不会很快进入批量生产。对Vdd的另一个限制是SRAM的Vmin,它为给定的错误率设定了可能的最低电源电压。由于嵌入式SRAM通常是在电压降低时最先失效的模块,因此Vmin往往设定了最低的电源电压。"

在功率方面会有一些改进。"过去十年的每一项后续技术,以及今后的发展,都会给你在相同性能下降低20%左右的开关功耗,"Moroz说。"泄漏受到可变性的影响,因为对于泄漏来说,更重要的是快角,即晶体管泄漏的地方。所以拥有更严格的可变性有助于解决这个问题。"

但是,关于动力还有未知的方面。"热量的一个来源是自热或焦耳热,"Ansys的产品营销总监Marc Swinnen说。"对于GAA,你在这些门中有多个纳米片,它们被绝缘体所包围,这不是一个好导体。器件的自热将有所不同,但我们还没有足够的信息来知道它的影响有多大。我们最终会从铸造厂得到这些数字。局部的热源会导致热峰值,这可能会影响电迁移,而电迁移对温度的敏感性是指数级的。如果局部的几个晶体管趋于变热,那么与芯片的平均温度相比,周围的金属会有不同的电迁移情况。你不能只使用平均数。"

下一步是什么?

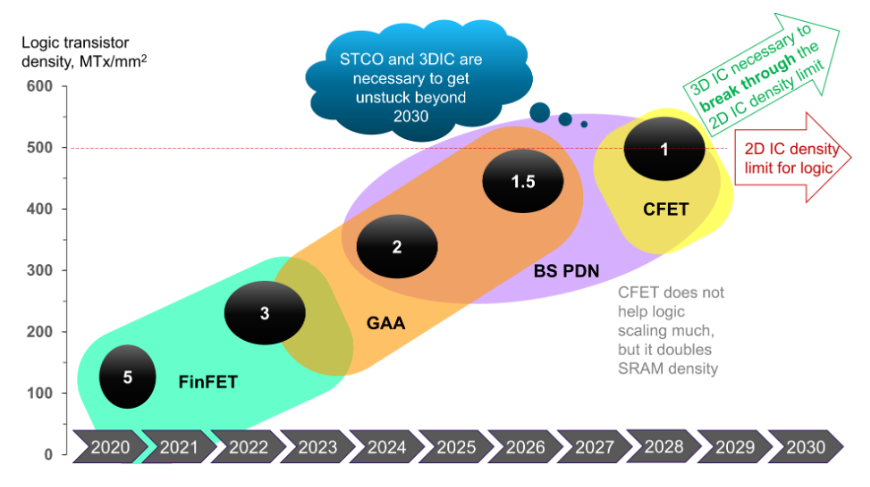

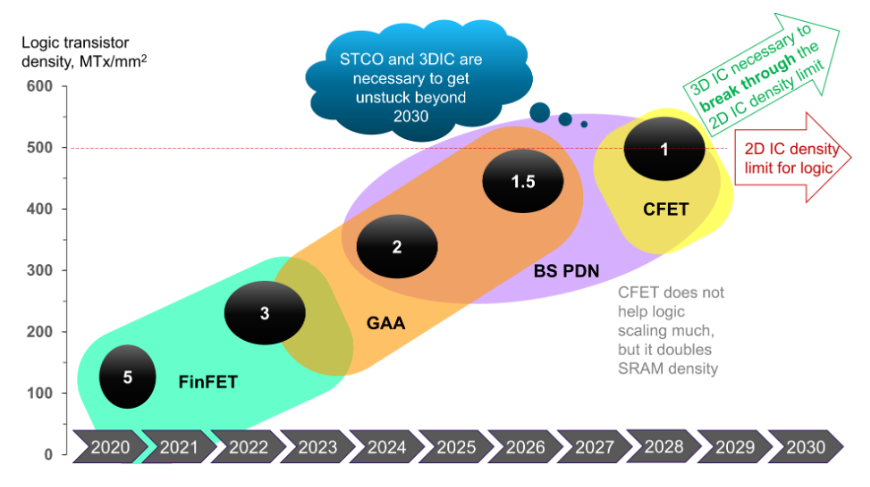

很明显,随着设备的缩小,变化将成为常态。"Ryckaert说:"我们期望看到纳米片至少用于两个节点,但在那之后,纳米片结构的扩展将变得非常棘手。"我们已经提出了叉状结构,这是对纳米片概念的一种调整。它的扩展特性将使另外两个节点成为可能。然后是CFETs,(赠送的FET堆叠),它受到纳米片的启发,但采用堆叠配置(见图3)。"

GAA可能具有与finFET相似的寿命。"最有可能的是,它将存在10年,"莫罗兹说。"但在2030年左右,我预计行业将转向堆叠式晶体管,即你有两个GAA晶体管堆叠在一起。有些人称它为CFET,互补FET,或堆叠式晶体管。"

图3:逻辑技术路线图。来源: Synopsys

这时就变得有点困难了。"在CFET之后,我们就完成了二维集成电路,"Moroz补充说。"我们预计晶体管密度将停止在每平方毫米密度50亿个晶体管的逻辑上,而对于SRAM来说,这将是每平方毫米10亿个。然后我们就被困住了,因为虽然你可以尽可能地挤压晶体管,但一切都将受到连接晶体管的电线的限制。唯一的出路是堆叠小芯片。

参考资料

1. 三星宣布它将在3纳米时推出GAA FET。英特尔和台积电计划在2纳米时引入它们。

本文译自:semiengineering.com