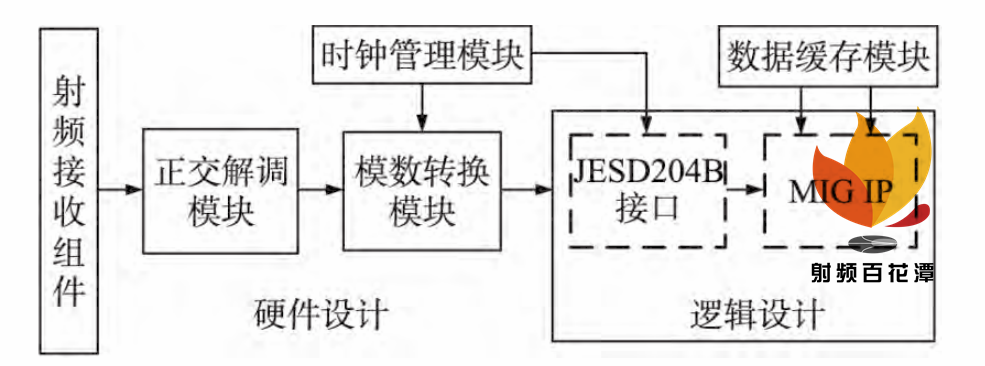

为了解决传统转换器传输接口传输速率低、抗干扰差、布局布线面积大等问题,设计了一种基于 JESD204B 的射频信号高速采集系统。系统对接收到的射频信号进行下变频处理,通过高速 ADC 对解调基带信号直接采样,采样后的数字基带信号通过自主设计的 JESD204B 接口逻辑传输至 FPGA 并缓存。测试结果表明,系统可实现 1.0 Gsample/s 采样率的直接采样,数据传输速率可达 10 Gbit/s,且数据链路稳定可靠。

1

系统总体设计

2

硬件设计

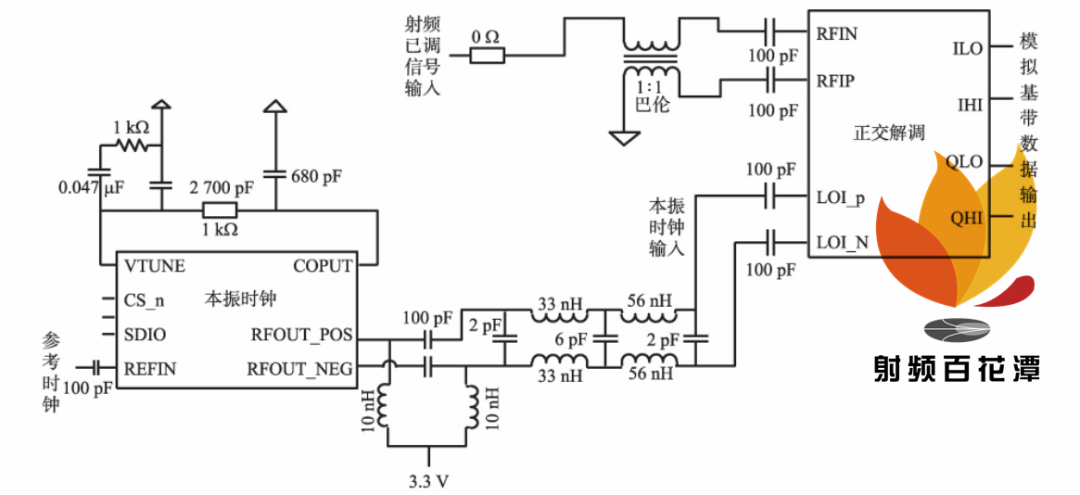

2.1 正交解调模块

正交解调模块通过宽带正交解调芯片和射频本振芯片组合实现下变频功能。所采用的正交解调芯片 ADL5380 是一款宽带正交 I/Q 解调器,涵盖从400 MHz 到 6 GHz 的 RF/IF 输入频率范围,3 dB 解调输出的 IQ 基带带宽可达 390 MHz,具有出色的动态范围,适用于要求苛刻的直接变频应用。在工作过程中,本振芯片 ADF4351 为正交解调芯片提供2.4 GHz 本振时钟信号,本振时钟信号输入被正交相位分离模块拆分为两路正交本振时钟,分别作为两路相互正交的混频模块的本振输入;射频信号经过电压 - 电流转换后,分为两路大小相同的分支,分别输入两路相互正交的混频模块,与本振信号进行混频操作;混频操作完成后,信号通过输出接口运放转换为差分输出信号进入下一模块。

如图 2 所示,在正交解调输入部分硬件电路中,本振信号传输路径为差分信号传输,路径两端均串接电容形成直流耦合且中部插入低通滤波器,抑制本振信号中的直流噪声和偏斜抖动;射频信号输入路径中插入 1 ∶1 巴伦(平衡 - 不平衡变压器),实现单端转差分和阻抗匹配功能,降低射频输入路径反射噪声。

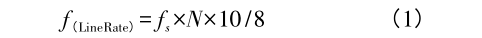

2.2 模数转换模块

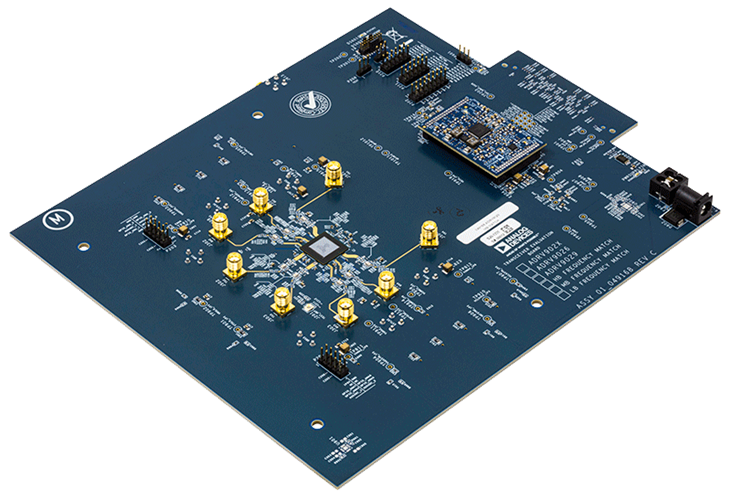

为了使被采样基带信号满足模数转换芯片要求,模数转换模块中采用可变增益放大器 AD8366 作为模数转换芯片的输入驱动,对正交解调后的模拟基带信号进行调理,电路原理如图 3 所示。系统采用的模数转换芯片 ADS54J60 是一款低功耗、高带宽 16 位、采样速率高达 1.0 Gsample/s 的双通道模数转换芯片(ADC),满足输入模拟基带信号的采样要求。芯片内部包含两个相互独立的流水线架构 ADC 核心,支持JESD204B 串行接口,每个 ADC 可支持 2 或 4 条数据通道,数据传输速率可达 10 Gbit/s 。ADS54J60 的数据输出采用8B/10B 编码,其通道线路速率 f (LineRate)与采样率 f s ,通道数据位数 N 满足以下关系:

通过 SPI 接口配置 ADC 为双数据通道输出,即将 16 位采样数据分为两路 8 位数据同时输出,从而同时实现了 1.0 Gsample/s 采样率及 10 Gbit/s 的线路速率。

图 3 模数转换模块电路示意图

2.3 时钟管理模块

高质量的时钟是确保 JESD204B 传输链路稳定的关键。JESD204B 协议要求发送接收端器件时钟来自同源时钟,因此,时钟管理模块需要分别为 ADC 与FPGA 提供 JESD204B 器件时钟。LMK04828 是一款超低抖动时钟调理器,可专门配置为 JESD204B 转换器提供器件时钟和确定性延迟对应的 SYSREF 时钟,最大时钟输出频率为 3.1 GHz。其内部寄存器也通过SPI 接口配置,以改变时钟分频与输出。

3

逻辑设计

3.1 JESD204B 接口模块

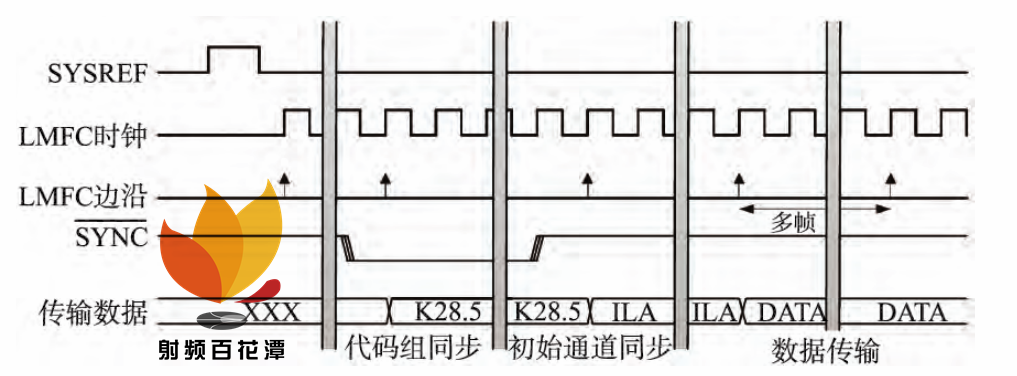

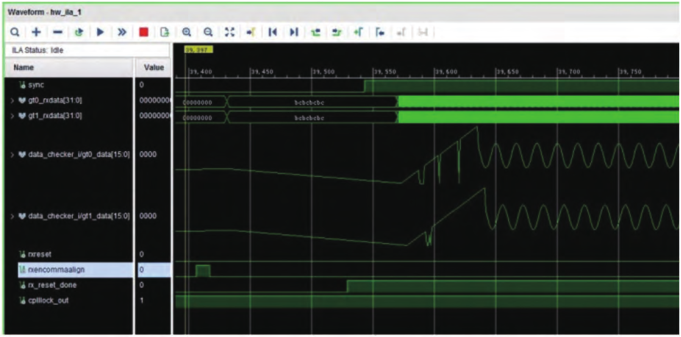

系统在 Xilinx FPGA Virtex-7 的高速串行收发器 GTX 硬 件 基 础 上,针 对 本 系 统 需 要 设 计 了JESD204B 接 收 端 相 关 逻 辑。逻 辑 主 要 实 现JESD204B 协议的帧时钟对齐、代码组同步、初始帧通道同步与数据传输 4 个阶段,如图 4 所示。

图 4 JESD204B 传输阶段时序图

通过 Xilinx GTX IP 设置 GTX 接收数据通道为32 位,以保证对 ADC 发送数据有效接收与缓存。上电逻辑运行后,首先使能复位信号初始化 GTX 内部寄存器,等待对应复位完成信号 RXRESETDONE拉高。

通过器件时钟采样输入的 SYSREF 时钟上升沿生成本地多帧时钟(LMFC)与对应的帧时钟,LMFC用于后续 3 个阶段的事件判定与对齐,即完成帧时钟对齐阶段;FPGA 拉低与 ADC 之间的同步信号SYNCb,初始设置 GTX 的对齐识别字符为 K28.5 字符,等待 ADC 发送端响应并发送 K28.5 字符后,使能 GTX 的接收对齐信号 RXCOMMAALIGN,当 GTX识别对齐 4 个连续的 K28.5 字符后,也即对应标志位 CHARISK[3:0]全为高,代码组同步完成;FPGA拉高同步信号 SYNCb,ADC 发送端在 SYNCb 拉高后的下一个 LMFC 边沿开始发送 4 个连续的 ILA 多帧序列,完成初始帧通道同步;最后进入数据传输阶段,ADC 开始并持续在链路上发送有效采样数据。

3.2 数据缓存模块

数据缓存模块基于 MIG IP 的乒乓读写操作控制方案,利用对不同存储区域的读写切换有效降低预充电命令与激活命令之间的时间间隔,并且使用超长突发操作减少发送列寻址和读写命令所造成的时间延时 ,极大地提高数据传输效率。

4

测试分析

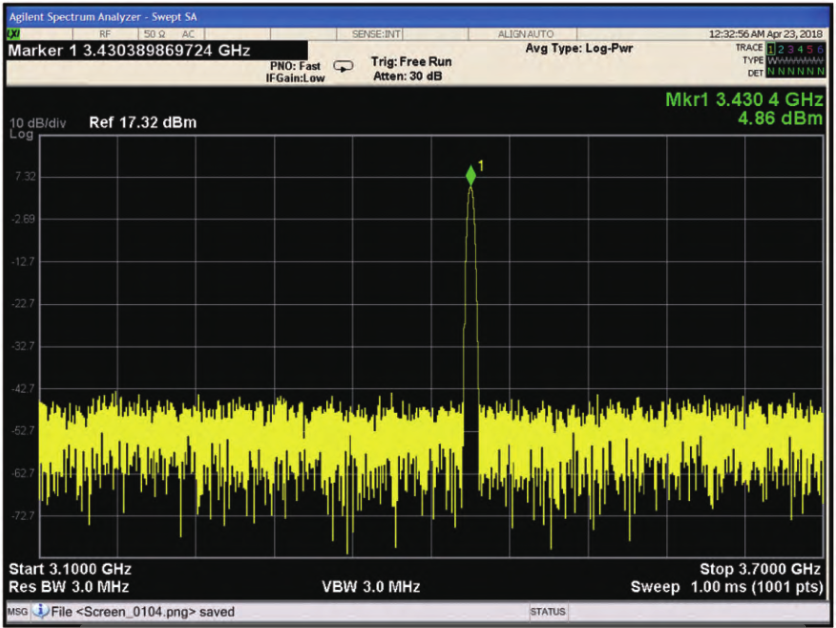

系统使用罗德与施瓦茨公司 SMW200A 矢量信号发生器作为系统测试输入,设置正余弦基带信号频率为 30 MHz,射频输出载波频率为 3.4 GHz,观察其射频输出频谱,如图 5 所示。从图 5 观察可知,在600 MHz 的扫描带宽中,只出现单音 3.430 GHz 的射频信号频谱,无其他噪声谐波干扰,射频输入信号频率成分单一,信号发生器生成单音射频已调信号正确无误。

图 5 射频测试输入信号频谱

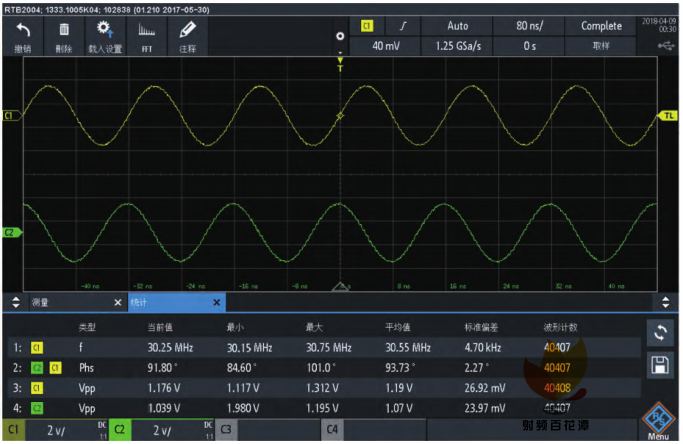

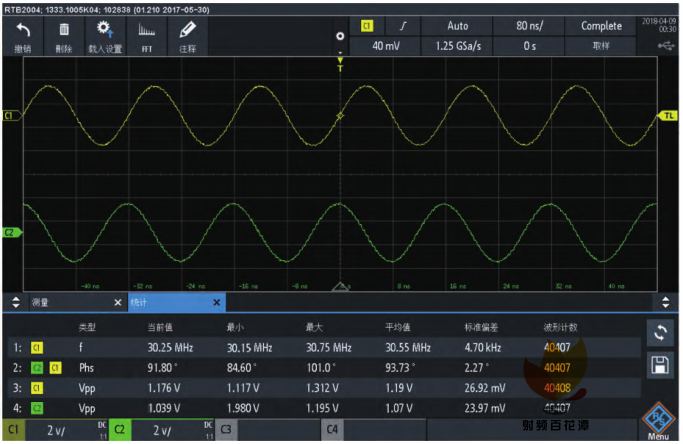

采用罗德与施瓦茨公司 RTB2004 示波器对正交解调后的正交基带信号进行测试,如图 6 所示,并通过 Xilinx 的调试核心 ILA 抓取 JESD204B 接口逻辑接收的 FPGA 内部缓存数据,如图 7 所示。可以看出,正交解调后的基带信号频率为 30 MHz,与初始输入设置一致,数据传输链路按照 JESD204B 协议阶段逐步建立,且接收基带信号数据良好无误。

图 6 解调后的模拟正交基带信号

5

结论

基于 JESD204B 的射频信号高速采集系统设计,采用 JESD204B 传输协议及相关转换器,实现了对接收到的射频信号的下变频处理,以及对正交解调后的基带信号的直接采样与高速传输。系统可实现 1.0 Gsample/s 采样率的直接采样,传输速率可达10 Gbit/s,且传输数据稳定无误。此外,针对系统需要求,自主设计了 JESD204B 接收相关逻辑,减少了使用资源,降低了开发成本。

来源:电 子 器 件

声明:

投稿/招聘/推广/宣传 请加微信:15989459034