今天我们将讨论时钟如何影响精密 ADC,涉及时钟抖动、时钟互调和时钟的最佳 PCB 布局实践。

如本系列第 9 部分所述,所有数据采集 (DAQ) 系统都需要一个参考点。在那篇文章中,参考点是一个电压电平,它与模拟输入信号进行比较以生成输出代码。然而,DAQ 系统还需要另一种类型的参考点,尽管不一定与电压相关。

在 DAQ 系统中,时钟作为时间参考,以便所有组件可以同步运行。对于模数转换器 (ADC),准确且稳定的时钟可确保主机向 ADC 发送命令,并且 ADC 以正确的顺序从主机接收命令且不会损坏。更重要的是,系统时钟信号使用户能够在需要时对输入进行采样并发送数据,从而使整个系统按预期运行。

尽管您可能将时钟视为数字输入信号,但这些组件会影响精密 DAQ 系统的模拟性能。为了进一步了解时钟如何影响精密 ADC,我们将讨论这些与时钟信号相关的主题:

时钟抖动;

时钟互调;和

时钟的最佳印刷电路板 (PCB) 布局实践。

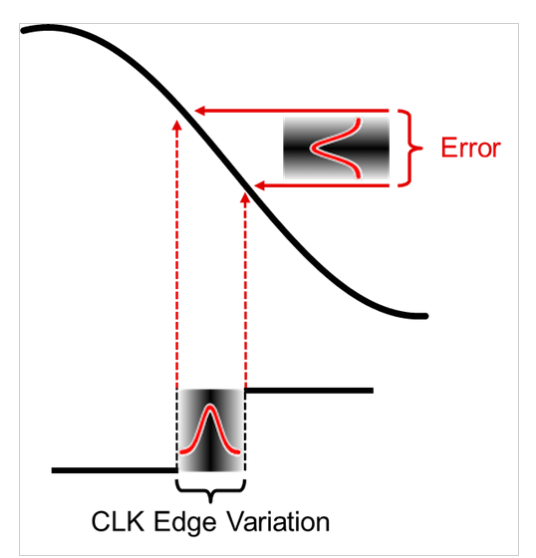

虽然您可能期望 ADC 的采样周期完全恒定,但始终与理想情况存在一些偏差。“时钟抖动”是指时钟波形边沿从一个周期到下一个周期的变化。由于所有 ADC 都使用时钟边沿来控制采样点,因此时钟边沿变化会导致采样实例出现偏差。这种偏差会导致出现在转换结果中的非恒定采样频率,作为另一个噪声源。

与本系列迄今为止讨论的大多数噪声源类似,时钟抖动是随机的,并遵循高斯分布。因此,采样不确定性误差也是高斯的,就像热噪声一样。最终,时钟抖动对 ADC 性能的影响主要是 ADC 的本底噪声增加,随后是信号链的总热噪声。图 1 显示了由正弦输入信号上的时钟抖动引起的采样边沿变化。

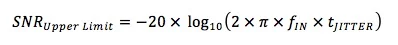

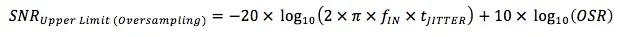

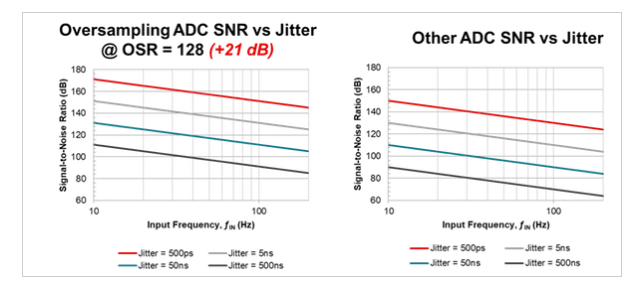

热噪声增加的量取决于输入信号的压摆率和时钟源中的时钟抖动量。您可以使用公式 1 计算 ADC 信噪比 (SNR) 的理论上限:

其中 fIN 是输入信号频率,tJITTER 是时钟源的抖动规范。对于具有较高频率成分的信号,您可以预期输入信号压摆率会更高,而时钟抖动导致的 SNR 降级会更糟。

过采样转换器(如 delta-sigma ADC)的一个主要好处是,理想的 SNR 在使用更高的过采样率 (OSR) 时会得到改善。过采样在定义的时间段内平均多次转换,这反过来又平均了一些由时钟抖动引起的采样变化。等式 2 量化了由于过采样而导致的 SNR 改进,它只是等式 1 的扩展,增加了一个与 Δ-Σ ADC 的 OSR 相关的项:

为了直观显示具有过采样和没有过采样的 ADC 之间的性能差异,图 2 绘制了方程 1 和 2 作为输入信号频率和抖动的函数。每个图都包括四种不同时钟抖动规格(0.5 ns、5 ns、50 ns 和 500 ns)的曲线。图 2a 表示过采样 ADC 的 SNR,而图 2b 表示没有过采样架构的 ADC 的 SNR。

考虑到过采样的好处,与图 2b 中的等效抖动规格曲线相比,图 2a 中的四个图提供了 21dB 的 SNR 改进。但是,两个图都说明了相同的效果:随着输入信号频率或时钟抖动量的增加,产生的 SNR 会降低。因此,具有更高 SNR 目标的应用可能需要更昂贵、更高功率的时钟解决方案来最小化抖动。

例如,德州仪器 (TI) ADS127L01的评估模块(EVM) ,一个512kSPS、24 位 delta-sigma ADC,使用 Abracon ASEMB-16.000MHZ-XY-T 低抖动振荡器。该振荡器提供 5 ps 的典型周期抖动规格,远低于图 2 中绘制的任何抖动规格。但是,如果您考虑低抖动振荡器的成本与性能权衡,您可能想知道这种选择是必要的或只是矫枉过正。

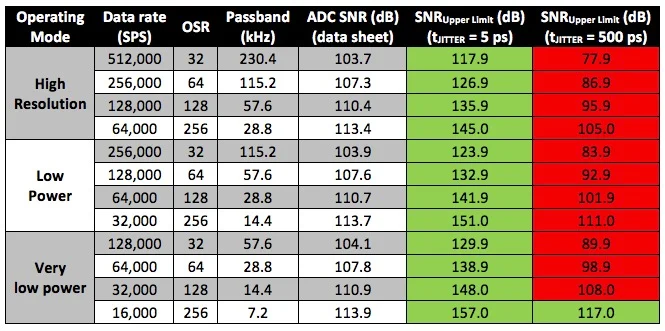

为了帮助回答这个问题,表 1 比较了 ADS127L01 使用“宽带 1”数字滤波器设置的数据手册噪声规范,SNR 上限是针对 5 ps 和 500 ps 时钟抖动计算得出的。SNR 上限计算使用数字滤波器通带频率作为“fIN”来表示最大输入信号频率,这是时钟抖动影响最明显的地方。

当 tJITTER = 5 ps 时,所有计算出的 SNR 值(以绿色突出显示)都大于 ADC 的数据手册 SNR 规格。使用该时钟源,您可以安全地假设时钟抖动产生的噪声不会成为您系统的主要噪声源。将其与以红色突出显示的条目进行比较,表示 SNR 值低于 ADC 的 SNR 规范,所有这些值均针对 tJITTER = 500 ps。在这种情况下,当使用全信号带宽时,来自时钟抖动的噪声实际上会限制 ADC 可实现的 SNR。

表 1. TI 的 ADS127L01“宽带 1”滤波器 SNR 与 5 ps 和 500 ps 时钟抖动的 SNRUpper 限制

表 1 和图 2 的另一个关键要点是增加 OSR(相当于降低 ADC 的输出数据速率)可以进一步提高 SNR 性能。通常,可以支持较慢输出数据速率的系统正在测量移动较慢的输入信号。由于时钟边沿的轻微变化实际上被“忽视”了,这些系统会因抖动而受到更少的噪声。

最后,降低时钟抖动引起的噪声的另一种方法是选择使用集成时钟分频器产生调制器采样时钟的 ADC,例如 ADS131A04。时钟分频器仅作用于两个输入时钟边沿之一(通常是上升沿),以产生不超过原始输入时钟频率一半的输出时钟频率。由于您可以合理地假设两个输入时钟边沿都存在一些抖动,因此将时钟一分为二可以有效地降低输出时钟上的抖动。如果您继续多次分频输入时钟,则可以进一步减轻输入时钟抖动对 ADC 的影响。

时钟源影响 ADC 噪声性能和增加系统噪声的另一种方式是通过时钟互调。几乎所有 DAQ 系统都有多个需要时钟输入的开关组件。在某些情况下,这些时钟输入可能需要来自不同时钟源的不同输入频率。

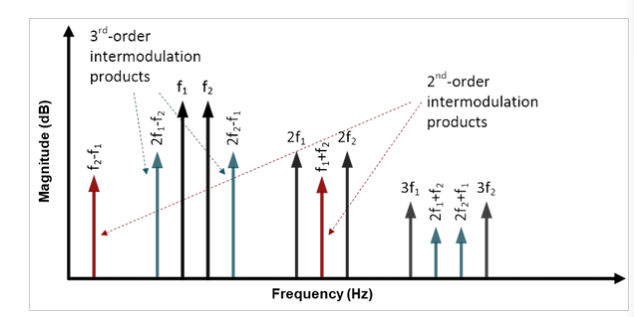

如果这些时钟源是离散的和异步的,它们可能会相互耦合并在频谱中产生音调。给定频率为 F1 和 F2 的两个时钟源,它们基频的差值或总和会产生互调音调。这些被称为二阶互调产物,如图 3 所示。

此外,基频与其他互调产物(包括它们的谐波)之间的和或差会产生额外的高阶音调。虽然这些音调可能存在于您感兴趣的信号带宽之外,但它们仍然可以混叠到 ADC 通带中并降低 SNR 和总谐波失真等 AC 规格。

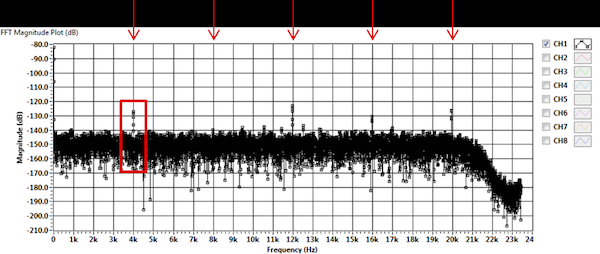

图 4 中的快速傅立叶变换 (FFT) 说明了这些互调效应。使用具有短路输入(0-V 差分输入)的 ADC,处理器时钟设置为 12 MHz,而 ADC 调制器时钟降低到 11.996 MHz,产生 4 kHz 的差异。

由于处理器和 ADC 时钟的差异,2 阶互调音出现在 4 kHz 的频谱中,并在 4 kHz 的倍数处产生额外的谐波。这说明了互调产物如何直接落入 ADC 的通带并产生噪声。

为了缓解这个问题,宽带应用通常使用一个时钟源来生成系统中使用的所有其他频率,以确保它们都是同步的。另一种有用的缓解技术是选择在感兴趣的信号带宽内最不可能产生音调的时钟频率和采样率。

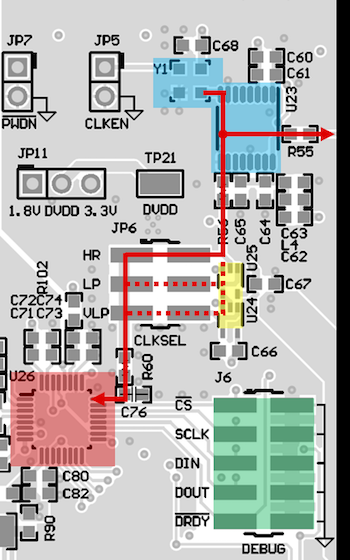

在为您的时钟源设计 PCB 布局时,请注意保持时钟信号尽可能干净。尽管它被视为数字输入,但将时钟信号视为另一个重要的模拟信号。最小化走线阻抗,将走线远离串行外设接口 (SPI) 信号和其他噪声电路,并考虑包括用于串联电阻器和并联电容器的 PCB 封装,以帮助处理反射或过冲。图 5 显示了来自ADS127L01EVM的示例时钟布局。

图 5 中的红线跟踪从源到 ADC(U26,以红色突出显示)的时钟路径。时钟路径从时钟源 (Y1) 开始,然后被送入时钟扇出缓冲器 (U23)。这两个组件在图 5 的右上角以蓝色突出显示。时钟扇出缓冲器生成原始输入时钟频率的两个相同副本:一个用于驱动 ADC,另一个用于驱动微控制器(通过 R55)。

为了进入 ADC,时钟信号继续通过一个与时钟缓冲器输出串联的 43 Ω 小电阻器 (R56),以帮助抑制反射。然后时钟信号连接到跳线 (JP6),该跳线选择三个不同的 ADC 时钟频率之一。另外两个时钟频率由两个 D 触发器(U24 和 U25,在图 5 中以黄色突出显示)产生。这些组件对时钟缓冲器输出进行分频以产生用于其他两种模式的时钟:“低功耗”(LP) 模式和“极低功耗”(VLP) 模式。所有三种模式选择也与原始时钟源同步。在图 5 中,红色实线穿过“高分辨率”(HR) 模式选择。

在跳线之后,选定的时钟信号在到达 ADC 时钟引脚之前通过另一个电阻器 (R60) 和一个并联电容器 (C76)。路径尽可能短且直接。SPI 接口信号(以绿色突出显示)也远离时钟输入,直到它们到达 ADC。

如果您遵循此处提供的时钟布局指南,但仍怀疑您的时钟正在降低 ADC 性能,则需要测试一些其他与时钟相关的问题。

如果 ADC 时钟输入引脚上的时钟信号显示过度的过冲和振铃,您可能需要通过添加或增加小型串联电阻器和并联电容器(分别为图 5 中的 R60 和 C76)的大小来进一步压摆时钟边沿。添加这些组件可以有效地将低通滤波器应用于时钟输入,同时保留基本时钟频率。

您可能还会注意到时钟边沿中的“搁架”或“阶梯”。这是由时钟信号沿走线传输并进入高阻抗输入时的反射引起的。串联电阻器将有助于抑制这些时钟反射。

因为 ADC 的 DVDD 输入和时钟源或时钟缓冲器可能共享同一个数字电源,所以检查这些引脚是否有大的瞬变。瞬态由电流的突然需求引起,可能需要额外的去耦电容器来抑制。但是在选择去耦电容器的尺寸时要小心:较小的去耦电容器具有较小的电感并且可以更快地提供必要的电流,而较大的去耦电容器有助于存储大部分必要的电荷并过滤电源轨上的任何噪声。可能需要结合使用两种尺寸的去耦电容器来保持数字电源的安静和稳定。

另一种有助于减少耦合到 ADC 输出的瞬变的技术是在 ADC 数字电源引脚和时钟源或时钟缓冲器电源引脚之间放置一个小铁氧体磁珠。

如果您的 PCB 尺寸不允许将时钟电路放置在远离敏感模拟电路的地方,则可能有助于部分分离接地以隔离时钟电流的返回路径。但是,应始终将接地层的两侧尽可能靠近器件,以避免 ADC 的模拟部分和数字部分之间出现显着的接地电位差。

最终,遵循本文中推荐的做法和程序应该有助于避免最常见的时钟相关问题,并确保您的时钟源不是信号链噪声的最大贡献者。

从基础到高级的ADC讲座,将涵盖高速ADC设计的原理、传统架构和最先进的设计。第一部分首先回顾了ADC的基本知识,包括采样、开关电容和量化理论。接下来,介绍了经典ADC架构的基础和设计实例,如闪存、SAR和流水线ADC。然后,本教程将对混合型ADC架构进行总体概述,这就结束了第一部分。在第二部分,首先描述了ADC的度量。然后,介绍混合或非混合架构的各种先进设计。该教程最后将以数字辅助解决技术结束。

>>>点击图片了解课程详情!

今天小编带来了:ISSCC2023套餐,里面有文章、PPT、Tutorial等,同学可以拿回去自己学习研究。

1、深入理解SerDes(Serializer-Deserializer)之一

2、深入理解SerDes(Serializer-Deserializer)之二

3、科普:深入理解SerDes(Serializer-Deserializer)之三

4、资深工程师的ESD设计经验分享

5、干货分享,ESD防护方法及设计要点!

6、科普来了,一篇看懂ESD(静电保护)原理和设计!

7、锁相环(PLL)基本原理 及常见构建模块

8、当锁相环无法锁定时,该怎么处理的呢?

9、高性能FPGA中的高速SERDES接口

10、什么是毫米波技术?它与其他低频技术相比有何特点?

11、如何根据数据表规格算出锁相环(PLL)中的相位噪声

12、了解模数转换器(ADC):解密分辨率和采样率

13、究竟什么是锁相环(PLL)

14、如何模拟一个锁相环

15、了解锁相环(PLL)瞬态响应

16、如何优化锁相环(PLL)的瞬态响应

17、如何设计和仿真一个优化的锁相环

18、锁相环(PLL) 倍频:瞬态响应和频率合成

19、了解SAR ADC

20、了解 Delta-Sigma ADC

21、什么是数字 IC 设计?

22、什么是模拟 IC 设计?

23、什么是射频集成电路设计?

24、学习射频设计:选择合适的射频收发器 IC

25、连续时间 Sigma-Delta ADC:“无混叠”ADC

26、了解电压基准 IC 的噪声性能

27、数字还是模拟?I和Q的合并和分离应该怎么做?

28、良好通信链路性能的要求:IQ 调制和解调

29、如何为系统仿真建模数据转换器?

30、干货!CMOS射频集成电路设计经典讲义(Prof. Thomas Lee)

31、使用有效位数 (ENOB) 对 ADC 进行建模

32、以太网供电 (PoE) 的保护建议

33、保护高速接口的设计技巧

34、保护低速接口和电源电路设计技巧

35、使用互调多项式和有效位数对 ADC 进行建模

36、向 ADC 模型和 DAC 建模添加低通滤波器

37、揭秘芯片的内部设计原理和结构

38、Delta-Sigma ADCs中的噪声简介(一)

39、Delta-Sigma ADCs中的噪声简介(二)

40、Delta-Sigma ADCs 中的噪声简介(三)

41、了解Delta-Sigma ADCs 中的有效噪声带宽(一)

42、了解Delta-Sigma ADCs 中的有效噪声带宽(二)

43、放大器噪声对 Delta-Sigma ADCs 的影响(一)

44、放大器噪声对 Delta-Sigma ADCs 的影响(二)

45、参考电压噪声如何影响 Delta Sigma ADCs

46、如何在高分辨率Delta-Sigma ADCs电路中降低参考噪声

47、时钟信号如何影响精密ADC

48、了解电源噪声如何影响 Delta-Sigma ADCs

49、运算放大器简介和特性

50、使用 Delta-Sigma ADCs 降低电源噪声的影响

51、如何设计带有运算放大器的精密电流泵

52、锁定放大器的基本原理

53、了解锁定放大器的类型和相关的噪声源

54、用于降低差分 ADC 驱动器谐波失真的 PCB 布局技术

55、干货!《实用的RFIC技术》课程讲义

56、如何在您的下一个 PCB 设计中消除反射噪声

57、硅谷“八叛徒”与仙童半导体(Fairchild)的故事!

58、帮助你了解 SerDes!

1、免费公开课:ISCAS 2015 :The Future of Radios_ Behzad Razavi

2、免费公开课:从 5 微米到 5 纳米的模拟 CMOS(Willy Sansen)

3、免费公开课:变革性射频毫米波电路(Harish Krishnaswamy)

4、免费公开课:ESSCIRC2019-讲座-Low-Power SAR ADCs

5、免费公开课:ESSCIRC2019-讲座-超低功耗接收器(Ultra-Low-Power Receivers)

6、免费公开课:CICC2019-基于 ADC 的有线收发器(Yohan Frans Xilinx)

7、免费公开课:ESSCIRC 2019-有线与数据转换器应用中的抖动

8、免费公开课:ISSCC2021 -锁相环简介-Behzad Razavi

9、免费公开课:ISSCC2020-DC-DC 转换器的模拟构建块

10、免费公开课:ISSCC2020-小数N分频数字锁相环设计

11、免费公开课:ISSCC2020-无线收发器电路和架构的基础知识(从 2G 到 5G)

12、免费公开课:ISSCC2020-从原理到应用的集成变压器基础

13、免费公开课:ISSCC2021-射频和毫米波功率放大器设计的基础

14、免费公开课:ISSCC 2022-高速/高性能数据转换器系列1(Prof. Boris Murmann)

15、免费公开课:ISSCC 2022-高速/高性能数据转换器系列2(Dr. Gabriele Manganaro)

16、免费公开课:ISSCC 2022-高速/高性能数据转换器系列3(Prof. Pieter Harpe)

17、免费公开课:ISSCC 2022-高速/高性能数据转换器系列4(Prof. Nan Sun)

点击下方“公众号”,关注更多精彩

半导体人才招聘服务平台