FPGA在数据时代有什么终极意义?从特性上来讲,相比内核执行外算法都冻结的ASIC,可编程内核的FPGA拥有很强的灵活性和适应性;从功用上来讲,是摩尔定律放缓后至关重要的协处理器和桥接器件。

在异构计算的大背景下,FPGA愈发追求小尺寸、低功耗和高性能,这看准的便是FPGA固有的特性,可以说FPGA是数据时代现阶段最适合的产品。在追求极致性能上,除了增加I/O数量,甚至部分厂商为了追求灵活性和适应性把ASIC塞进了FPGA。

Lattice(莱迪思半导体)是利用28nm FD-SOI(耗尽型绝缘层上硅)这种工艺平衡FPGA的性能和功耗,让小型FPGA兼具“高性能”也具有“低功耗”两种特性。从技术上来讲,主要是因为FD-SOI可在衬底这部分进行电压控制,因此反馈偏压(Back Bias)是可控的,在此方面可自由进行低功耗和高性能的设定切换。

另一方面,传统使用SRAM制程的FPGA产品容易受到辐射干扰,而28nm FD-SOI则拥有较薄的氧化层,因此关键区域的减少,使得软错误率(SEU)随之而降。同时,与bulk CMOS工艺相比,28nm FD-SOI的漏电也降低了50%。

利用这种28nm FD-SOI的工艺,Lattice在去年专门发布了Lattice Nexus™这一技术平台进行多系列产品产出,与此同时还发布了首款产品CrossLink-NX。之前,21ic中国电子网曾经也重点对这种工艺的FPGA进行了讲解。

而就在第一款产品问世六个月后,日前Lattice宣布发布了这款平台的第二代产品——Certus™-NX,这款新产品拥有同类型产品脱颖而出的参数和性能,具有更高的I/O密度和功耗,21ic中国电子网记者受邀参加此次发布会。

当然,需要注意的是Lattice一直专注领域属于中端市场,主营范围还是低功耗的小型FPGA,产品主要聚焦在功能性和性价比上,本款产品亦是如此。

01

更极致的性能和安全性

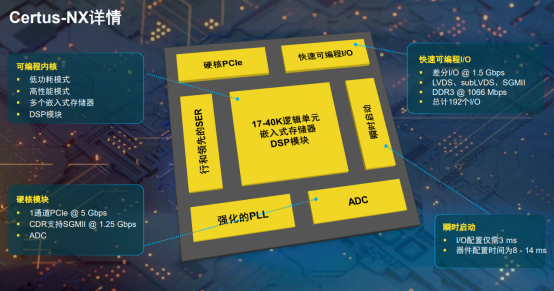

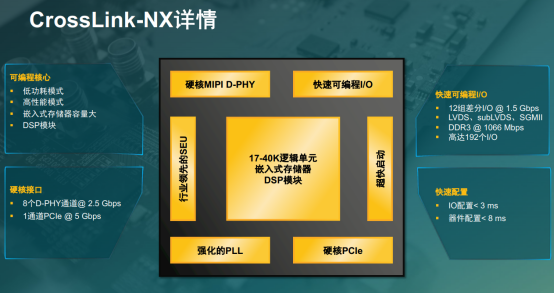

从整体架构来看,Certus-NX与CrossLink-NX因为都采用的是28nm FD-SOI工艺,所以在特性上非常相似,均可切换低功耗和高性能模式,内嵌嵌入式闪存,配置了特有的DSP模块进行乘加法。

另外,在逻辑单元上也均为17-40K。在快速启动方面,两者均采用Lattice一贯的内嵌闪存,大大降低唤醒时间,达到无缝的视觉体验。

图1:Certus-NX详情

图2:CrossLink-NX详情

而从差异性来看,两款产品拥有两个关键的区分点:

一、Certus-NX去除了硬核MIPI D-PHY

根据莱迪思现场技术支持总监蒲小双(Jeffery Pu)的介绍,这主要是考虑到细分子市场对I/O个数的要求而进行的优化,去掉硬核MIPI D-PHY后每平方毫米的I/O个数有了显著地提升。

记者对两款产品的参数上进行了对比,两款产品最小尺寸均为6 x 6 mm(121 csfBGA),CrossLink-NX的I/O数量为72个,而Certus-NX的I/O数量为82个,相当于每平方毫米I/O数量提升了13%。

从应用上来讲, MIPI接口大多数与摄像头和传感器有关,前一代市场瞄准的是消费级市场嵌入式视觉方面,而本产品则更多发力于网络边缘应用添加处理和互连功能,这些应用一般来说强调使用PCle和千兆以太网。正因如此,这一代产品走的便是极致性价比和极致功耗性能,针对不同应用市场将硬核转化为性能。

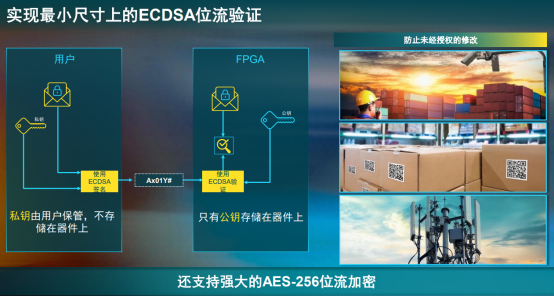

二、Certus-NX增添了安全认证ECDSA位流验证

Jeffery Pu告诉记者,受到前几代产品的启发,包括Lattice以前推出的XO3D产品,内部拥有PFR功能,里面有很复杂的认证,借用这些概念放到新款产品里,这是相对于前一代产品非常明显的差距。

从技术上来讲,ECDSA英文全称Elliptic Curve Digital Signature Algorithm,主要原理是创建数据数字签名,与AES(高级加密标准)不同,ECDSA不会对数据进行加密或阻止数据访问。当然,这款FPGA另外还是支持强大的AES-256位流加密的。

图3:Certus-NX实现最小尺寸上的ECDSA位流验证

从市场上来看,需要在嵌入式视觉方面发力的用户选择带有MIPI接口的CrossLink-NX即可,需要重点在工业、通信上添加处理和互连的则可选用性能更强劲的Certus-NX。

02

性能碾压同类竞品

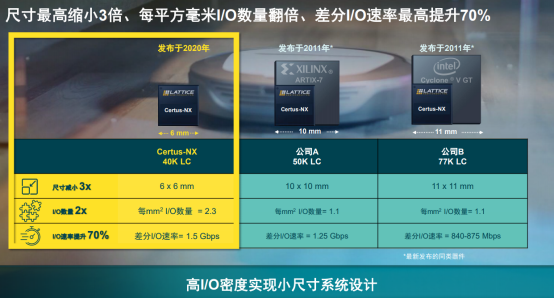

在28nm FD-SOI工艺加持之下,以及Lattice一贯的低功耗FPGA经验,新产品在同类竞品中脱颖而出。需要注意的是,Lattice之前也多次强调自身专注的是消费级的低功耗FPGA,市场既需要追求尖端市场产品的厂商,也需要专注小尺寸产品的FPGA厂商。具体对比如下:

一、3倍的小尺寸,2倍I/O数量,70%I/O速率提升

Certus-NX在最小尺寸上,仅有6 x 6 mm,在I/O数量和速率上最接近的公司A的50K逻辑单元产品都已达到了10 x 10 mm尺寸了,而公司B的77K逻辑单元产品则达到了11 x 11 mm,相差了3倍之多。

而从I/O数量上来说,一方面,有着28 nm FD-SOI工艺加持,另一方面,毕竟这一代产品砍掉了MIPI硬核,数量提升是相当的明显的。当然相比传统工艺产品,28 nm FD-SOI工艺加持之下速率也提升了70%。

图4:对比同类竞品Certus-NX有明显优势

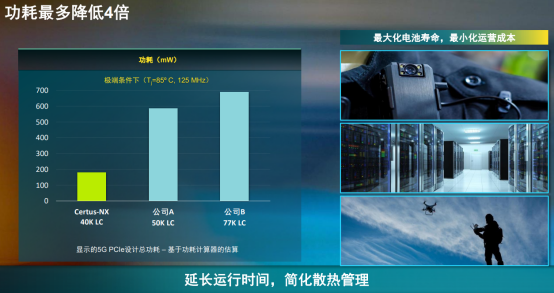

二、4倍功耗降低

Lattice一直以来的优势便是低功耗,从参数上来看,在极端条件下对比公司B的77K逻辑单元产品最多降低了4倍。

从另一方面来看,低功耗就意味着更低的发热,在此方面电池就拥有最大化的寿命。这意味着,用电成本、散热成本、电池更换成本均有所降低。

图5:Certus-NX功耗降低4倍

三、12倍配置速度

配置速度是Lattice一直的强项,从CrossLink-Plus便开始加入这项功能。主要原理上是在产品中内嵌嵌入式闪存,加快了启动的速度。本代产品依然沿袭了前一代产品的3ms的I/O配置时间。

Jeffery Pu为记者介绍表示,传统FPGA一般加入的是SPI Flash,启动速度就取决于SPI的速度。早年传统FPGA能跑到50Mbps速率就很不错了,现如今新的SPI Flash基本可以达到130Mbps,但仍然不是能够达到秒开的效果。

Certus-NX主要使用的是QSPI,相比单通道的SPI,四个通道数据加载速度就会有明显的提升。不过,需要注意的是这需要FPGA具有相应的设计,才能支持快速配置。

很多情况下,在安全为首的系统中,启动时间有延迟会带来一定风险,无缝的启动显示既带来了更好的用户体验,也为安全增添了一分色彩。

图6:Certus-NX拥有12倍的配置速度

四、100倍降低软错误率(SER)

从Certus-NX公布的数据来看,40K逻辑单元下SER达到了19.34,相比公司A的50K逻辑单元产品降低了超过100倍。这归功于28nm FD-SOI这种工艺带来的普惠,因为这种工艺拥有一层较薄的氧化层,因而减少了关键区域,从而降低了软错误率(SER)。

当然,不仅仅是软错误率这一指标,这种工艺还具有抗干扰性,在漏电上也降低了50%。

图7:Certus-NX软错误率降低了100倍

03

低功耗FPGA仍有许多值得期待

除了最新的FPGA,Lattice也在上半年发布了名为Lattice Propel的最新软件方案。据了解,Lattice Propel开发工具包含两大特色:IP整合工具Lattice Propel Builder,以及软件开发工具Lattice Propel SDK。

图8:Lattice的产品更新路线

Propel意为驱动、推进,这两个开发工具也切实地进一步推动了FPGA开发自动化。Lattice Propel Builder可让FPGA开发商以拖动IP区块形式进行设计,还能够自动联机产生代码;Lattice Propel SDK则具备软件套件建构、编译、分析和除错的应用程序,并以软件函式库与开发板级提供支持,让软件开发人员能在硬件就绪前进行软件设计,加速产品上市时程。

值得一提的是Lattice Propel是支持RISC-V IP的,众所周知RISC-V在嵌入式应用是极其重要的,透过最新FPGA开发环境,行业将迎来新的开发格局。

当然,基于Certus-NX这款产品的相关工具和IP也已提供下载使用,开发者将拥有更好的开发体验。目前,Certus-NX的样片已发往多个客户,开发板已可订购。

图9:各类工具和解决方案加速开发

在发布会的最后,Jeffery Pu透露,28nm FD-SOI的Nexus技术平台的第三代产品将在今年下半年宣发,相关计划也非常多,低功耗FPGA市场下半年将有更多惊喜值得期待。

【1】管理层与董事会“开撕”?Arm中国CEO吴雄昂罢免之谜

【2】振奋人心!我国首台核心元器件100%国产化的计算机诞生了

【3】终于整理齐了,电子工程师“设计锦囊”,你值得拥有!

【4】半导体行业的人都在关注这几个公众号