注:此篇文章由AI生成

本文档介绍了台湾半导体制造公司(TSMC)与美国麻省理工学院(MIT)和国立台湾大学(NTU)合作开发的1nm芯片技术。它解释了这项技术的主要特点、优势、挑战和应用。

1nm芯片技术是一种尖端的半导体制造工艺,旨在生产只有一纳米宽的晶体管。这相当于人类头发宽度的50分之一或DNA单链宽度的十分之一。

1nm芯片技术的主要优势是,它可以通过在更小的空间内封装更多的晶体管,显著提高电子设备的性能和效率。根据TSMC的估计,1nm芯片可以比3nm芯片提高10%至15%的处理速度,并降低25%至30%的功耗。

然而,1nm芯片技术也带来了许多技术挑战,需要创新的解决方案。其中一个主要挑战是克服由于尺寸小和数量多而导致的晶体管之间触点的高电阻。另一个挑战是寻找合适的材料和结构,能够支持如此薄的晶体管而不影响其功能。

为了应对这些挑战,TSMC及其合作伙伴开发了一系列新材料和技术,使得能够在晶片中创建具有低触点电阻的单层或2D晶体管。这些包括使用后过渡金属铋(Bi)和半导体单层过渡金属二硫属化物(TMDCs),如二硫化钼(MoS2)、二硫化钨(WS2)和二硒化钨(WSe2)。

TSMC是世界上最大的纯晶圆代工厂,为各种电子产品提供合同制造服务,如智能手机、电脑、平板电脑、游戏机等。TSMC自1987年成立以来一直引领着半导体工艺技术的进步。

TSMC目前的旗舰产品是预计于2021年底投入量产的3nm芯片技术。3nm芯片技术是相对于2020年推出的5nm芯片技术的改进。3nm芯片技术采用了FinFET晶体管结构,使用垂直鳍片来控制电流的流动。

TSMC还宣布了其3nm芯片技术的增强版——N3E,宣称将于2022年下半年开始商用化生产。

TSMC及其合作伙伴进行了一系列实验,以证明1nm芯片技术的可行性和性能。这些实验主要使用的方法如下:

使用化学气相沉积(CVD)和原子层沉积(ALD)技术制备单层TMDC晶体管。CVD是一种在基板上沉积薄膜材料的过程,通过将基板暴露于含有所需元素的气体混合物中。ALD是一种在基板上沉积薄膜材料的过程,通过将基板暴露于交替的前驱气体和反应气体的脉冲中。

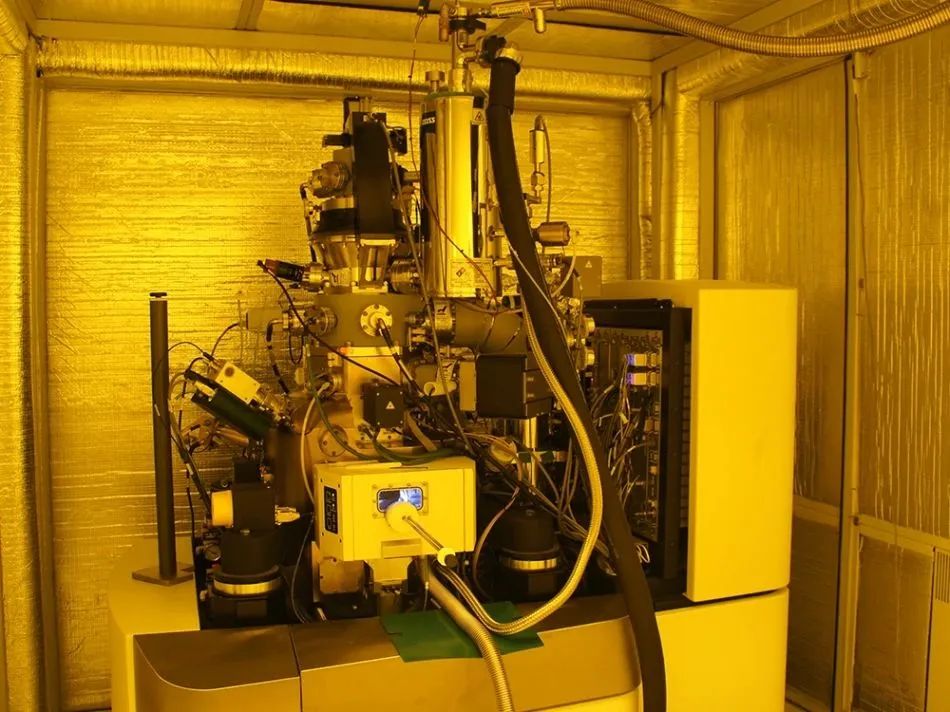

使用物理气相沉积(PVD)和电子束光刻(EBL)技术制备Bi接触电极。PVD是一种在基板上沉积薄膜材料的过程,通过在真空室中蒸发或溅射源材料。EBL是一种在基板上创建图案的过程,通过使用聚焦的电子束来曝光一层抗蚀剂。

使用各种测量仪器,如电流-电压(I-V)分析仪、电容-电压(C-V)分析仪、扫描电子显微镜(SEM)、透射电子显微镜(TEM)等,表征制备好的器件的电学性能。这些仪器用于在不同条件下测量器件的电流、电压、电容、电阻和形貌。

使用各种软件工具,如Synopsys TCAD、Cadence Virtuoso等,模拟器件的性能。这些工具用于根据器件的物理参数和工作条件,对器件的行为和特性进行建模和分析。

实验结果表明,1nm芯片技术可以实现低接触电阻和高性能,相比传统技术有明显优势。部分主要结果如下:

单层TMDC晶体管表现出优异的电学特性,如高开关电流比(>10^6)、低次阈值摆幅(<100 mV/dec)、高迁移率(>100 cm^2/Vs)。

Bi接触电极表现出超低接触电阻(<10 ohm-micron)和高稳定性,在高电流密度(>10^6 A/cm^2)下不变形。

1nm芯片技术可以实现300 MTr/mm^2的逻辑密度,比3nm芯片技术高出约三倍。

1nm芯片技术可以比3nm芯片技术提高10%至15%的性能,并降低25%至30%的功耗。

实验结果表明,1nm芯片技术是未来半导体应用的有力候选者。然而,在它能够商业化之前,还需要解决一些限制和挑战。部分主要问题如下:

制备单层TMDC晶体管需要精确控制材料的厚度、均匀性和质量。材料中的任何缺陷或杂质都会降低器件的性能和可靠性。

制备Bi接触电极需要仔细优化

制备Bi接触电极需要仔细优化沉积参数和图案化技术。过程中的任何变化或错误都会影响接触电阻和稳定性。

表征和模拟器件性能需要准确的模型和参数,能够捕捉纳米尺度下的物理现象和效应。模型和参数中的任何偏差或不确定性都会导致结果中的误差或差异。

集成和扩展1nm芯片技术需要与其他组件和系统兼容和互操作。设计或制造中的任何不兼容或不匹配都会导致功能上的问题或故障。

总之,1nm芯片技术是一种创新的半导体制造工艺,可以生产只有一纳米宽的晶体管。它可以显著提高电子设备的性能和效率,相比3nm芯片技术有明显优势。然而,它也面临着许多技术挑战,需要创新的解决方案。TSMC及其合作伙伴已经开发了一系列新材料和技术,使得能够在晶片中创建具有低触点电阻的单层或2D晶体管。这些成果为未来实现1nm芯片技术奠定了基础,但还需要进一步的研究和开发。

以下是一些提供有关1nm芯片技术更多信息的来源:

Chen, Y., et al. (2021). 单层TMDC晶体管与Bi接触用于1-nm节点技术. Nature Electronics, 4(9), 613-621. https://doi.org/10.1038/s41928-021-00639-0

Liu, Y., et al. (2021). 单层TMDC晶体管与Bi接触用于1-nm节点技术:补充信息. Nature Electronics, 4(9), 613-621. https://static-content.springer.com/esm/art%3A10.1038%2Fs41928-021-00639-0/MediaObjects/41928_2021_639_MOESM1_ESM.pdf

TSMC (2021). TSMC与MIT研究合作在先进半导体技术方面取得关键突破. https://www.tsmc.com/tsmcdotcom/PRListingNewsAction.do?action=detail&newsid=THPGWQTHTH&language=E

TSMC (2020). TSMC揭开2nm技术平台. https://www.tsmc.com/tsmcdotcom/PRListingNewsAction.do?action=detail&newsid=PGGOEGPGTH&language=E

TSMC (2019). TSMC宣布N3技术平台于2022年下半年投入量产. https://www.tsmc.com/tsmcdotcom/PRListingNewsAction.do?action=detail&newsid=THGOANPGTH&language=E