之前我们开始讲到通过RTL改善时序的几个技巧,提到了移位操作两种方式的切换。我们将继续探讨通过RTL改善时序的其他几个方法。今天我们来看看设计中用到了Block RAM的时候,如何处理时序收敛的问题。

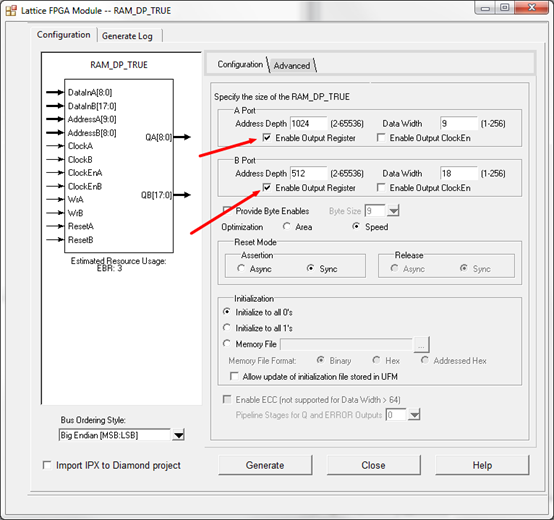

在使用Block RAM的时候,打开Block RAM的输出寄存器选项。

Block RAM是我们在设计中经常要用到的资源。不同于LUT部分,Block RAM主要实现了数据存储的功能,比如做双口的RAM,FIFO等。在通过EDA软件例化一个Block RAM的时候,输入的寄存器一定是使能的,输出寄存器做为选项,可以使能,也可以关闭。如果没有打开Block RAM的输出寄存器,这一级逻辑的延时就有几个ns。如果你的时序不满足,在时序报告中发现在关键路径上有Block RAM,而且这个Block RAM的输出寄存器没有使能,可以打开这个选项,对时序的提高会有很大的帮助。毕竟2-3个ns的延时对时序的提高是非常明显的。

不过需要注意的是,因为打开了Block RAM的输出寄存器,那么寄存器的输出就比之前的晚了一拍。在时序设计上,一定要根据这个变化调整你的流水设计,否则会影响你的功能。