寄存器的clock enable

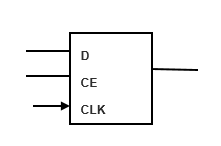

一个标准的寄存器,除了数据输入,数据输出,时钟,复位,还有一个clock enable信号。Clock enable作为一个使能信号,当条件满足时才会触发对寄存器的操作。这也是我们在做RTL设计的时候常常会用到的信号。

由于clock enable信号是作用在时钟上的,在实现结构上clock enable需要更长的setup时间。如果分析时序报告我们发现关键路径出现在clock enable上,可以在这方面做出改进。

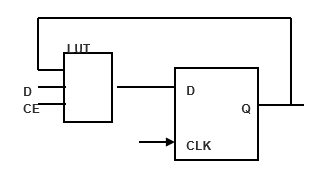

通过上图我们可以看到,我们可以用一个等效的电路完全替代clock enable信号的。经过这样的修改,逻辑的功能没有发生变化,但我们不再需要保证给clock enable预留额外的setup时间了。

综合工具的发展可以完全把上述的过程变成自动化的,RTL设计的时候不需要你为此做任何改动。只要在定义寄存器的时候,添加如下的约束,综合工具就会自动做这样的等效变换。

reg [1:0] q /* synthesis syn_useenables = 0 */;