我们在分析时序的时候经常会提到Setup up time和Hold time。时序报告一般也会分Setup的报告和Hold的报告。

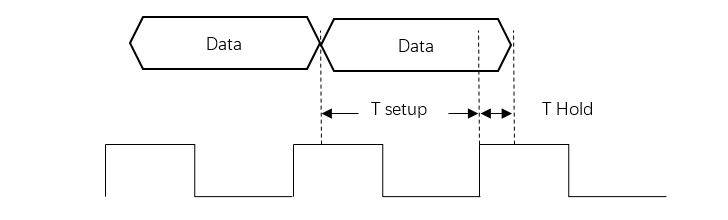

在同步设计中,我们要在时钟的变化沿(上升沿或下降沿,为了便于描述,后面我们统一称为上升沿)对信号寄存器采样。为了保证信号正确的存储,必须要在时钟的上升沿到来之前数据的稳定,这个时间我们称为setup time,信号的建立时间。由于寄存器的物理特性,数据在有效后必须要稳定一段时间才能完成这个存储过程,这个稳定的时间我们称为Hold time,信号的保持时间。

由此可见,数据信号在处理和传输的时间越短,留给时钟上升沿的时间越充足,时钟频率也就可以运行的更快。数据信号在处理和传输中的时间越长,留给Hold的时间越充足。这两个矛盾的指标,确定了设计的频率。一个健壮的设计,必须要同时满足Setup和Hold的要求才能保证可靠性。我们在分析时序报告的时候也要两方面同时分析。

Setup的时间越短越好,最长路径的Setup就决定了设计能跑的最高频率。我们在做STA的时候,分析和处理最多的就是Setup的delay。

Hold的时间越长越好,最短路径的Hold time就是我们能容忍的上限。Hold time的问题相对比较好处理,一般EDA软件可以通过绕线的方式对最快路径进行修复。