前三章给一些没有学过半导体的人掌握的基础知识,核心观点就是MOS模型怎么去理解,用我导师的话就是Vgs对Ids的控制,这里我们称它叫Gm,那么问题来了,不同工作区的Vgs对Ids的控制是什么样的呢?截止区不谈,亚阈值区是指数关系所以Vgs对Ids的控制很强,通常把他当做Bjt用或者说对Gm有较大要求的时候使用,缺点嘛,就是临界导通,pvt下难以保证,饱和区就是二次关系了,最常说的就是Vgs对Ids的强控制,这里的强是相对于线性区一次关系而言的,这也是常用饱和区MOS管的原因,比如电流镜,比如运放,因为它受到Vds影响较小(沟长调制影响较小),我们保证两个MOS管的Vgs相等的时候,差不多流过的电流就相等了,那么线性区的MOS管通常用在哪儿呢?答案是当做开关管或者线性电阻用,因为Vgs和Ids的关系是一次关系,所以斜率是几乎固定的,拿它当线性电阻或者开关管用最合适不过了。

了解到MOS管特性后,后面应该掌握的是放大器,所以后面开始讲几种类型的放大器。(模拟不谈放大谈啥?)等你开始对增益有一定的理解后,后面会跟你讲频率响应,这个的目的是为了后面零极点或者说系统稳定性服务的。

再后面讲噪声,这个应该没啥,我们导师对于本科生都是不上的,自学,懂得怎么计算就行了。

再后面是运算放大器,掌握一下两级运放的零极点分布,弥勒补偿是如何进行极点分裂,引入的右边零点是如何引入的?调零电阻是如何改变零点极性的?推导一下就明白了。

再后面章节是稳定性或者说带隙基准了,稳定性就是为了让你有个反馈的概念在脑海里面,如何稳定?肯定是系统负反馈大于正反馈,如何衡量欲度?引入相位欲度概念。这个概念主要是为了让你明白零极点对于系统幅频和相频特性的影响。可以结合信号与系统来看看这个,核心观点就是让你明白对于系统零极点分布,如何设计补偿来实现系统稳定性。对了需要记住一点,一般系统的单位增益带宽GBW和相位裕度PM之间是trade off的关系!

带隙基准而言,就是讲一下正负温度系数电压如何实现的,很简单,需要掌握的还是系统稳定性问题,了解一下,运放正负端能否互换,为什么?为什么说负反馈环的系数比正反馈环大?结合前面稳定性分析一下,这是最简单的二级系统(除了二级运放以外)

再后面学习非线性或者开关电容的章节了,非线性比较麻烦,需要考虑的很多,细节只有用到才去看,不深入谈,开关电容引入的目的是为采样保持服务的,就是对于电容这块的理解,核心观点就是,开关前后,电容上电荷守恒。

再往后面就是时钟电路了,VCO或者PLL,这块就偏向于应用了,只有做这个的时候采用它,基础可以忽略。其实PLL就是频率=0处有两个极点,需要设计零点,带宽和极点的位置,保证PLL相位裕度OK,随着输入频率低了,带宽会做低,零点难以实现。你问为啥带宽会变低?那就是涉及到LPF对CP输出离散电流零阶保持成一个Vctrl电压的过程了,为了能够线性化处理这个过程。

再继续往后面走就没啥了吧,一些版图知识了,还有一些器件知识了。

人在高铁上信号不好,暂时想那么多了,汇总一下拉扎维其实就是这么点东西,需要多看多理解,而不是单纯做题。

--------------------------------分割线--------------------------------

没想到随手一写的回答,点赞过百了,有人跟我说,拉扎维没有我说的那么简单,是的肯定是的,但是我第一次学的时候,我导师也是关着书给我讲每一章节告诉我们什么内容的,让你知道为啥学这个,增强你对模拟电路的认识,然后归纳出一套自己的理解,就是那种随口就说出来的那种。

既然大家挺喜欢这个回答的,我再补充几点吧,前面两章,你只需要记住一个观点就行了,Vgs对Ids的控制,就是MOS管的特性,然后还有什么沟长调制效应,衬底偏置效应,前者指的是vds也会对Ids有个控制,后者指的是衬底电位影响阈值电压,核心思想就是影响vgs对ids的控制,有了这个思想,mos管的使用无非就是那个控制强一些,那个控制弱一些,然后利用强弱特性,保证让它用于什么样的电路中。

第三章是单级运放,讲得核心就是三种类型运放,共源,共栅,源跟随,共源是G端输入,D端输出,增益是-gm*ro,极性变负了。这是最常用的,共栅是S端输入,D端输出,增益是gm*ro,源跟随就是G端输入,S端输出了,都叫跟随了,没啥增益,增益可以看做=1,其实也就是约等于gm*1/gm,有啥用?输出阻抗低,可以输出大电流,较大的驱动能力。

第四章电流镜,针对MOS饱和区里面Vgs对Ids强控制原理展开的应用。

第五章是差分运放,讲一下差分信号,引入共模和差模概念。

第六章频率响应,前面提到过不讲了,补充一点就是弥勒效应这个很关键,需要自己理解一下,有利于后面对系统补偿的理解。

第七章噪声,让你明白每个模块对于系统的噪声贡献,先要明白模块的输出到系统输出之间的传递函数H(s),然后会分析这个模块自身的频谱密度,我们称它为S(f),结合计算它对系统噪声贡献就是P(f)=S(f)*|H(s)|^2,记住那个Hs是求模,此外,需要对P(f)频率有个积分,如果考虑全频带,就是0到正无穷,一般都是单频带。

然后需要了解到的一些噪声类型,电阻的热噪声,电压形式是4kTR,电流形式是4kT/R,MOS管噪声,4kTgm,还有是理解一些相关性和非相关的噪声,这样方便你计算系统噪声时候,怎么针对每个模块进行噪声叠加。

第八章讲反馈,我是没太记住和区分课本里面的反馈类型,当然考试肯定要求会的,如何区分电流反馈还是电压反馈,其实主要是采样和叠加,细节电路理论应该有讲过,实际使用不多,我就不讲了,主要是我也没理清楚,但是掌握住采样与叠加的思想,这个就容易区分了。

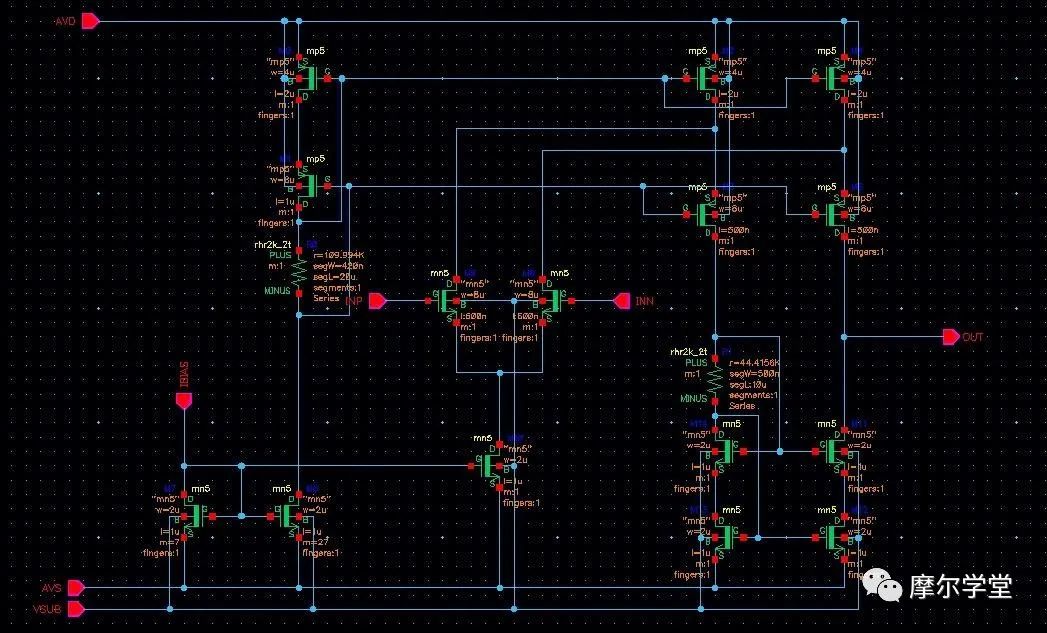

第九章讲运算放大器,设计运放的时候,不要被课本迷惑住了,第4章学习了电流镜,他是为运放做偏置来服务的,千万别拿个电压源去给运放的MOS管栅端做偏置,这就是瞎胡闹。建议的是,先确定好运放的架构,再大致分配一下电压裕度,设计合适的偏置电路,再调整运放,可以先设计好偏置电路,再做运放,因为偏置电路是用来纯消耗的。了解一下,几种运放结构,单级5管运放,7管二级运放,cascode运放,套筒和折叠,他们四个的优缺点太明显了,不说了。需要思考的问题是,运放选择PMOS作为输入对管和NMOS作为输入对管的优缺点,以及在输入的时候采用PMOS电流镜负载和NMOS电流镜负载的区别,这个在设计Vbg的时候能够用到。

第十章讲的是稳定性,主要是对二级运放的补偿,上面提到过,不仔细讲了。结合弥勒等效,以及核心思想都是GBW与PM之间的trade off!

第11章讲bandgap了,了解一下什么是bandgap,正负温度系数的产生,核心思想就是,架构的选取和运放的设计,一般都是banba架构或者Ahuje架构,名字可能打的有问题,就是在Vbg的输出上做处理,运放的设计需要考虑输入对管以及负载管类型的选取,还会涉及到Bandgap的系统补偿的设计。这个做Vbg的人面试肯定会问的问题就是,vbg电压的表达式,影响vbg电压的因素有那些,如何消除?偶尔会考一些负反馈的内容在里面,比如极点怎么分布的?然后运放如果正负反接行不行?为啥不行?怎么判断负反馈大于正反馈?多思考思考!对了,第一版课本里那个与电源无关的偏置电路,拿PMOS管实现的,那张图画错了,第二版改过来了,大家可以翻开对比一下,我读书那会儿第二版没出来,我还跟老师讨论过这个问题。

第12章开关电容,前面也提到了一些,核心思想就是开关前后电容极板电荷守恒。后面做采样保持电路的时候会有这个思想在里面,如果用它的话,单纯看拉扎维是不够的,拉扎维里面你需要掌握的是开关电容电路的噪声,以及引入的时钟馈通和电荷共享的原因,还有就是失配消除,其实就是把运放的失配存到输入电容或者输出电容,电容在输入的话,输入的失配不能够完全消除,只能保证它不被放大直接到输出,电容在输出端的话,输入失配可以完全被消除掉,但是会存在运放饱和的风险,结论是这样了,细节还是得自己看了。

第13章非线性和失配,两个可不是一个东西,非线性指的是线性度不太好的意思,举个例子,如果输入信号影响到系统的属性,比如说增益和带宽,那么说明系统具有较大的非线性,影响越明显,非线性越大,拿mos管举例,共源运放,gm受到输入信号有影响吧?gm=根号下2uncox(Vgs-Vth)Ids嘛,很明显受到Vgs的影响,如果你换成二极管负载的共源级放大器的话,他的gm表达式成为什么样子的呢?推导一下就可以看明白这两个电路的线性度了,当然线性度提升了会有其他方面的下降,思考一下你们会明白的。失配的概念,就是误差,这个不是非线性,很输入信号关系不大,需要掌握的失配消除放大,前面我提到过,自己消化一下。

第14章振荡器,需要结合前面的震荡原理来分析,什么巴赫豪森判据,说白了就是反馈回来的信号,相位翻转成为正的了,系统还有增益,就会震荡啦。我是嘴巴上说说,细节还是得自己去看看,掌握一下ring架构和lc架构vco是啥样子的,都是对电容充放电,lc带个电感而已。如果做PLL会对这个有更深入的理解,比如VCO的相位噪声的贡献,这里就不谈了。

第15章PLL,前面也提到过PLL系统,这里不仔细讲了。我本身也是做过PLL的,有对这个感兴趣的可以私信跟我讨论讨论,这里提出几个问题,比如说零极点的分布,Kvco的设计,每个模块相噪的贡献,相位噪声和jitter之间的转化,jitter的种类,如何定义。如何通过优化相噪来优化jitter?面试应届生的时候我一般会问这些问题的。

第16章是短沟道器件和模型了,一般先进工艺会考虑到短沟道器件,还有一些非理想的效应,模型的话,通常比较多的是BSIM,BSIM4和BSIM6模型还是有一定区别的,设计MOS管尺寸的时候考虑Gm/Id设计最合适了。

第17章涉及的是工艺,18章涉及的是版图,工艺看拉扎维是没啥卵用的,大致了解一下怎么制作的,CMOS工艺比较便宜,版图的话我也不太了解,研究生的时候没画过版图,作为一名合格的模拟ic设计工程师,你需要做到的是把控好电路的敏感模块和敏感线,让版图小哥帮你处理一下就行啦,比如说敏感线上加隔离,敏感模块做到NBL里面,然后设计过程中,那些MOS换需要匹配,还有电容电阻的匹配方式,这个是你需要了解的,画的话还是让专业版图工程师来吧,记住一点,就是,如果你说整个模块,比如说运放,都需要匹配,那么就等于都不匹配,因为资源就那么多,都要几乎=都没有,也就是你没有做到对资源的合理利用。

好啦,暂时这么多了,如果大家关注度多的话,可以考虑再更新一下其他知识点,感兴趣的小伙伴可以跟我讨论呀!以上是我个人(大部分都是听我之前导师讲的)对拉扎维课本的理解。

---------------------------分割线----------------------------------

这周看到大家还挺喜欢这个答案的,有一些小伙伴开始追更啦,基于拉扎维我想再谈几点看法,顺便给大家讲一些关于设计的干货,初学者可以听一听,大佬就忽略吧。

看法: 学会拉扎维不仅仅是说会做题,老实说我确实也是很多题不会做,当然我们华科大也有CMOS考试都是满分的大佬,他确实基础很好,无懈可击的好,但是对于普通人而言,做题不是目的,理解才是关键,否则不可能工作的时候对电路的认识不够,直接开始画小信号?或者拿着电路开始仿真?那样的效率会低很多。好啦,简单的谈一谈运放吧。

针对应用上而言,我们在选取运放架构的时候,拉扎维肯定有教过大家,五管运放、cascode 运放(折叠和套筒)、以及二级运放,他们会在面积,稳定性,噪声,电压裕度上面有各自的优缺点,课本里面有讲,这里就不谈了,那么我想问一下,我们设计单端输出运放的时候,输入对管的选取是怎么考虑的?然后双端转单端输入的时候,负载管选择pmos电流镜(上端网络转单端)还是nmos电流镜(下端网络转单端)负载呢?

输入对管的选择大家一定不会陌生,因为它跟运放的输入共模电平有关,低共模电平我们选择pmos作为输入对管,高共模电平我们选择nmos作为输入对管,假设有需求的话,pmos和nmos都可以同时做输入对管,那就是轨至轨运放的使用了,总之是根据运放的输入共模电平范围来决定输入对管的选择的,这个很简单,不用质疑。那么转单端输出的负载管应该如何去选择呢?

答案就是根据运放输出的接法相关,如果运放输出接PMOS栅端,那么负载管我们可以选择PMOS电流镜,如果是NMOS栅端,那么我们可以选择用NMOS做电流镜输出,具体原因跟PSR有关,可以推导一下vdd的波动对于输出的影响,常用的比如Bandgap电路或者LDO电路设计理念会考虑到运放架构的选择。

本文转自知乎,作者辉霸,版权归原作者所有,仅供大家学习。

今天小编带来了:ISSCC2023套餐,里面有Short Courses、文章、PPT、Tutorial等,同学可以拿回去自己学习研究。

1、深入理解SerDes(Serializer-Deserializer)之一

2、深入理解SerDes(Serializer-Deserializer)之二

3、科普:深入理解SerDes(Serializer-Deserializer)之三

4、资深工程师的ESD设计经验分享

5、干货分享,ESD防护方法及设计要点!

6、科普来了,一篇看懂ESD(静电保护)原理和设计!

7、锁相环(PLL)基本原理 及常见构建模块

8、当锁相环无法锁定时,该怎么处理的呢?

9、高性能FPGA中的高速SERDES接口

10、什么是毫米波技术?它与其他低频技术相比有何特点?

11、如何根据数据表规格算出锁相环(PLL)中的相位噪声

12、了解模数转换器(ADC):解密分辨率和采样率

13、究竟什么是锁相环(PLL)

14、如何模拟一个锁相环

15、了解锁相环(PLL)瞬态响应

16、如何优化锁相环(PLL)的瞬态响应

17、如何设计和仿真一个优化的锁相环

18、锁相环(PLL) 倍频:瞬态响应和频率合成

19、了解SAR ADC

20、了解 Delta-Sigma ADC

21、什么是数字 IC 设计?

22、什么是模拟 IC 设计?

23、什么是射频集成电路设计?

24、学习射频设计:选择合适的射频收发器 IC

25、连续时间 Sigma-Delta ADC:“无混叠”ADC

26、了解电压基准 IC 的噪声性能

27、数字还是模拟?I和Q的合并和分离应该怎么做?

28、良好通信链路性能的要求:IQ 调制和解调

29、如何为系统仿真建模数据转换器?

30、干货!CMOS射频集成电路设计经典讲义(Prof. Thomas Lee)

31、使用有效位数 (ENOB) 对 ADC 进行建模

32、以太网供电 (PoE) 的保护建议

33、保护高速接口的设计技巧

34、保护低速接口和电源电路设计技巧

35、使用互调多项式和有效位数对 ADC 进行建模

36、向 ADC 模型和 DAC 建模添加低通滤波器

37、揭秘芯片的内部设计原理和结构

38、Delta-Sigma ADCs中的噪声简介(一)

39、Delta-Sigma ADCs中的噪声简介(二)

40、Delta-Sigma ADCs 中的噪声简介(三)

41、了解Delta-Sigma ADCs 中的有效噪声带宽(一)

42、了解Delta-Sigma ADCs 中的有效噪声带宽(二)

43、放大器噪声对 Delta-Sigma ADCs 的影响(一)

44、放大器噪声对 Delta-Sigma ADCs 的影响(二)

45、参考电压噪声如何影响 Delta Sigma ADCs

46、如何在高分辨率Delta-Sigma ADCs电路中降低参考噪声

47、时钟信号如何影响精密ADC

48、了解电源噪声如何影响 Delta-Sigma ADCs

49、运算放大器简介和特性

50、使用 Delta-Sigma ADCs 降低电源噪声的影响

51、如何设计带有运算放大器的精密电流泵

52、锁定放大器的基本原理

53、了解锁定放大器的类型和相关的噪声源

54、用于降低差分 ADC 驱动器谐波失真的 PCB 布局技术

55、干货!《实用的RFIC技术》课程讲义

56、如何在您的下一个 PCB 设计中消除反射噪声

57、硅谷“八叛徒”与仙童半导体(Fairchild)的故事!

58、帮助你了解 SerDes!

59、ISSCC 2022 值得关注的新技术!

60、ISSCC 2023 有什么值得关注的亮点?

1、免费公开课:ISCAS 2015 :The Future of Radios_ Behzad Razavi

2、免费公开课:从 5 微米到 5 纳米的模拟 CMOS(Willy Sansen)

3、免费公开课:变革性射频毫米波电路(Harish Krishnaswamy)

4、免费公开课:ESSCIRC2019-讲座-Low-Power SAR ADCs

5、免费公开课:ESSCIRC2019-讲座-超低功耗接收器(Ultra-Low-Power Receivers)

6、免费公开课:CICC2019-基于 ADC 的有线收发器(Yohan Frans Xilinx)

7、免费公开课:ESSCIRC 2019-有线与数据转换器应用中的抖动

8、免费公开课:ISSCC2021 -锁相环简介-Behzad Razavi

9、免费公开课:ISSCC2020-DC-DC 转换器的模拟构建块

10、免费公开课:ISSCC2020-小数N分频数字锁相环设计

11、免费公开课:ISSCC2020-无线收发器电路和架构的基础知识(从 2G 到 5G)

12、免费公开课:ISSCC2020-从原理到应用的集成变压器基础

13、免费公开课:ISSCC2021-射频和毫米波功率放大器设计的基础

14、免费公开课:ISSCC 2022-高速/高性能数据转换器系列1(Prof. Boris Murmann)

15、免费公开课:ISSCC 2022-高速/高性能数据转换器系列2(Dr. Gabriele Manganaro)

16、免费公开课:ISSCC 2022-高速/高性能数据转换器系列3(Prof. Pieter Harpe)

17、免费公开课:ISSCC 2022-高速/高性能数据转换器系列4(Prof. Nan Sun)

点击下方“公众号”,关注更多精彩

半导体人才招聘服务平台